4

to

СП

vj

01

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для отображения линейной шкалы на экране электронно-лучевой трубки | 1983 |

|

SU1327089A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Изобретение относится к вычис10 лительной технике и технике связи. Его использование в системах цифрового радиовещания и звукозаписи позволяет расширить функциональные возможности за счет обеспечения перемещения символов. Цифровой компандер содержит блоки 5, 6 оперативной памяти, блок 7 вьгоода и блок 3 управления. Благодаря введению анализатора 1 старших разрядов, формирователя 2 порядка мантиссы и формирователя 4 адресов обеспечивается одновременное перемежение и сжатие информации.-- 5 з.п. ф-лы, 5 ил.

п

Фиг. 1

Изобретение относится к вычисли- ,фельной технике и технике связи и ожет быть использовано в системах .цифрового радиовещания и звукозаписи,

Цель изобретения - повышение помехозащищенности формируемого кода за. счет обеспечения перемещения символов.

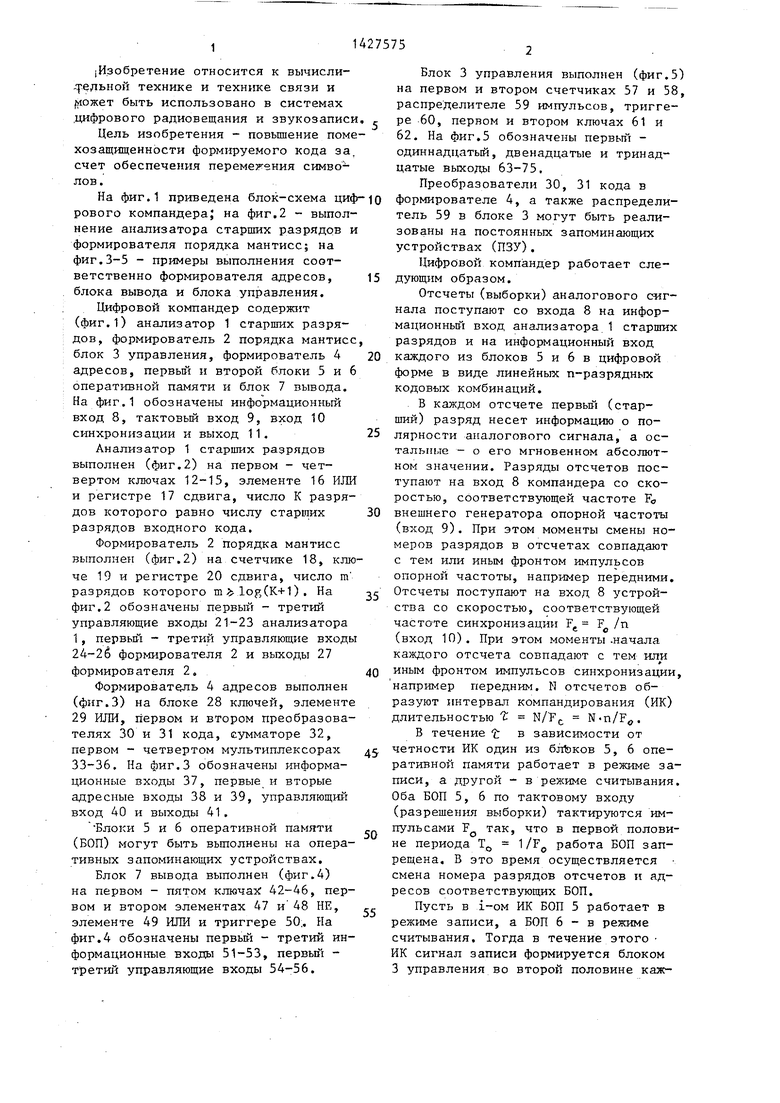

На фиг.1 приведена блок-схема циф-ю формирователе 4, а также распределирового компандера; на фиг,2 - выполнение анализатора старших разрядов и формирователя порядка мантисс; на фиг,3-5 - примеры выполнения соответственно формирователя адресов, блока вывода и блока управления.

Цифровой компандер содержит (фиг.1) анализатор 1 старпшх разрядов, формирователь 2 порядка мантисс, блок 3 управления, формирователь 4 адресов, первьп и второй блоки 5 и 6 оперативной памяти и блок 7 вывода. На фиг.1 обозначены информационный вход 8, тактовый вход 9, вход 10 синхронизации и выход 11.

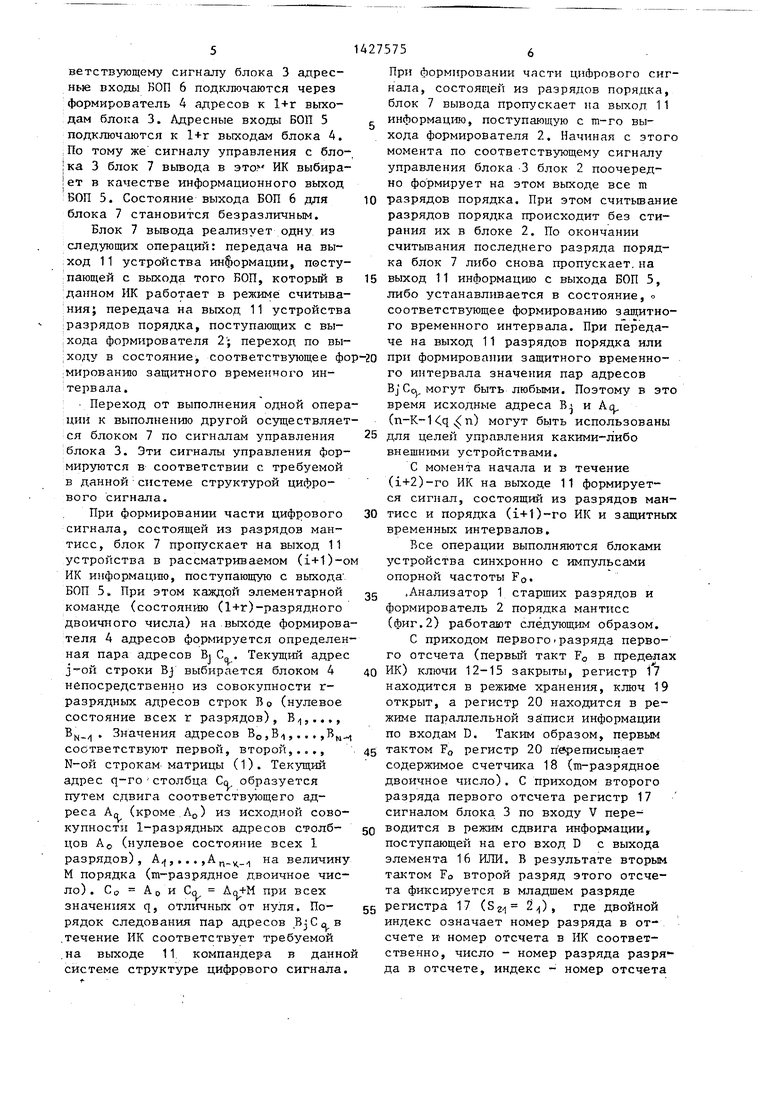

Анализатор 1 старших разрядов выполнен (фиг,2) на первом - четвертом ключах 12-15, элементе 16 ИЛИ и регистре 17 сдвига, число К разрядов которого равно числу старших разрядов входного кода.

Формирователь 2 порядка мантисс выполнен (фиг.2) на счетчике 18, ключе 19 и регистре 20 сдвига, число т разрядов которого (K-bl), На фиг,2 обозначены первый - третий управляющие входы 21-23 анализатора 1, первый - третий управляющие входы 24-2ё формирователя 2 и выходы 27 формирователя 2.

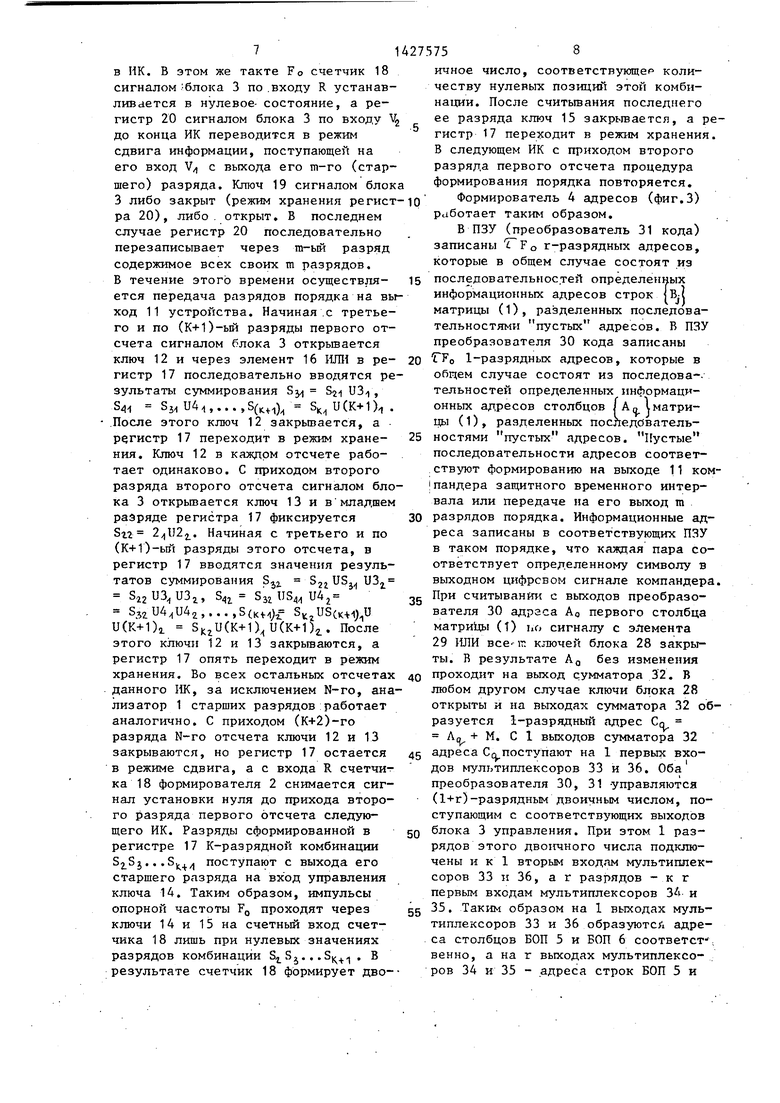

Формирователь 4 адресов выполнен (фиг.З) на блоке 28 ключей, элементе 29 ИЛИ, первом и втором преобразователях 30 и 31 кода, сумматоре 32, первом - четвертом мультиплексорах 33-36, На фиг.З обозначены информационные входы 37, первые и вторые адресные входы 38 и 39, управляющий вход 40 и выходы 41,

Блоки 5 и 6 оперативной пам;гги (БОП) могут быть вьшолнены на оперативных запоминающих устройствах.

Блок 7 вывода выполнен (фиг.4) на первом - пятом ключах 42-46, первом и втором элементах 47 и 48 НЕ, элементе 49 ИЛИ и триггере 50;, На фиг,4 обозначены первый - третий информационные входы 51-53, первьш - третий управляющие входы 54-56,

15

20

25

30

35

40

4S

50

55

таль 59 в блоке 3 могут быть реализованы на постоянных запоминающих устройствах (ПЗУ),

Цифровой компандер работает следующим образом.

Отсчеты (выборки) аналогового сигнала поступают со входа 8 на информационный вход анализатора.1 старших разрядов и на информационный вход каждого из блоков 5 и 6 в цифровой форме в виде линейных п-разрядных кодовых комбинаций,

В каждом отсчете первьп (старший) разряд несет информацию о полярности аналогового сигнала, а остальные - о его мгновенном абсолютном значении. Разряды отсчетов поступают на вход 8 компандера со скоростью, соответствующей частоте F, внешнего генератора опорной частоты (вход 9). При этом моменты смены номеров разрядов в отсчетах совпадают с тем или иным фронтом импульсов опорной частоты, например передними. Отсчеты поступают на вход 8 устройства со скоростью, соответствующей частоте синхронизации F F /n (вход 10). При этом моменты .начала каждого отсчета совпадают с тем или иным фронтом импульсов синхронизации, например передним. N отсчетов образуют интервал компандирования (ИК) длительностью I N/F N-n/F,,.

В течение t в зависимости от четности ИК один из ботЬков 5, 6 оперативной памяти работает в режиме записи, а другой - в режиме считывания. Оба БОП 5, 6 по тактовому входу (разрешения выборки) тактируются импульсами Fg так, что в первой половине периода Т 1/F работа БОП запрещена, В это время осуществляется смена номера разрядов отсчетов и адресов соответствующих БОП,

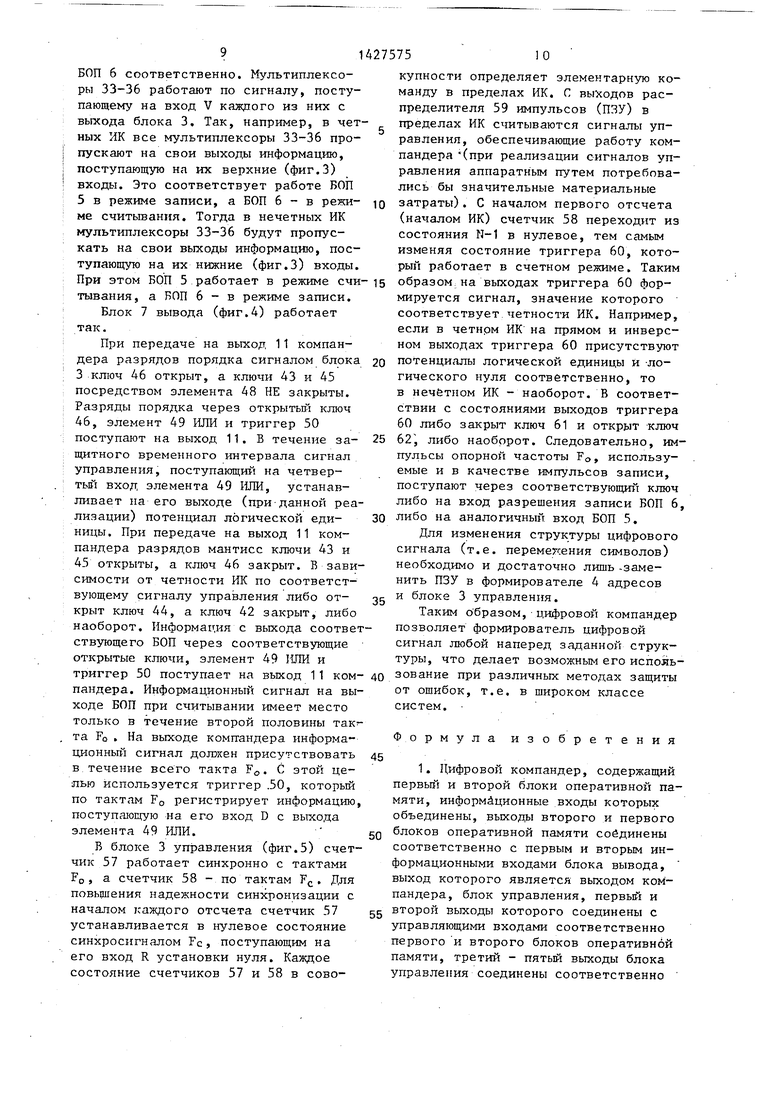

Пусть в i-oM ИК БОП 5 работает в режиме записи, а БОП 6 - в режиме считывания. Тогда в течение этого ИК сигнал записи формируется блоком 3 управления во второй половине кажБлок 3 управления выполнен (фиг.5) на первом и втором счетчиках 57 и 58, распределителе 59 импульсов, триггере 60, первом и втором ключах 61 и 62. На фиг,5 обозначены первьш - одиннадцатый, двенадцатые и тринадцатые выходы 63-75,

Преобразователи 30, 31 кода в

5

0

5

0

5

0

S

0

5

таль 59 в блоке 3 могут быть реализованы на постоянных запоминающих устройствах (ПЗУ),

Цифровой компандер работает следующим образом.

Отсчеты (выборки) аналогового сигнала поступают со входа 8 на информационный вход анализатора.1 старших разрядов и на информационный вход каждого из блоков 5 и 6 в цифровой форме в виде линейных п-разрядных кодовых комбинаций,

В каждом отсчете первьп (старший) разряд несет информацию о полярности аналогового сигнала, а остальные - о его мгновенном абсолютном значении. Разряды отсчетов поступают на вход 8 компандера со скоростью, соответствующей частоте F, внешнего генератора опорной частоты (вход 9). При этом моменты смены номеров разрядов в отсчетах совпадают с тем или иным фронтом импульсов опорной частоты, например передними. Отсчеты поступают на вход 8 устройства со скоростью, соответствующей частоте синхронизации F F /n (вход 10). При этом моменты .начала каждого отсчета совпадают с тем или иным фронтом импульсов синхронизации, например передним. N отсчетов образуют интервал компандирования (ИК) длительностью I N/F N-n/F,,.

В течение t в зависимости от четности ИК один из ботЬков 5, 6 оперативной памяти работает в режиме записи, а другой - в режиме считывания. Оба БОП 5, 6 по тактовому входу (разрешения выборки) тактируются импульсами Fg так, что в первой половине периода Т 1/F работа БОП запрещена, В это время осуществляется смена номера разрядов отсчетов и адресов соответствующих БОП,

Пусть в i-oM ИК БОП 5 работает в режиме записи, а БОП 6 - в режиме считывания. Тогда в течение этого ИК сигнал записи формируется блоком 3 управления во второй половине каждого такта То по тактопому входу (разрешения записи) НОП 5, п сигнал сч1.тыван 1я - по аналогичному входу БОП 6. Отсчеты г-го ИК ндкаплитзаются в БОП 5 в виде матрицы размером Nxn:

1l2i3l...KT(K+1)T ...п, ...Кг() ...п

,, .Кц(К+1 )

где 1, 2, 3, ..., К, ..., п - номера разрядов отсчета, а индексы - номера отсчетов в ИК. С этой целью блок 3 15 управления последовательно и синхрон- |Но с частотами FQ и F формирует 1-разрядные адреса столбцов и г-раз- рядные адреса строк соответственно. Эти адреса через формирователь 4 пос- 20 тупают на соответствующие адресные входы БОП 5. Как видно из матрицы (1), :1-разрядное двоичное число последова- тельно по тактам FO проходит все состояния от нулевого до состояния, со- 25 ответствующего п. Оттуда же г-разряд- ное двоичное число последовательно и синхронно с FC проходит все состояния от нулевого до состояния, соответствующего N. Так как FC РО/П, ЗО то каждое изменение состояния г-раз- рядного двоичного числа происходит в момент перехода 1-разрядного двоичного числа из п-го состояния в нулевое. Таким образом каждое состояние с (1+г)-разрядного двоичного числа определяет элементарную команду (шаг) в пределах каждого данного ИК. Это двоичное число используется для управления формирователем 4 адресов, 40 который в рассматриваемом i-ом. ИК формирует адреса строк и столбцов для БОП 6.

Одновременно с формированием в 5 БОП 5 матрицы (1) анализатор 1 старших разрядов определяет номер /и самого старшего из К старших разрядов, следующих сразу после первого (знакового)., значение которого отлично от 50 нуля хотя бы в одном из N отсчетов данного НК, Осуществляется это путем формирования блоком 1 по сигналам блока 3 К-разрядной комбинации .. .8 , где индексы означают 55 номера К анализируемых старших разрядов отсчетов, следующих сразу после первого (знакового). Значение каждого разряда этой комбинации опрелеляется в результате N операщш логического cy fмиpoвaния

Si 2, U2tU...U2,, Sj ВгиЗ,и32.и...иЗн ,

(2)

10

15 20 ), 25 ЗОс ) 40

5 т 50 55 SMI SKU(K+I) п(к+1)2и...и(к-и)н StUS,.u..., ...ик„и(к+1),и

U(K+1)U...(K+1) ,

где 2,3,...,(К+1) - номера К старших разрядов отсчетов, а индексы при них - номера отсчетов п ИК.

Из (2) видноj что К-разрядная комбинация S Sj . .. Sy. в общем случае состоит из двух непрерывных последовательностей: нулевой StSj.. и единичной S;u...Sn . Количество нулей в нулевой последовательности соответствует числу X старших разрядов, следующих сразу после первого и на протяжении данного ИК (во всех отсчетах данного ИК) сохраняющих нулевые значения. Эти разряды в мантиссы не входят (отбрасываются ). Тогда количество единиц в единичной последовательности соответствует числу Y К-Х отбрасьшаемых в данном ИК младших разрядов отсчетов,

После анализа блоком 1 (К+1)-го разряда N-ro отсчета и по сигналу блока 3 управления комбинация S;jSj...S попазрядно поступает с выхода анализатора 1 на информационный йход формироватедя 2, который по сигналу блока 3 и в соответствии с числом X формирует т-разрядное ((K+1)) двоичное число. Последнее представляет собой порядок мантисс данного ИК в двоичном представлении чисел с плавающей запятой. Порядок определяет число- отбрасьтае- мых старших разрядов отсчетов, следующих сразу после первого. Порядок определяет номер разряда в отсчетах, после которого следуют вторые старшие разряды соответствующих мантисс. Первым старшим разрядом мантисс является первый (знаковый) разряд отсчетов.

С началом следующего (i+l)-ro ИК т-разрядное двоичное число переписывается на выходы формирователя 2 по соответствующему сигналу блока 3. Одновременно с этим БОП 5 переходит в режим считывания, а БОП 6 - в режим записи. Кроме того, по соответствующе гу сигналу блока 3 адресные входы ВОП 6 подключаются через формирователь 4 адресов к 1+г выходам блока 3. Адресные входы БОН 5 подключаются к 1+г выходам блока 4. :По тому же сигналу управления с блоI ка 3 блок 7 вьшода в ИК выбира- ет в качестве информационного выход БОП 5. Состояние выхода БОП 6 для блока 7 становится безразличным.

Блок 7 вьгеода реализует одну из следующих операций: передача на выход 11 устройства информации, поступающей с выхода того БОП, который в Сданном ИК работает в режиме считывания; передача на выход 11 устройства :разрядов порядка, поступающих с вы- :хода формирователя 2; переход по выходу в состояние, соответствующее фор-20 при формировании защитного временномированию защитного временного ин- тервала.

; Переход от выполнения одной операции к выполнению другой осуществляется блоком 7 по сигналам управления блока 3. Эти сигналы управления формируются в соответствии с требуемой в данной системе структурой цифрового сигнала.

При формировании части цифрового сигнала, состоящей из разрядов мантисс, блок 7 пропускает на выход 11 устройства в рассматриваемом (1+1)-ом ИК информацию, поступающую с выхода БОП 5. При этом каждой элементарной команде (состоянию (1+г)-разрядного двоичного числа) на выходе формирователя 4 адресов формируется определенная пара адресов BjCg. Текущий адрес j- oi i строки Bj выбирается блоком 4 непосредственно из совокупности г- разрядных адресов строк Во (нулевое состояние всех г разрядов), В;,,..., В| . Значения адресов Во,В,.. . ,В соответствуют первой, второй,..,, N-ой строкам матрицы (1). Текущий адрес q-roстолбца Со образуется путем сдвига соответствующего адреса АО (кроме АО) из исходной совокупности 1-разрядных адресов столбцов АО (нулевое состояние всех 1 разрядов), А, ... ,Аг1-х на величину М порядка (т-разрядное двоичное число) . Со АО и Со AQ+M при всех значениях q, отличных от нуля. рядок следования пар адресов .течение ИК соответствует требуемой .на выходе 11 компандера в данно системе структуре цифрового сигнала.

По- .

При формировании части цифрового сигнала, состоящей из разрядов порядка, блок 7 вывода пропускает на выход 11

информацию, поступающую с т-го выхода формирователя 2, Начиная с этого момента по соответствующему сигналу управления блока -3 блок 2 поочередно формирует на этом выходе все m

разрядов порядка. При этом считывание разрядов порядка происходит без стирания их в блоке 2. По окончании считьшания последнего разряда порядка блок 7 либо снова пропускает, на

выход 11 информацию с выхода БОП 5, либо устанавливается в состояние, о соответствующее формированию защитного временного интервала. При передаче на выход 11 разрядов порядка или

го интервала значения пар адресов BjCc могут быть любыми. Поэтому в это время исходные адреса В и Ас (n-K-1 q n) могут быть использованы

для целей управления какими-либо внешними устройствс1ми.

С момента начала и в течение (i+2)-ro ИК на выходе 11 формируется сигнал, состоящий из разрядов мантисе и порядка (i+l)-ro ИК и защитных временных интервалов.

Все операции выполняются блоками устройства синхронно с импульсами опорной частоты FQ.

.Анализатор 1 старщих разрядов и формирователь 2 порядка мантисс (фиг.2) работают следующим образом,

С приходом первогорразряда первого отсчета (первьй такт FO в пределах

ИК) ключи 12-15 закрыты, регистр 17 находится в режиме хранения, ключ 19 открыт, а регистр 20 находится в режиме параллельной за:писи информации по входам D. Таким образом, первым

тактом регистр 20 п вреписывает содержимое счетчика 18 (т-разрядное двоичное число). С приходом второго разряда первого отсчета регистр 17 сигналом блока 3 по входу V переводится в режим сдвига информации, поступающей на его вход D с выхода элемента 16 РШИ. В результате вторым тактом FO второй разряд этого отсчета фиксируется в младщем разряде

регистра 17 (8г-1 2), где двойной индекс означает номер разряда в отсчете и номер отсчета в ИК соответственно, число - номер разряда разряда в отсчете, индекс - номер отсчета

в НК. В этом же такте FO счетчик 18 сигналом блока 3 по .входу R устанавливается в нулевое- состояние, а регистр 20 сигналом блока 3 по входу до конца ИК переводится в режим сдвига информации, поступающей на его вход V с выхода его т-го (старшего) разряда. Ключ 19 сигналом блока 3 либо закрыт (режим хранения регистра 20), либо, открыт, В последнем случае регистр 20 последовательно перезаписывает через га-ый разряд содержимое всех своих m разрядов. В течение этого времени осуществил- ется передача разрядов порядка на выход 11 устройства. Начиная .с третьего и по (К+1)-ый разряды первого отсчета сигналом блока 3 открьшается ключ 12 и через элемент 16 ИЛИ в ре- гистр 17 последовательно вводятся результаты суммирования S 821 U3i, Sj U4i,...,S(,)/ (K+I). .После этого ключ 12 закрьгоается, а

регистр 17 переходит в режим хранения. Ключ 12 в каждом отсчете работает одинаково. С приходом второго разряда второго отсчета сигналом блока 3 открьгоается ключ 13 и в младшем разряде регистра 17 фиксируется Згг . Начиная с третьего и по (К+Т)-ьп1 разряды этого отсчета, в регистр 17 вводятся значения результатов суммирования S

J2.

из

S22U3, U3i, SjiUS U4,

5зги4 и4гS(K.) Sv,.()U

U(K+1)i (К+1)и(К+1)г. После этого ключи 12 и 13 закрываются, а регистр 17 опять переходит в режим хранения. Во всех остальных отсчетах данного IIK, за исключением N-ro, анализатор 1 старших разрядов:работает аналогично. С приходом (К+2)-го разряда N-ro отсчета ключи 12 и 13 закрываются, но регистр 17 остается в режиме сдвига, а с входа R счетчит ка 18 формирователя 2 снимается сигнал установки нуля до прихода второго разряда первого отсчета следующего ИК. Разряды сформированной в регистре 17 К-разрядной комбинации ...S поступают с выхода его старшего разряда на вход управления ключа 14. Таким образом, импульсы опорной частоты Р проходят через ключи 14 и 15 на счетный вход счетчика 18 лишь при нулевых значениях разрядов комбинации S.j Sj. . .5 . В результате счетчик 18 формирует дво5 0

5

0

5

0

ичное число, соответствующер количеству нулевых позиций этой комбинатами. После считьгаания последнего ее разряда ключ 15 закрьгеается, а регистр 17 переходит в режим хранения. В следующем ИК с приходом второго разряда первого отсчета процедура формирования порядка повторяется.

Формирователь 4 адресов (фиг.З) работает таким образом.

В ПЗУ (преобразователь 31 кода) записаны f о г-разрядных адресов, которые в общем случае состоят из последовательностей определенных информационных адресов строк |В|{ матрицы (1), разделенных последовательностями пустых адресов. В ПЗУ преобразователя 30 кода записаны TFo 1-разрядных адресов, которые в общем случае состоят из последова-. тельностей определенных информационных адресов столбцов |Ао 1матри- цы (1), разделенных последовательностями пустых адресов. Пустые последовательности адресов соответствуют формированию на выходе 11 ком- |пандера защитного временного интервала или передаче на его выход m разрядов порядка. Информационные адреса записаны в соответствующих ПЗУ в таком порядке, что каждая пара соответствует определенному символу в выходном цифровом сигнале компандера. При считывание с выходов преобразователя 30 адргса АО первого столбца матри15)1 (t) ьо сигналу с элемента 29 ИЛИ все гс ключей блока 28 закрыты. В результате Ад без изменения проходит на выход сумматора 32. В любом другом случае ключи блока 28 открыты и на выходах сумматора 32 образуется 1-разрядный адрес Сп А„ + М. С 1 выходов сзгмматора 32

5 адреса Сл поступают на 1 первых входов кгультиплексоров 33 и 36. Оба преобразователя 30, 31 управляются (1+г)-разрядным двоичным числом, поступающим с соответствующих выходов

0 блока 3 управления. При этом 1 разрядов этого двоичного числа подключены и к 1 вторым входам мультиплексоров 33 и 36, а г разрядов - к г первым входам мультиплексоров 34 и

5 35. Таким образом на 1 выходах мультиплексоров 33 и 36 образуются адреса столбцов БОП 5 и БОП 6 соответст ; венно, а на г выходах мультиплексоров 34 и 35 - адреса строк БОП 5 и

9

БОП 6 соответственно. Мультиплексоры 33-36 работают по сигналу, поступающему на вход V каждого из них с выхода блока 3. Так, например, в четных ИК все мультиплексоры 33-36 пропускают на свои выходы информацию, поступающую на их верхние (фиг.З) входы. Это соответствует работе БОП 5 в режиме записи, а БОП 6 - в реки- ме считывания. Тогда в нечетных ИК мультиплексоры 33-36 будут пропускать на свои вьпсоды информацию, поступающую на их нижние (фиг.З) входы

При этом БОП 5 работает в режиме счи-is образом на выходах триггера 60 фортывания, а БОП 6 - в режиме записи.

Блок 7 вывода (фиг.4) работает Tajc.

При передаче на выход 11 компандера разрядов порядка сигналом блока 3 ключ 46 открыт, а ключи 43 и 45 посредством элемента 48 НЕ закрыты. Разряды порядка через открытый ключ 46, элемент 49 ИЛИ и триггер 50 поступают на выход 11. В течение защитного временного интервала сигнал управления, поступающий на четвертый вход элемента 49 ИЛИ, устанавливает на его выходе (при-данной реализации) потенциал логической единицы. При передаче на выход 11 компандера разрядов мантисс ключи 43 и 45 открыты, а ключ 46 закрыт. В зависимости от четности ИК по соответствующему сигналу управления либо открыт ключ 44, а ключ 42 закрыт, либо наоборот. Информация с выхода соответ ствзпощего БОП через соответствующие

Таким о бразом, цифровой компандер позволяет формирователь цифровой сигнал любой наперед заданной структуры, что делает возможным его испоньоткрытые ключи, элемент 49 1ШИ и

триггер 50 поступает на выход 11 ком- 40 зование при различных методах защиты

пандера. Информационный сигнал на вы- от ошибок, т.е. в широком классе

ходе БОП при считывании имеет место только в течение второй половины такта FO . На выходе компандера информационный сигнал должен присутствовать в,течение всего такта F. С этой целью используется триггер .50, который по тактам FO регистрирует информацию поступающую на его вход D с выхода элемента 49 ИЛИ.

Б блоке 3 управления (фиг.5) счетчик 57 работает синхронно с тактами FO , а счетчик 58 - по тактам Fj, . Для повьщгения надежности синхронизации с началом каждого отсчета счетчик 57 устанавливается в нулевое состояние синхросигналом FC, поступающим на его вход R установки нуля. Каждое состояние счетчиков 57 и 58 в сово5

10

купности определяет элементарную команду в пределах ИК. С выходов распределителя 59 импульсов (ПЗУ) в пределах ИК считываются сигналы управления, обеспечивающие работу компандера (при реализации сигналов управления аппаратным путем потребовались бы значительные материальные затраты). С началом первого отсчета (началом ИК) счетчик 58 переходит из состояния N-1 в нулевое, тем самым изменяя состояние триггера 60, который работает в счетном режиме. Таким

мируется сигнал, значение которого соответствует четности ИК. Например, если в четнрм ИК на прямом и инверсном выходах триггера 60 присутствуют

потенциалы логической единицы и -логического нуля соответственно, то в нечётном ИК - наоборот. В соответствии с состояниями выходов триггера 60 либо закрыт ключ 61 и открыт ключ

62, либо наоборот. Следовательно, импульсы опорной частоты FO, используемые и в качестве импульсов записи, поступают через соответствующий ключ либо на вход разрешения записи БОП 6,

либо на аналогичный вход БОП 5.

Для изменения структуры цифрового сигнала (т.е. переметсения символов) необходимо и достаточно лишь -заменить ПЗУ в формирователе 4 адресов

и блоке 3 управления.

Таким о бразом, цифровой компандер позволяет формирователь цифровой сигнал любой наперед заданной структуры, что делает возможным его испоньсистем.

Формула изобретения

с первым - третыда управляющими входами блока вывода, отличаю- щ и и с я тем,- что, с целью повышения помехозащ -щенности формируемого кода за счет обеспечения перемежения символов, в компандер введены формирователь порядка мантисс, формирователь адресов и анализатор старших разрядов, информационньш вход кото- рого объединен с информационным входом первого блока оперативной памяти и является информационным входом компандера, тактовьп вход анализатора старших разрядов объединен с такто- выми входами блоков оперативной памяти формирователя порядка мантисс, блока вывода и блока управления и является тактовым входом компандера, вход синхронизации блока управления является входом синхронизации компандера, выход анализатора старших разрядов соединен с информационным входом формирователя порядка мантисс, выходы которого, кроме последнего, подключены к соответствующим информационным входам формирователя адресов, управляющий вход которого подключен к пятому выходу блоки управления, шестой - одиннадцатьи выходы которого соединены соответственно с первым - третьим управляющими входам анализатора старших разрядов и первым - третьим управляющими входами формирователя порядка мантисс, пос- ледний выход которого подключен к соответствующему информационному входу формирователя адресов к третьему информационному входу блока вьгоода, двенадцатые и тринадцатые выходы блока управления подключены соответственно к первым и вторым адресным входам формирователя адресов, первые - четвертые выходы которого соединены соответственно с первыми и вторыми адресными входами первого и второго блоков оперативной памяти. 2. Компандер по п.1, отличающийся тем, что анализатор старших разрядов выполнен на ключах, регистре сдвига и элементе ИЛИ, первый вход которого является информационным входом анализатора, выход элемента ИЛИ соединен с информационным входом регистра сдвига, выход первого разряда которого соединен с управляющим входом первого ключа, выход К-го разряда регистра сдвига (к - число старших разрядов входного

5 0 5 О к 0 5 0 5

кода) соединен с управляющими входами второго и третьего ключей, информационные входы первого и второго ключпй являются соответственно первым и вторым управляющими входами анализатора, информационньп вход третьего ключа объединен с тактовым входом регистра сдвига и является тактовьм входом анализатора, выходы первого, второго и третьего ключей соединены соответственно со вторым и третьим входами элемента 1ШИ и информационным входом четвертого ключа, управляющий вход которого объединен с управляющим входом регистра сдвига и является третьим управляющим входом анализатора, выход четвертого ключа является выходом анализатора,

4,Компандер по п,1, отличающийся тем, что формирователь адресов выполнен на первом и втором преобразователях кода, су 1маторе, элементе ИШ, первом - четвертой мультиплексорах и блоке ключей, информационные входы которого являются информационными входами формирователя, выходы блока ключей соединены с первыми входами сумматора, выходы которого подключены к первым информационным входам первого и четвертого мультиплексоров, вторые информационные входы которых объединены с соответствующими первыми входами преобразователей кода и являются первыми адресными входами формирователя, вьп- ходы первого преобразователя кода

13

соединены с вторыми входами сумматора и входами элемента ИЛИ, выход которого соединен с управляющим входом блока ключей, вторые входы преобразователей кода объединены с первыми 1|нформационными входами второго и третьего мультиплексоров и являются фторыми адресными входами формирователя, выходы второго преобразова теля кода соединены с вторыми информационными входами второго и .третьего мультиплексоров, управляющие вхо- р,ы всех мультиплексоров объединены и Являются управляющим входом формирователя, выходы первого - четвертого мультиплексоров являются соответст- первыми - четвертыми выходами

:венно

формирователя.

п. 1, о т л и - тем, что блок вы:вода выполнен на первом - пятом ключах, первом и втором элементах НЕ, элементе ИЛИ и триггере, тактовый вход которого является тактовым входом блока, зьпсод первого элемента НЕ соединен с управляющим входом .первого ключа, выход которого соединен с информационным входом второго ключа, выход третьего ключа сое динен с информационным входом четвертого ключа, выход второго элемента НЕ соединен с управляющими входам второго и четвертого ключей, выходы которых и выход пятого ключа подключены к первому - третьему входам элемента , выход которого соединен с информационным входом триггера информационные входы первого, третьего и пятого ключей являются соответственно первым - третьим информационными входами блока, вход второго

Q

42757514

элемента НЕ объединен с управляющим входом пятого ключа и является первым управляющим входом блока, четвертый вход элемента ИЛИ является вторым управляющим входом блока, вход первого элемента НЕ объединен с управляющим входом третьего ключа и является третьим управляющим входом блока, выход триггера является выходом блока.

6, Компандер поп.1,отлича- тем, что блок управле15

20

зо

ю щ и и с я

ния выполнен на первом и втором счетчиках, распределителе импульсов, триггере и первом и втором ключах, информационные входы которых объединены со счетным входом первого счетчика и являются тактовым входом блока, вход обнуления первого счетчика объединен со счетным входом второго счетчика и является входом синхронизации блока, выход переполнения второго счетчика подключен к тактово- 25 му входу триггера, инверсный выход которого соединен с его информационным входом и управляющим входом второго ключа, выходы первого и второго ключей и первьп и второй выходы распределителя импульсов являются соответственно первым - четвертым выходами блока, прямой выход триггера соединен с управляющим входом первого ключа и является пятым выходом блока, третий - восьмой выходы распределителя импульсов являются соответственно шестым - .одиннадцатым выходами блока, выходы первого и второго счетчиков подключены соответственно к - первым и вторым входам распределителя импульсов и являются двенадцатыми и тринадцатыми выходами блока.

35

40

25 26

Г

./

.2

Фиг.З

| Патент США N 4467315, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-30—Публикация

1986-08-15—Подача