ел ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Устройство декодирования тональных сигналов | 1985 |

|

SU1277433A2 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Цифровой синтезатор частотно-модулированных сигналов | 1988 |

|

SU1552345A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

Изобретение относится к радиосвязи. Цель изобретения - повышение помехоустойчивости с одновременным увеличением числа декодируемых частот. Устройство содержит фильтр 1, компаратор 2, делитель 3 частоты, счетчики 4, 5 и 6, блок 7 вычисления кода длительности входного сигнала, коммутаторы 8 и 9, блок 10 постоянной памяти, блок 11 оперативной памяти, эл-т 12 задержки, регистр 13, дешифратор 14, сумматор 15, блок 16 сравнения двоичных кодов, распределитель 17, эл-ты И 18 и 19 и эл-ты ИЛИ 20 и 21. В данном устройстве процесс декодирования сигнала сводится к вычислению по поступлении фронта входного сигнала кодов длительности его периодов и сравнении этих кодов с допустимыми значениями, хранящимися в блоке 10 постоянной памяти. Данные этого блока путем обеспечения их изменения позволяют выбирать оптимальные х-ки устройства. Так как в данном устройстве распознавание принимаемой частоты производится сразу, то это сокращает время обработки и расширяет диапазон обрабатываемых частот. Устройство по п. 2 формулы отличается выполнением блока 7 вычисления. 1 з.п. ф-лы, 3 ил.

со

4

ратор 2, делитель 3 частоты, счетчики 4, 5 и 6, блок 7 вычисления кода длительности входного сигнала, коммутаторы 8 и 9, блок 10 постоянной памяти блок 11 оперативной памяти, эл-т 12 задержки, регистр 13, дешифратор 14, сумматор 15, блок 16 сравнения двоичных кодов, распределитель 17, эл-ты И 18 и 19 и эл-ты ИЛИ 20 и 21. В дан- Ном устройстве процесс декодирования сигнала сводится к вычислению по поступлении фронта входного сигнала кодов длительности его периодов и срав

Изобретение относится к радиосвязи и может быть использовано для приема Тональных сигналов ряда заданных частот, в частности для приема данныхэ Передаваемых последовательным частотным кодом.

Цель изобретения - повышение поме- хоустойчивости с одновременным увеличением числа декодируемых частот.

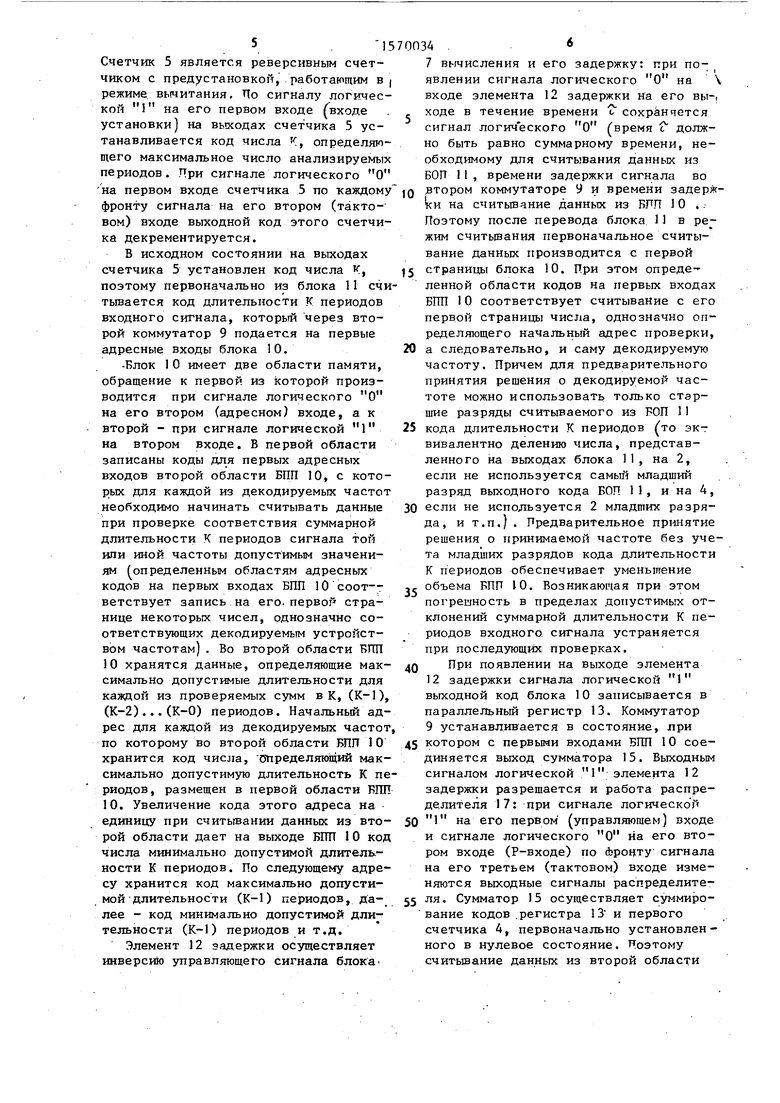

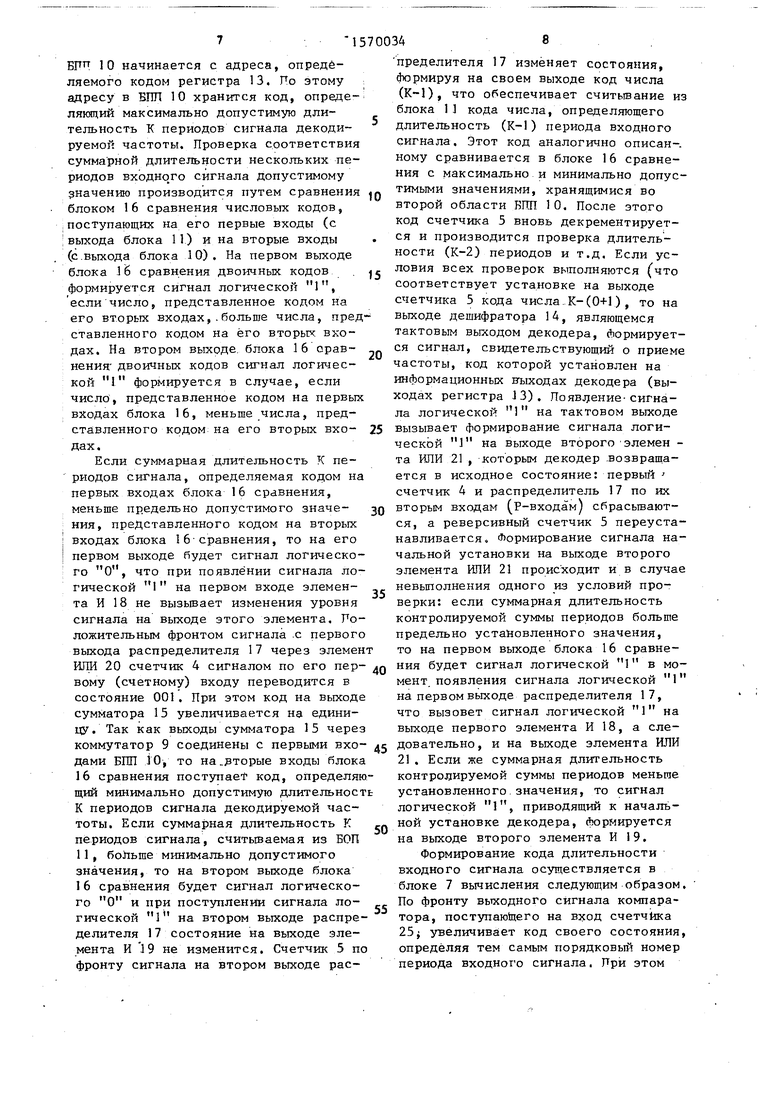

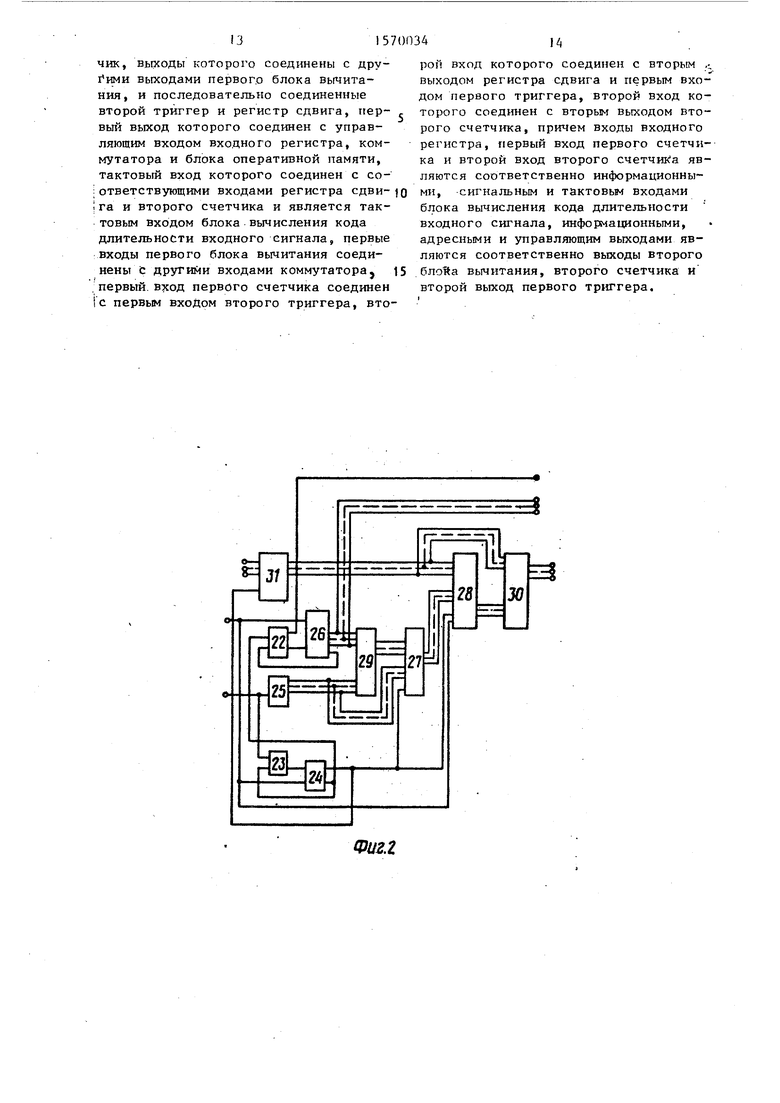

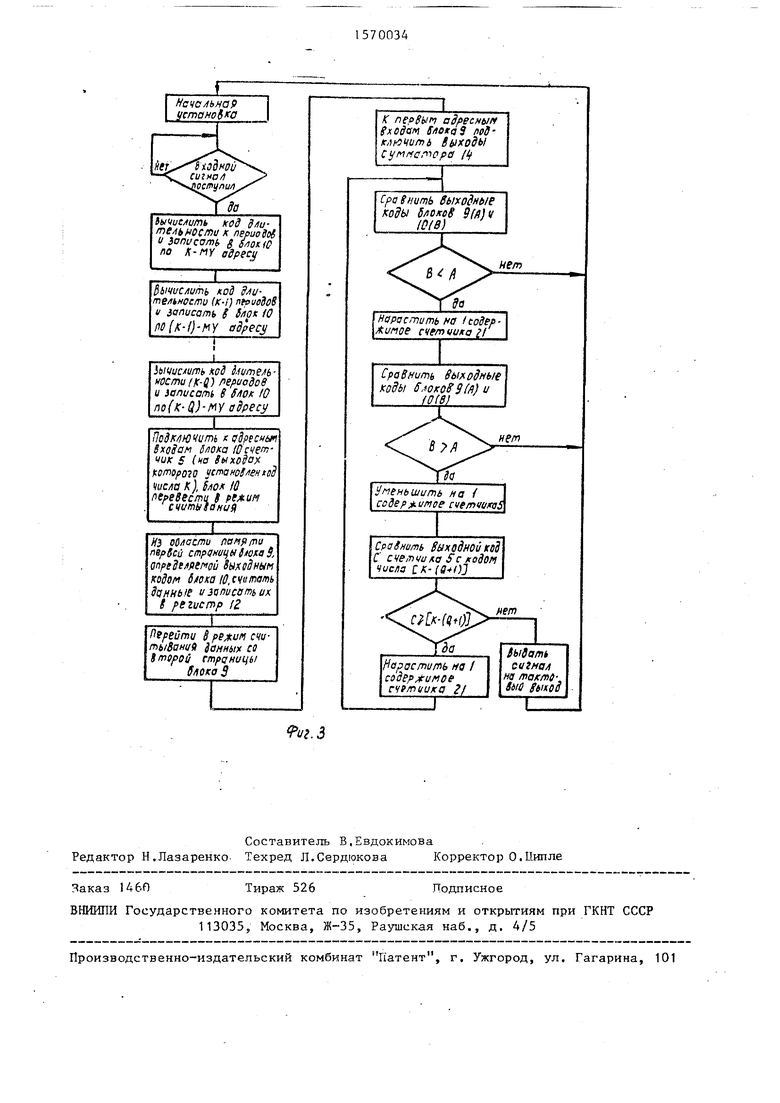

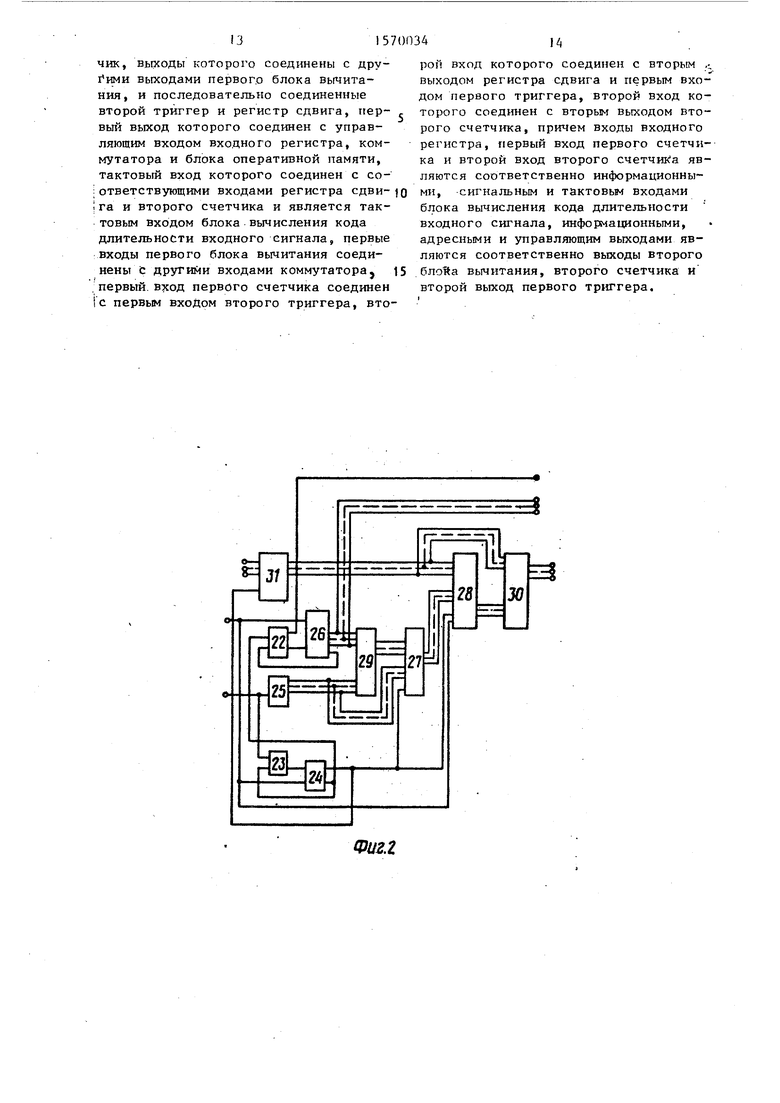

Uа фиг. 1 приведена структурная :уема устройства декодирования тональных частот; на йшг. 2 - структурная схема блока вычисления кода длительности входного сигнала; на Лиг. 3 - алгоритм работы декодера тональных: сигналов.

Устройство декодирования тональных сигналов содержит входной Аильтр 1, компаратор 2, делитель 3 частоты, первый 4, второй 5 и трети 6 счетчики, блок 7 вычисления кода длитель

ности входного сигнала, первый 8 и второй 9 коммутаторы, блок 10 постоянной памяти (БШТ) , блок II оперативной памяти БОП, элемент 12 задержки, выходной регистр 13, дешифратор 14, сумматор 15, блок 16 сравнения двоич ных кодов, распределитель 17, первый 8 и второй 19 элементы И, первый 20 и второй 21 элементв ИЛИ. Блок 7 вычисления кода длительности входного сигнала содержит первый 22 и второй 23 триггеры, регистр 24 сдвига, первый 25 и второй 26 счетчики, коммутатор 27, блок 28 оперативной памяти (БОП), первый 29 и второй 30 блоки вычитания, входной регистр 31 ,

Устройство работает следующим образом .

Счетчик 6Э изменяя свое состояние с частотой выходного сиглала делите

нении этих кодов с допустимыми значениями, хранящимися в блоке 10 постоянной памяти. Данные этого блока путем обеспечения их изменения позволяют выбирать оптимальные х-ки устройства. Так как в данном устройстве распознавание принимаемой частоты производится сразу, то это сокращает время обработки и расширяет диапазон обрабатываемых частот. Устройство по п.2 Формулы отличается выполнением блока 7 вычисления. 1 з.п, , 3 ил.

0

5

0

5

0

0

5

ля 3 частоты, определяет текущее время. Входной синусоидальный сигнал, прошедший через входной Фильтр 1 , улучшающий соотношение сигнал/шум, преобразуется компаратором 2 в- прямоугольные импульсы, имеюетие частоту входного сигнала. По каждому фронту сигнала на выходе компаратора 2 в блоке 7 вычисления производится вычисление кода длительности К (К-1), (К-2)...(К-0) периодов входного сигнала путем вычисления разности кодов счетчика 6 в момент фиксации поступления текущего периода входного сигнала и кодов, которые имел счетчик 6 ранее, на К, (К-1), (К-2)...(К-0) периодов. Вычисленные таким образом коды длительности последовательно подаются на информационные входы блока 11, на адресные входы которого через первый коммутатор 8 с выхода блока 7 вычисления подаются коды, определяющие число периодов, для которых определена длительность. Сигналом логической 1 с управляющего выхода блока 7 блок 1i оперативной памяти переводится в режим записи (для записи информации в БОП И необходимо, чтобы на его первом входе был сигнал логического О). После записи кодов длительности К, (К-1)..,(К-0) периодов входного сигнала БОЛ 11 сигналом ло- гическогог 0 с управляющего выхода блока 7 вычисления переводится в режим считывания„ Адрес ячеек памяти БОП 11 при этом определяется счетчиком V55 так как первый коммутатор 8 при изменении сигнала на его управляющем входе устанавливается в состояние; при котором KJ его выходы поступают сигналы с выходов счетчика 5.

Счетчик 5 является реверсивным счетчиком с предустановкой, работающим в | режиме вычитания. По сигналу логической 1 на его первом входе (входе установки) на выходах счетчика 5 устанавливается код числа , определяющего максимальное число анализируемых периодов. При сигнале логического О на первом входе счетчика 5 по каждому фронту сигнала на его втором (тактовом) входе выходной код этого счетчика декрементируется.

В исходном состоянии на выходах счетчика 5 установлен код числа и, поэтому первоначально из блока 11 считывается код длительности К периодов входного сигнала, который через второй коммутатор 9 подается на первые адресные входы блока 10.

-Блок 10 имеет две области памяти, обращение к первой из которой производится при сигнале логического О на его втором (адресном) входе, а к второй - при сигнале логической 1 на втором входе. В первой области записаны коды для первых адресных входов второй области БПП 10, с которых для каждой из декодируемых частот необходимо начинать считывать данные при проверке соответствия суммарной длительности К периодов сигнала той или иной частоты допустимым значениям (определенным областям адресных кодов на первых входах БПП 10 соот- ветствует запись на его- первой странице некоторых чисел, однозначно соответствующих декодируемым устройством частотам). Во второй области БПП 10 хранятся данные, определяющие максимально допустимые длительности для каждой из проверяемых сумм в К,(К-1), (К-2)...(К-0) периодов. Начальный адрес для каждой из декодируемых частот по которому во второй области БПП 10 хранится код числа, определяющий максимально допустимую длительность К периодов, размещен в первой области БГШ 10. Увеличение кода этого адреса на единицу при считывании данных из второй области дает на выходе БПП 10 код числа минимально допустимой длительности К периодов. По следующему адресу хранится код максимально допустимой длительности (К-1) периодов, далее - код минимально допустимой длительности (К-1) периодов и т.д.

Элемент 12 задержки осуществляет инверсию управляющего сигнала блока

0

5

7 вычисления и его задержку: при появлении сигнала логического О на Ч входе элемента 12 задержки на его вы-, ходе в течение времени С сохраняется сигнал логического О (время Ј должно быть равно суммарному времени, необходимому для считывания данных из БОП 11, времени задержки сигнала во втором коммутаторе 9 и времени задержки на считывание данных из БПП 10 . Поэтому после перевода блока 11 в режим считывания первоначальное считывание данных производится с первой

5 страницы блока 10. При этом определенной области кодов на первых входах БПП 10 соответствует считывание с его первой страницы числа, однозначно определяющего начальный адрес проверки, а следовательно, и саму декодируемую частоту. Причем для предварительного принятия решения о декодируемой частоте можно использовать только старшие разряды считываемого из БОП 11 кода длительности К периодов (то эквивалентно делению числа, представленного на выходах блока 11, на 2, если не используется самый младший разряд выходного кода БОП 1 1, и на 4,

0 если не используется 2 младптих разряда, и т.п.). Предварительное принятие решения о принимаемой частоте без учета младших разрядов кода длительности К периодов обеспечивает уменьшение объема БПП Ю. Возникающая при этом погрешность в пределах допустимых отклонений суммарной длительности К периодов входного сигнала устраняется при последующих проверках.

При появлении на выходе элемента 12 задержки сигнала логической 1 выходной код блока 10 записывается в параллельный регистр 13. Коммутатор 9 устанавливается в состояние, лри

5 котором с первыми входами БПП 10 соединяется выход сумматора 15. Выходным сигналом логической 1 элемента 12 задержки разрешается и работа распределителя 17: при сигнале логической

0 1 на его первом (управляющем) входе и сигнале логического О на его втором входе (Р-входе) по Фронту сигнала на его третьем (тактовом) входе изменяются выходные сигналы распределите5 ля. Сумматор 15 осуществляет суммирование кодов регистра 13 и первого счетчика 4, первоначально установленного в нулевое состояние. поэтому считывание данных из второй области

5

0

БП™ 10 начинается с адреса, определяемого кодом регистра 13. По этому адресу в БПЛ 10 хранится код, определяющий максимально допустимую длительность К периодов сигнала декодируемой частоты. Проверка соответствия суммарной длительности нескольких периодов входно.го сигнала допустимому

пределителя 17 изменяет состояния Формируя на своем выходе код числ (К-1), что обеспечивает считывани блока 1 1 кода числа, определяющег длительность (К-1) периода входно сигнала. Этот код аналогично опис ному сравнивается в блоке 16 срав ния с максимально и минимально до

значению производится путем сравнения JQ тимыми значениями, хранящимися во

блоком 16 сравнения числовых кодов, поступающих на его первые входы (с выхода блока 11) и на вторые входы (с выхода блока 10). На первом выходе блока J 6 сравнения двоичных кодов формируется сигнал логической 1,

второй области БПП 1 0. После этог код счетчика 5 вновь декрементиру ся и производится проверка длитель ности (К-2) периодов и т.д. Если у ловия всех проверок выполняются (ч соответствует установке на выходе счетчика 5 кода числа К-(0+1), то выходе дешифратора 14, являющемся тактовым выходом декодера, Формиру

второй области БПП 1 0. После этого код счетчика 5 вновь декрементирует- ся и производится проверка длительности (К-2) периодов и т.д. Если ус- ловия всех проверок выполняются (что соответствует установке на выходе счетчика 5 кода числа К-(0+1), то на выходе дешифратора 14, являющемся тактовым выходом декодера, Формируетесли число, представленное кодом на его вторых входах, больше числа, представленного кодом на его вторых входах. На втором выходе блока 16 орав- 2д ся сигнал, свидетельствующий о приеме нения двоичных кодов сигнал логичес- частоты, код которой установлен на

кой 1 формируется в случае, если

информационных выходах декодера (выходах регистра 13). Появление-сигначисло, представленное кодом на первых входах блока 16, меньше числа, представленного кодом на его вторых вхо- 25 вызывает Формирование сигнала логила логической 1 на тактовом выходе

Дах.

Если суммарная длительность К периодов сигнала, определяемая кодом на первых входах блока 16 сравнения, меньше предельно допустимого значения, представленного кодом на вторых входах блока 16 сравнения, то на его первом выходе будет сигнал логическо- что при появлении сигнала лого

О,

гической 1 на первом входе элемен35

та И 18 не вызывает изменения уровня сигнала на выходе этого элемента. Положительным фронтом сигнала с первого выхода распределителя 17 через элемент ИЛИ 20 счетчик 4 сигналом по его пер- Q вому (счетному) входу переводится в состояние 001. При этом код на выходе

мент появления сигнала логической на первом выходе распределителя 17, что вызовет сигнал логической 1 на

сумматора 15 увеличивается на единицу. Так как выходы сумматора 15 через выходе первого элемента И 18, а сле- коммутатор 9 соединены с первыми вхо- 45 довательно, и на выходе элемента ИЛИ дами БПП 10, то на.вторые входы блока 21 . Если же суммарная длительность 16 сравнения поступает код, определяющий минимально допустимую длительность К периодов сигнала декодируемой часконтролируемои суммы периодов меньше установленного значения, то сигнал логической 1, приводящий к началь- тоты. Если суммарная длительность К -0 ной установке декодера, Формируется периодов сигнала, считываемая из БОП на выходе второго элемента И 19.

11, больше минимально допустимого значения, то на втором выходе блока 16 сравнения будет сигнал логического О и при поступлении сигнала логической 1 на втором выходе распределителя 17 состояние на выходе элемента И 9 не изменится. Счетчик 5 по фронту сигнала на втором выходе рас700348

пределителя 17 изменяет состояния, Формируя на своем выходе код числа (К-1), что обеспечивает считывание из блока 1 1 кода числа, определяющего длительность (К-1) периода входного сигнала. Этот код аналогично описанному сравнивается в блоке 16 сравнения с максимально и минимально допустимыми значениями, хранящимися во

второй области БПП 1 0. После этого код счетчика 5 вновь декрементирует- ся и производится проверка длительности (К-2) периодов и т.д. Если ус- ловия всех проверок выполняются (что соответствует установке на выходе счетчика 5 кода числа К-(0+1), то на выходе дешифратора 14, являющемся тактовым выходом декодера, Формируется сигнал, свидетельствующий о приеме частоты, код которой установлен на

информационных выходах декодера (выходах регистра 13). Появление-сигнавызывает Формирование сигнала логила логической 1 на тактовом выходе

ческой 1 на выходе второго элемен - та ИЛИ 21 , которым декодер возвращается в исходное состояние: первый счетчик 4 и распределитель 17 по их вторым входам (Р-входам) сбрасываются, а реверсивный счетчик 5 переустанавливается. Формирование сигнала начальной установки на выходе второго элемента ИЛИ 23 происходит и в случае невыполнения одного из условий проверки: если суммарная длительность контролируемой суммы периодов больше предельно установленного значения, то на первом выходе блока 16 сравнения будет сигнал логической 1

в моII 1 И

мент появления сигнала логической на первом выходе распределителя 17, что вызовет сигнал логической 1 на

выходе первого элемента И 18, а сле- довательно, и на выходе элемента ИЛИ 21 . Если же суммарная длительность

Формирование кода длительности входного сигнала осуществляется в блоке 7 вычисления следующим образом. По фронту выходного сигнала компаратора, поступающего на вход счетчика 25$ увеличивает код своего состояния, определяя тем самым порядковый номер периода входного сигнала. При этом

триггер 23 по тактовому входу устанавливается в нулевое состояние. Выход триггера 23 соединен с первым входом /Р-входом) регистра 24 сдвига, Поэтому по фронту сигнала, поступающего на тактовый вход регистра 24 сдвига, на его первом выходе (выходе первого разряда) устанавливается сигнал логическая 1, что обеспечивает запись в регистр 31 кода 0, установленного на информационных входах и характеризующего состояние счетчика 6 в момент прихода фронта входного сигнала. Сигналом логической 1 с первого выхода регистра.24 сдвига БОТ7 28 переводится в режим записи коммутатор 27 устанавливается в состояние, при котором к первым (адресным ) входам блока 28 оперативной па- мяти подключаются выходы первого счетчика 25. Это обеспечивает запись в БОП 28 по адресу, определяемому порядковым номером периода входного сигнала, выходного кода регистра 31, характеризующего текущее время прихода входного сигнала. По следующему фронту сигнала на тактовом входе сигнал логической 1 появляется на втором выходе регистра 24 сдвига, котогг рым триггер 22 переустанавливается, формируя на управляющем выходе сигнал логической 1 и разрешая работу второго (реверсивното.) счетчика 26. Этим же сигналом триггер 23 по второму входу (S-входу) устанавливается в единичное состояние, на выходах регистра 24 сдвига устанавливаются сигналы логического О, БОП 28 переводится в режим считывания, а к его адресным входам через коммутатор 27 подключаются выходы первого блока 29 вычитания. На выходах блока 29 вычитания Аорми- руется разность кодов двух чисел: вы- ходного кода счетчиков 25 и 26. На выходе первого счетчича 25 установлен код порядкового номера периода входного сигнала. В исходном состоянии на выходах второго счетчика 26 установ- хлен код числа К - максимального числа анализируемых периодов-. Поэтому на адресных входах БОП 28 формируется код номера периода входного сигнала, который был ранее на К периодах. Это обеспечивает считывание из БОП 28 кот да М счетчика 6, который он имел ранее на К периодах входного сигнала. На выходе второго блока 30 вычитания формируется разность кодов (0 - М).-

кодов счетчика 6 в моменты времени, . разделенные К.периодами анализируемого сигнала. Так как счетчик 6 работает с частотой fT , а время гЬикст

сации появления переднего фронта входного сигнала отмечается по состоянию счетчика 6, то величина (0 - M)f будет с точностью до.периода тактовой частоты определять длительность К периодов входного сигнала. Код длительности входного сигнала через инЛорма- ционные выходы выдается для записи во внешнее устройство одновременно с кодом числа периодов, для которого он определен (для этого используются адресные выходы). Счетчик 26 работает в режиме вычитания, поэтому с каждым импульсом на его втором (тактовом) входе выходной код его будет последовательно декрементироваться, представляя на выходах коды чисел К, (К-1), (К-2) и т.п. Соответственно на других выходах будут коды длительности К, (К-1 ), (К-2) периодов входного сигнала. При Формировании на втором выходе счетчика 26 (выходе переноса) сигнала логической 1 триггер 22 по второму входу устанавливается в исходное состояние, что обеспечивает блокировку работы счетчика 26 и установку на его выходах кода чисел К. На управляющем выходе формируется сигнал логического О, что свидетельствует об окончании цикла вычисления анализируемых длительностей сигнала,

Такчм образом, процесс декодирования сигнала (фиг. 3) сводится к вычислению по поступлении фронта входного сигнала кодов длительности его К, (К-1), (К-2)...(К-0) периодов и сравнении этих кодов с допустимыми значениями, хранящимися в блоке 10. При этом за счет увеличения выходной частоты сигнала делителя 3 частоты и постоянном значении полосы по срабатыванию .допустимые значения отклонения сЬронтов входного сигнала может достигать .нескольких периодов сигнала делителя. Причем чем больше разность чисел, определяющих максимальную и минимальную суммарные длительности нескольких периодов, тем ближе форма частотной характеристики устройства к прямоугольной. Поэтому отклонение частоты сигнала в определенных преде лах не приводит к изменению вероятности приема. Контроль же каждой сумц1

марной длительности нескольких периодов производится путем сравнения с двумя крайними допустимыми значениям вне зависимости от того, сколь велик между ними разность. Это дает возможность увеличивать частоту делителя 3 и тем самым улучшать (Ьорму частотной характеристики декодера без увеличения времени, затрачиваемого на обра- ботку. При этом полоса по срабатыванию определяется данными блока 10, что позволяет путем их изменения выбирать оптимальные характеристики устройства.

В предлагаемом устройстве распознавание принимаемой частоты производится сразу, что сокращает время обработки и расширяет диапазон обрабатываемых частот.

Формула изобретения

третий счетчик соединен с информаии- онными входами блока вычисления кода длительности входного сигнала, к сигнальному входу которого подключен выход компаратора, информационные выхо™- ления кода длительности входного сигдвоичных кодов, второй выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходом второго элемента И и с выходом дешифратора, первый вход первого счетчика соединен с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторыми входами первого и второго счетчиков и распределителя, тактовый вход которого соединен с тактовым входом блока вычисления кода длительности входного сигнала и входом делителя частоты.

ключеньт соответствующие выходы блока j-r ДРУгие входы которого соедивычисления кода длительности входного сигнала через первый коммутатор к другим входам которого подключены соответствующие выходы второго счетчянены с информационными входами бл ка оперативной памяти и выходами вх ного регистра, последовательно соед ненные первый триггер и второй сче

12

ка, а к управляющему входу первого коммутатора, входу элемента задержки и управляющему входу блока оперативной памяти подключен управляющий выход блока вычисления кода длительности входного сигнала, выходы блока оперативной памяти подключены к соответствующим входам второго коммутатора и блока сравнения двоичных кодов, к другим входам которого подключены выходы блока постоянной памяти и информационные входы выходного регистра, выходы которого через сумматор подключены к другим входам второго коммутатора, выходы которого соединены с входами блока постоянной памяти, тактовый вход которого соединен с тактовым входом выходного регистра, управляющим входом второго коммутатора, первым входом распределителя и подключен к выходу элемента задержки, первый выход распределителя подсоединен к первым входам первого элемента И и первого элемента ИЛИ, второй вход которого соединен с вторым выходом распределителя, первым входом второго счетчика и первым входом второго элемента И, второй вход которого соеди нен с первым выходом блока сравнения

ления кода длительности входного сигдвоичных кодов, второй выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходом второго элемента И и с выходом дешифратора, первый вход первого счетчика соединен с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторыми входами первого и второго счетчиков и распределителя, тактовый вход которого соединен с тактовым входом блока вычисления кода длительности входного сигнала и входом делителя частоты.

ления кода длительности входного сиг2. Устройство по п. 1, отличающееся тем, что блок вычиснала содержит последовательно соединенные первый счетчик, первый блок вычитания, коммутатор, блок оперативной памяти и второй блок вычитания,

нены с информационными входами блока оперативной памяти и выходами входного регистра, последовательно соединенные первый триггер и второй счетчик, выходы которого соединены с дру- ими выходами первого блока вычитания, и последовательно соединенные второй триггер и регистр сдвига, иер- , вый выход которого соединен с управляющим входом входного регистра, коммутатора и блока оперативной памяти, тактовый вход которого соединен с соответствующими входами регистра сдви-to

га и второго счетчика и является тактовым входом блока вычисления кода длительности входного сигнала, первые входы первого блока вычитания соединены с другими входами коммутатора} 15 первый вход первого счетчика соединен

с первым входом второго триггера, второй вход которого соединен с вторым , выходом регистра сдвига и первым входом первого триггера, второй вход которого соединен с вторым выходом второго счетчика, причем входы входного регистра, первый вход первого счетчика и второй вход второго счетчик а являются соответственно информационными, сигнальным и тактовым входами блока вычисления кода длительности входного сигнала, информационными, адресными и управляющим выходами являются соответственно выходы второго блоКа вычитания, второго счетчика и второй выход первого триггера.

Фиг.г

Составитель В.Евдокимова Редактор Н.Лазаренко Техред Л.Сердюкова Корректор О.Шотле

Заказ 1460

Тираж 526

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Авторское свидетельство СССР № 1160614, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-07—Публикация

1988-08-23—Подача