Изобретение относится к вычислительной технике, а именно к устройствам контроля постоянной памяти, и может быть использовано для контроля достоверности хранения информации в постоянных запоминаюп,их устройствах в процессе работы.

Целью изобретения является повышение точности контроля.

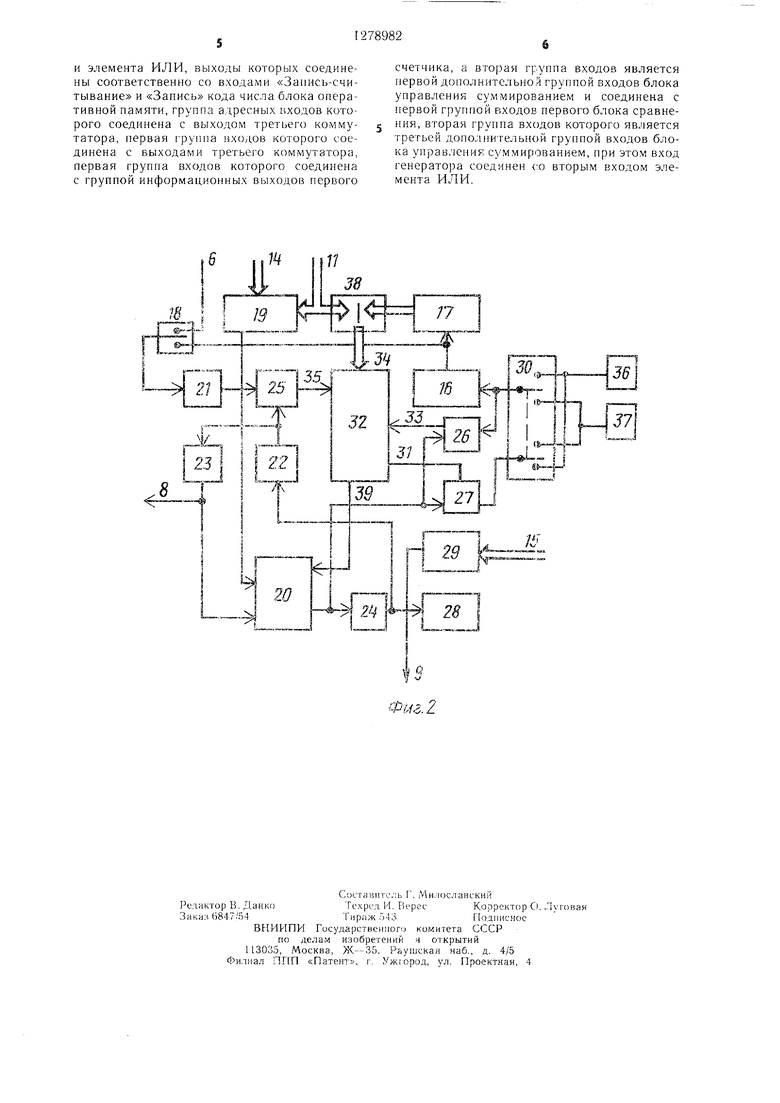

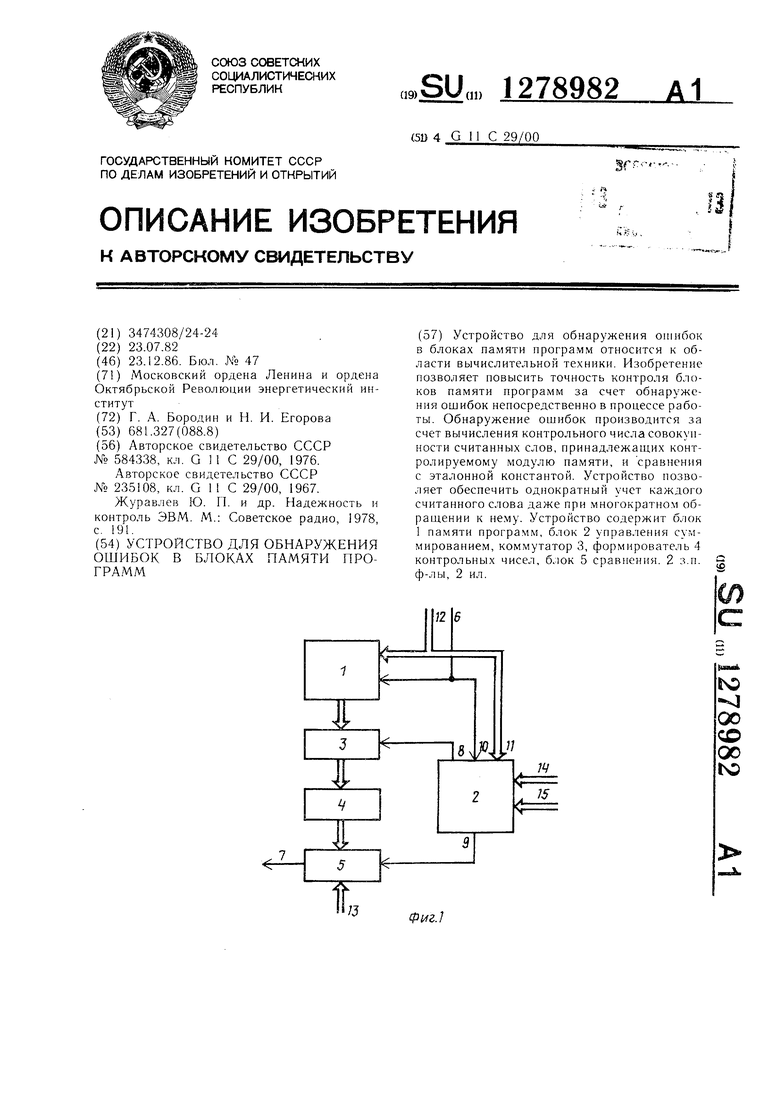

На фиг.1 представлена блок-схема устройства для обнаружения ошибок в блоках памяти программ; на фиг.2 -- блок-схема блока управления суммированием.

Устройство для обнаружения опшбок в блоках памяти программ содержит (фиг.1) блок 1 постоянной памяти, блок 2 управления суммированием, коммутатор 3, формирователь 4 контрольных чисел, блок 5 срав- неш Л, уиоаеляюший 15ход 6 и выход 7 устройств; . до1 о;и1итс,чьный выход 8 блока 2 управлении суммированием, унравляюнлий выход 9 и вход 10 блока 2 управления суммированием, 1ервую дополнительную rpyiuiy 11 iixo;ioB блока 2 управления сум- мированим, первую 12, вторую 1 3, третью 14 и четвертую 15 группы входов устройства.

Блок 2 улравлепия суммированием содержит (фиг.2) генератор 16, первый счетчик 17, первый коммутатор 18, первый блок 19 сравнения, триггер 20, первый 21, второй 22, третий 23 и четвертый 24 одновиб- раторы, формирователь 25 считывания, элементы ИЛИ 26, И 27, второй счетчик 28, второй блок 29 срав)ения, второй коммутатор 30, вход 31 « Запись-считывание блока 32 оперативной ггамяти, информационный вхо;, 33, адресные входы 34, вход 35 выборки блока 32 оперативной намяти, первый 36 и второй 37 источпики напряжепия, третий коммутатор 38, информационный выход 39 блока 32 оп.еративной памяти.

Формирователь 25 считьпзания может быть выполнен на элементе И, если блок 32 онератиЕП-юй па.мяти управляется нулевым логическим сигналом по входу 35 выборки, и на элементе ИЛИ, если - единичным.

Блок оперативной памяти должен иметь быстродействие при обра имении в два раза вы- И1е, чем контролг руемый блок 1 постоянной намяти.

В качестве форми)ователя 4 контрольных чисел можно использовать сумматор, сумматор с различными обратными связями, параллельный сигнатурный анализатор и т. п.

Устройство работает следующим образом.

Подготовительный режим. В подоготови- тельном режиме во ice ячейки блока 32 оперативной памяти записываются единицы признак отсутствия обращения к данной ячейке. Для этого коммутатор 38 нере- ключают на прием адресов от первого счетчика 17, коммутатор 18 переводят в режим приема игчшульсов обращения от геперато- ра 16. Второй коммутатор 30 Г ереводят в верхнее (но фиг.2) но,,1Ожепие, что обеспечивает нодачу на входы генератора 16 и

элемент ИЛИ 26 разреп1ающего потенциала от первого источника 36 напряжения и запирающего потенциала на вход элемента И 27 от второго источника 37 папряжения. В

результате этих переключений на вход 33 оперативного блока 32 онеративной памяти поступает логическая единица на запись, а на вход 31 - логический ноль, означающий режим заниеи. Генератор 16 вырабатывает импульсы с определенной частотой, которые через коммутатор 18, одновибратор 21, формирователь 25 считывания поступают на вход 35 разрен1ения выборки оперативного блока 32 оперативной на.мяти. Кроме того, они поступают и на вход счетчика 7,

вследствие чего он носледователык) меняет свое состояние, «пробегая тем самым всю возможную пос.ледовательность адресов, поступающих через коммутатор 38 па адресные- входы 34 блока 32 онеративной памяти, Указанные действия нриводят к тому, что но

всем адресам блока 32 oнepaтив oй намяти будут записаны един;-ни 1. Формирс)вате.ль 4 контрольных чисел обнуляется.

По окончании под| отовительпого режима второй коммутатор 30 г.ереводят в нижнее

(на фиг.2) положение, в результате чего работа генератора Hi блокируется, на вход элемента ИЛИ 26 поступает ;1огическпй ноль, а на вход элемента И 27 - логические единицы. Коммутатор 38 переводят на режим приема адресов из внен;иего устройства но

дополпительной rpyn ie 1 1 входов. Коммутатор 18 переключают на рехким приема импульсов обращения г.ыборки от входа 6. На вход блока 19 сравнения по i-pyniie 14 входов подают коды адресов ;1азрялов, которые онреде,ля1от адрес моду,ля (б.лока)

памяти, KOTOporsj бул.ет гюдсчнтыгип ься контрольное число. На вход блгжа 29 сравнения по группе 15 входов ода1от код, озн.а- чаюпшй количество чнсе,, хранящихся в контролируемом модуле, что необходим) д, онределения конца работы ип контролю выбранного модуля нагляти,

Режим контроля. В 1Л юцессе заботы к блоку 1 памяти по rpymie i2 входов поступают адреса запранл1ваемых чисел, а но входу 6 - сигнал обраггепия. Выб1и;аемые ч;лсла поступают на выход б.юка i памяти, Коды адресов поступают также в блок управления суммированием. Импульсы выборки по входу 6 поступают также в блок 2. Если коды старших адресов, поступающих но грущшм 14 и 11 входов, coBPiaдают, что означает обращение к контролируемому модулю намяти, то блок 19 сравнения вырабатывает разренгающий г отенциа..л, поступающий па D-вход триггера 20, Импульс разрешения выборки по входу 6 поступает через коммутатор 18 на вход одновибратора 21, который формирует нужной длительности для обрапгеиия к 6,io- ку 32 оперативной гамяти, 1остун;-;юни1й через формирователь 25 на вход 35. Коды

адресов младших разрядов в это время через коммутатор 38 поступают на вход 34. По входу 31 установлен режим считывапия из блока 32 памяти. В результате этого но запрашиваемому адресу выбирается информа- ция (единица или ноль). Возможны два продолжения работы блока 2:

1.Если считывается единица - признак первого обращения по данному адресу, она поступает на С-вход триггера 20 и по раз- решаюнхему потенциалу па его входе (D) переводит его в единичное состояние. На выходе триггера 20 (инверсном) появится логический ноль, который через элемент И 27 установит режим записи по входу 31 и запись логического ноля по зходу 33 через элемент ИЛИ 26. Одновибратор 24 выраба- ThHjaeT по переднему фронту переключения триггера 20 импульс-, поступает на счетный вход счет шка 28 и через одновиб- ратор 22 и формирователь 25 па вход 35 блока 32. Это приводит к повторному обрате- нию по дапному адресу, по уже в режиме записп ноля. Через одповибратор 23 импу.чьс

по заднему фронту импульса с одновибрато- ра 22 р.остунит на выход 8 блока 2 и далее на разрешение коммутатора 3. Считан- ный из блока 1 намяти код поступит через коммутатор 3 в формирователь 4, где и сложится с его содержимым.

2.Если считывается ноль - признак новторпого обрап;ен 1Я по дапному адресу, то триггер 20 не срабатывает, едипица в счет- чик 28 пе добаз, яется, считываемое число через коммутатор 3 не поступает в формирователь 4 коптрольпых чисел.

Устройство по: воляет таким образом обеспечить однократное суммирование всех чисел даже поп многократном и непостоян- но.м но частоте количестве обрапхений к от- дельпым словам. Для определения конца проверки данного модуля необходимо испо;1ь- зовать блок 29 сравнепня. В резул.ьтате контроля в счетчике 28 подсчитывается количество обра1цений, которое сравнивается с числом, поступающим по группе 15 входов, и в момент сравнения вырабатывается признак сравнения, который по выходу 9 поступает на вход блока 5 cpauneniiH, и там производится еравпение ио;|учеппого контрольпого числа с этало1 пым, поступающим но rpyniie 13 входов. Прпзнак сравнения или несравнения вырабатываетсу па выходе 7 устройства.

Форму Ю- изобретения

1. Устройство для обнаружения оши.бок в блоках программ, содержащее блок памяти ф01-раму., группа адресных входов которого яв. яет; я первой группой входов устройства, ) вход соединен с управля1ОП1Им входом блока управления суммированием и является уп)авляюн1,им входом устройства, формирователь контрольп1 1Х чи10

5

(5 20

25

зо

5

0 .0

5

сел, группа информационных выходов которого соединена с первой группой информационных входов блока сравнения, управляющий вход которого соединен с управляю- пхим выходом блока управления суммированием, а вторая группа информационных входов и выход б,1ока сравнения являются соответственно второй группой входов устройства и выходом устройства, отличающееся тем, что, с целью повышения точности контроля, оно содержит коммутатор, группа информационных входов которого соединена с группой информационных выходов блока памяти программ, управляющий вход - с дополнительным управляющим выходом блока управ,тения суммированием, а группа информационных выходов коммутатора соединена с группой информационных входов формирователя контрольных чисел, при этом группа адресных входов блока памяти нрО|-рамм соединена с первой дополнительной группой входов блока управления суммированием, вторая и третья дополнительные грунпы входов которого являются соответственно третьей и четвертой группами входов устройства.

2. Устройство но п. 1, отличающееся тем, что б,ток управления суммированием содержит коммутаторы, элементы И и ИЛИ, D-триггер, блоки сравнения, одновпбратор|11, блок оперативной памяти,счетчики, источник напряжения и генератор, выход кото(1ого соединен со входом нервого счетчика п первым входом первого коммутатора, второй вход которого является управляющим входом блока управления суммированпм, а выход соедине через первый одновибратор с первым входом формирователя обрап1еппя, выход которого соединен со входом разрен е- ния выборки блока оперативной памяти, а второй вход - с выходом второго одиовиб- ратора и входом третьего одновибратора, причем выход третьего одновибратора является дополнитеьным управляющим выходом блока управления суммированием и соединен с R-входом D-триггера, D-вход которого сое- динен с выходом первого блока сравнения, С-вход - с информационным выходом блока оперативной памяти, а инверсный выход с первыми входами элемента ИЛИ и элемента И, а через четвертый одновибратор - со входом второго одновибратора и входом второго счетчика, группа информационных выходов которого подключена к нервой группе входов второго блока сравнения, вторая группа входов которого является второй дополнительной группой входов блока управления суммированием, а выход второго б, 1ока сравнения является управлякпцим (Vv1 блока управ.тения суммированием, rijin этом первый и второй источники )апряження соединены соответственно с грунг1ОЙ первых и вторых входов второго коммутатора, первый и второй выходы которого соединены соответственно с вторыми входами элемента И

и элемента ИЛИ, выходы которых соединены соответственно со входами «Запись-считывание и «Запись кода числа блока оперативной памяти, группа адресных входов которого соединена с выходом третьего коммутатора, первая группа входов которого соединена с выходами третьего коммутатора, первая группа входов которого соединена с группой информационных выходов первого

счетчика, а вторая группа входов является первой дополнительной группой входов блока управления суммированием и соединена с первой группой входов первого блока сравнения, вторая группа входов которого является третьей дополнительной группой входов блока управлепия суммированием, при этом вход генератора соединен со вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

Устройство для обнаружения он1ибок в блоках памяти программ относится к области вычислительной те.хники. Изобретение позволяет повысить точность контроля блоков памяти программ за счет обнаружения ошибок непосредственно в процессе работы. Обнаружение ошибок производится за счет вычисления контрольного числа совокупности считанных слов, принадлежащих контролируемому модулю памяти, и сравнения с эталонной константой. Устройство позволяет обеспечить однократный учет каждого считанного слова даже при многократном об- рагцении к нему. Устройство содержит блок 1 памяти программ, блок 2 управления суммированием, коммутатор 3, формирователь 4 контрольных чисел, боюк 5 сравнения. 2 з.п. g ф-лы, 2 ил. к д 00 со ОС Ю фиг.

.2

| Устройство для контроля блоков постоянной памяти | 1976 |

|

SU584338A1 |

| Солесос | 1922 |

|

SU29A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ ПАМЯТИ | 0 |

|

SU235108A1 |

| Солесос | 1922 |

|

SU29A1 |

| Журавлев Ю | |||

| П | |||

| и др | |||

| Надежность и контроль ЭВМ | |||

| М.: Советское радио, 1978, с | |||

| Устройство непрерывного автоматического тормоза с сжатым воздухом | 1921 |

|

SU191A1 |

Авторы

Даты

1986-12-23—Публикация

1982-07-23—Подача