Изобретеиие относится к области запоминающих устройств.

Известны устройства для контроля блоха постоянной памяти с контролем на четность, в которых наблюдаются ограниченное быстродействие нз-за значительного времени образования суммы цифр по mod 2; сложность контрольного оборудования; необходимость выделения дополнительного контрольного разряда.

Предлагаемое устройство для контроля блока отличается тем, что оно содержит регистр параллельного действия со счетнЕями входами, подключенными к выхол,ным шипам блока, узел установки контрольной суммы и схему сравнения, соединенную с указанным регистром и узлом установки. Это позволяет упростить устройство и повысить его быстродействие.

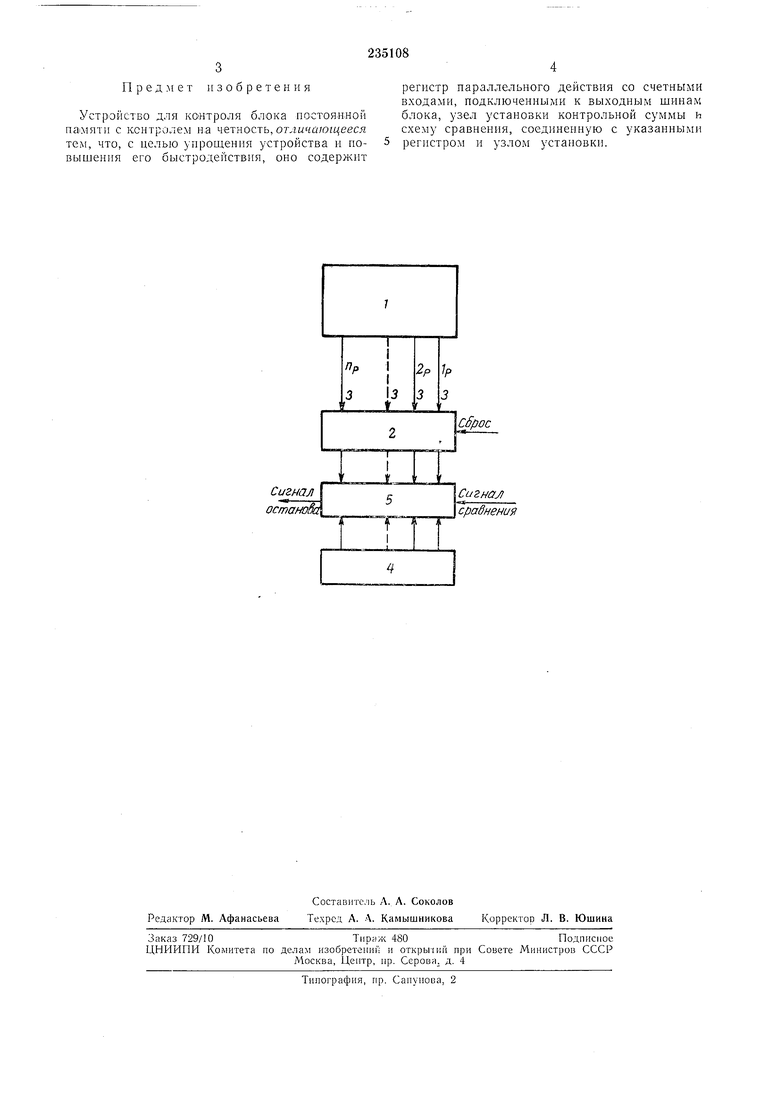

Па чертеже изображена блок-схема контрольного устройства.

При подаче на вход блока / постоянной памяти кода адреса и импульса запроса с выхода считывается л-разрядное число.

Устройство для контроля блока 1 постоянной памяти с контролем на четкость содержит регистр параллельного действия 2 со счетными входами 3, подключенными к выходным шинам блока /, узел установки контрольной суммы 4 и схему сравнения 5, соединенную с регистром 2 и узлом 4 установки.

Перед считыванием первого числа сигналол «сброс все разряды регистра устанавливаются в состояние «О, далее в него записывается первое число, считанное из блока. Единицы второго числа изменяют состояния соответствующих разрядов регистра на противоположные.

считывания всех чисел блока / в регистре 2 будет записана иоразрядная сумма, которая ири приходе сигнала сравнения сравнивается с контрольной суммой установленной в узле 4 установки. Если суммы совиадают, цикл иовторяется, если иет, вырабатывается сигнал останова.

Описанное контрольное устройство не. требует запнси в блок У дополнительного контрольного разряда и иозво.:1яет оиределить одинарную ошибку, возникающую в одном разряде группы чисел и количество ошибок, равное разрядности чисел (по одной в каждом разряде).

Место ошибки находится последовательным изменением днапазона адресов, при этом каждый раз в узле 4 устанавливается своя контрольная сумма. Регистр со счетными входами можно поставить и в блок /. Для контроля блока памяти следует отключить сигнал «сброс регистра, который необходи.м для раПредмет изобретения

Устройство для контроля блока постоянной naiMHTii с контролем н.а ч&ткостъ, отличающееся тем, что, с целью упрощения устройства п повышення его быстродействия, оно содержит

регистр параллельного действия со счетными входами, подключенными к выходным шинам блока, узел установки контрольной суммы и схему сравнения, соединенную с указанными регистром и узлом установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1977 |

|

SU714503A1 |

| Устройство для контроля блоков постоянной памяти | 1975 |

|

SU668008A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

Даты

1969-01-01—Публикация