Изобретение относится к автоматике и вычислительной технике и может быть использовано н системах числового программного управления .

Целью изобретения является повьппе- ние надежности системы ЧПУ зя счет введения режима автоматического обхо- ла алресов ОЗУ с неисправными элемен тами памяти без выключения системы и 10 ее ремонта. Причем даже при наличии многих неисправных ячеек система полностью сохраняет работоспособность и функционапьные возможности, а объем ОЗУ уменьшается лишь на коли- 15 честно неисправных элементов памяти.

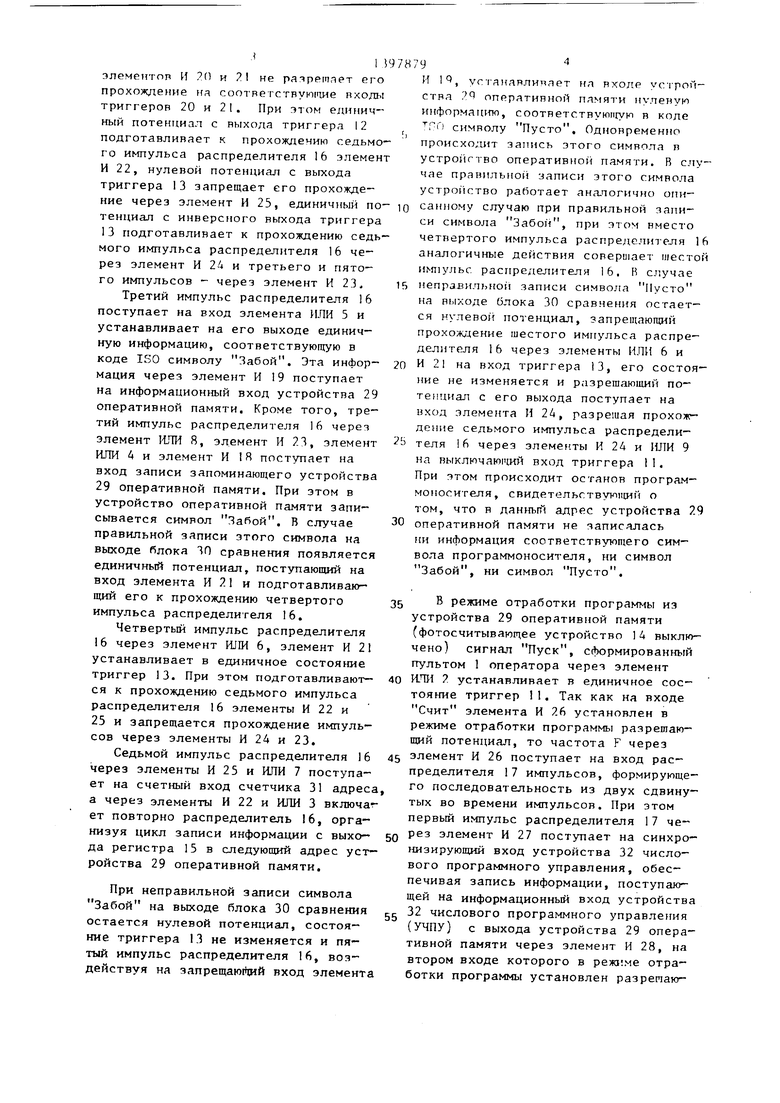

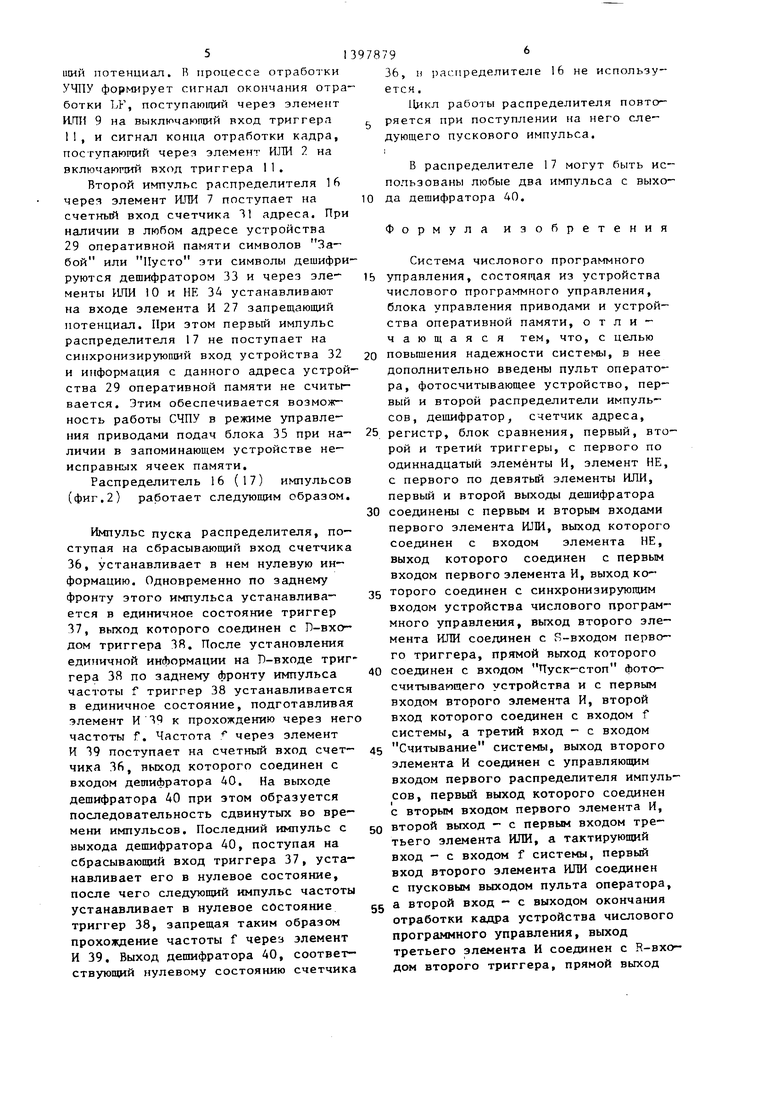

На фиг.1 изображена структурная схема предлагаемой системы; на фиг.2 возможный вариант вьтолнения распре- депителей импульсов,20

Система (фиг.1) состоит из пульта 1 оператора, элементов ШШ 2-10, триггеров 11-13, фогосчитывающего устройства 1А, регистра 15, распределителей 16 и 17 импульсов, элементов 25. И 18,28, устройства 29 оперативной памяти, блока 30 сравнения, счетчика 31 адреса, устройства 32 числового программного управления, дешифратора

нал СИ через элемент ИЛИ 3 включает распределитель 16, формирующий последовательность импульсов с частотой , поступающей на его тактовьт вход.

Первый 1тмпульс распределителя 1 (S устанавливает в единичное сос гояние триггер 12 и в нулевое состояние триггер 13 и через элемент ИЛИ 4 и элемент И 18, стробированный частотой, поступающей на второй вход элемента И 18, поступает на вход записи устройства оперативной памяти 29. При этом информация, соответствующая символу, считываемому с фотосчитываю- шего устройства 1Д, с выхода регист- -ра 15 через элемент ИЛИ 5 и элемент И 19 поступает на информационный вход устройства 29 оперативной памяти и записывается в него. Записанная информация сравнивается с входной информацией блоком 30 сравнения и в случае их равенства единичный потенциал с выхода блока 30 сравнения поступает на входы элементов И 20 и 21.

Второй импульс распределителя 16 через элемент И 20 устанавливает в нулевое положение триггер 12, а через

33, элемента НЕ 34 и блоков 35 управ-30 элемент ШТИ 6, элемент И 7.1 и триггер ления приводами.

Распределитель импульсов (фиг.2) состоит ия счетчика 36 импульсов, триггеров 37 и 38, элемента И 39 и дешифратора 0.

В основе работы предлагаемого устройства чаложет о свойство кодов ТЯО, в которых комбинация Пусто (отсутствие единицу и Забой (все единицы) не воспринимаются системами ЧПУ, так как блокирует импульс сопровождения (си). Это свойство и использовано для повышения надежности системы числового программного управления с миП-в единичное состояние. При этом нулевой потенциал с выхода триггера 12 запрещает прохождение седьмого импульса распределителя 16 через эле- 25 мент И 22, нулевой потенциал с выхода триггер I3 запрещает прохождение третьего и пятого импульсов распределителя 16 через элемент И 23 и седьмого импульса через элемент И 24. Раэрешаюш 1й потенциал с единичного выхода триггера 13 поступает на вход элемента И 25 и седьмой импульс рас пределителя 16 через элемент И 25 и элемент ИЛИ 7 поступает на счетный

40

нимальными затратами, без функциональ-дз ход счетчика 31 адреса, информацион

ограничений.

Система работает следующим обра зом.

Сигнал Пуск, сформирован штй пультом 1 оператора, через элемент ИЛИ 2 устанавливает в единичное состояние трип ер I 1 , выходной сигнал которого включает фотосчитывающее устройство (ФСУ) 14. Информация с ФСУ в коде ISO, сопровождаемая синхроимпульсом (си), поступает на информационный вход регистра 15, куда и записьшает- ся по сигналу СИ. Одновременно сиг-

нал СИ через элемент ИЛИ 3 включает распределитель 16, формирующий последовательность импульсов с частотой , поступающей на его тактовьт вход.

Первый 1тмпульс распределителя 1 (S устанавливает в единичное сос гояние триггер 12 и в нулевое состояние триггер 13 и через элемент ИЛИ 4 и элемент И 18, стробированный частотой, поступающей на второй вход элемента И 18, поступает на вход записи устройства оперативной памяти 29. При этом информация, соответствующая символу, считываемому с фотосчитываю шего устройства 1Д, с выхода регист- -ра 15 через элемент ИЛИ 5 и элемент И 19 поступает на информационный вход устройства 29 оперативной памяти и записывается в него. Записанная информация сравнивается с входной информацией блоком 30 сравнения и в случае их равенства единичный потенциал с выхода блока 30 сравнения поступает на входы элементов И 20 и 21.

Второй импульс распределителя 16 через элемент И 20 устанавливает в нулевое положение триггер 12, а чере

элемент ШТИ 6, элемент И 7.1 и триггер

П-в единичное состояние. При этом нулевой потенциал с выхода триггера 12 запрещает прохождение седьмого импульса распределителя 16 через эле- мент И 22, нулевой потенциал с выхода триггер I3 запрещает прохождение третьего и пятого импульсов распределителя 16 через элемент И 23 и седьмого импульса через элемент И 24. Раэрешаюш 1й потенциал с единичного выхода триггера 13 поступает на вход элемента И 25 и седьмой импульс рас пределителя 16 через элемент И 25 и элемент ИЛИ 7 поступает на счетный

ный выход которого соединен с адресным входом устройства 29 оперативной памяти. На этом цикл записи одного символа заканчивается. Цикл повторяется при поступлении очередного импульса СИ с фотосчитывающего устройства 14 или пульта 1 оператора.

При неправильной записи информации в устройство 29 оперативиой памяти на выходе блока 30 сравнения устанавливается нулевой потенциал. При этом второй импульс распределителя 16 изменяет состояния триггеров 12 и 13, так как нулевой потенциал на входах

1

элементов И 20 и 71 не ряярегппет его прохождение ня соответствуюпие входы триггеров 20 и 21. При этом единичный потенгшал с выхода триггера 12 подготавдивает к прохождению седьмого импульса распределитедя 16 элемент И 22, нулевой потенциал с выхода триггера 13 запрещает его прохождение через элемент И 25, единичный по- тенциал с инверсного выхода триггера 13 подготавливает к прохождению седьмого импульса распределитедя 16 через элемент И 2Д и третьего и пятого импульсов - через элемент И 23,

Третий импульс распределителя 16 поступает на вход элемента ИЛИ 5 и устанавливает на его выходе единичную информацию, соответствующую в коде ISO символу Забой. Эта инфор- мация через элемент И 19 поступает на информационнь й вход устройства 29 оперативной памяти. Кроме того, третий импульс распределителя 16 через элемент 11ПИ 8, элемент И 23, элемент ИЛИ 4 и элемент И 18 поступает на вход записи запоминающего устройства 29 оперативной памяти. При этом в устройство оперативной памяти записывается символ Забой. В случае правильной записи этого символа на выходе блока 30 сравнения появляется единичный потенциал, поступающий на вход элемента И 21 и подготавливающий его к прохождению четвертого импульса распределителя 16.

Четвертый импульс распределителя 16 через элемент ШШ 6, элемент И 21 устанавливает в единичное состояние триггер 13. При этом подготавливают- ся к прохождению седьмого импульса распределителя 16 элементы И 22 и 25 и запрещается прохождение импульсов через элементы И 2Д и 23.

Седьмой импульс распределителя 16 через элементы И 25 и ИЛИ 7 поступает на счетный вход счетчика 31 адреса а через элементы И 22 и ИЛИ 3 включа ет повторно распределитель 16, организуя цикл записи информации с выхо- да регистра 15 в следующий адрес устройства 29 оперативной памяти.

При неправильной записи символа Забой на выходе блока 30 сравнения остается нулевой потенциал, состояние триггера 13 не изменяется и пятый импульс распределителя 16, воздействуя на запрещающий вход элемента

6

0 Ь 0 5

0

5

5

И 14 ус г андрлиплет нл РХОЛР устройства оперягипной памяти нулевую информацию, соответствуюпгую в коде Ti i символу Пусто. Одновременно происходит запись этого символа п устройство оперативной памяти. В случае правильной записи этого символа ycTpoiicTBo работает аналогично они- сан))ому случаю при правильной записи символа Забой, при этом вместо четвертого импульса распределителя 16 аналогичные действия совершает 1лестой и пlyльc распределителя 16, R случае неправиль(ой записи символа Пусто на выходе блока 30 сравнения остается нулевой потенциал, запрещающий прохождение шестого импульса распре- дел 1теля 16 через элементы ИЛИ 6 и И 21 на вход триггера 13, его состояние не изменяется и разрешающий потенциал с его выхода поступает на вход элемента И 24, разре .иая прохож- дение седьмого импульса распределителя 16 через элементы И 24 и ИЛИ 9 на вьгключаю1чий вход триггера 1 I. При этом происходит останов программоносителя, свидет«льствук111шй о том, что в данньп адрес устройства 29 оперативной памяти не записалась ни информация соответствующего символа программоносителя, ни символ Забой, ни символ Пусто.

В режиме отработки программы из устройства 29 оперативной памяти (фотосчитывяюгдее устройство 14 выключено) сигнал Пуск, сформированный пультом 1 оператора через элемент ИЛУ1 2 устанавливает в единичное состояние триггер I1. Так как на входе Счит элемента И 26 установлен в режиме отработки программы разрешающий потенциал, то частота F через элемент И 26 поступает на вход распределителя 17 импульсов, формирующего последовательность из двух сдвинутых во времени импульсов. При этом первый импульс распределителя 17 через элемент И 27 поступает на синхронизирующий вход устройства 32 числового программного управления, обеспечивая запись информации, поступающей на информационный вход устройства 32 числового программного управления (УЧПУ) с выхода устройства 29 оперативной памяти через элемент И 28, на втором входе которого в режиме отработки программы установлен разрепаю51

ший потенциал. В процессе отработки УЧ1ТУ формирует сигнал окончания отработки LF, поступаю1ций через элемент И.ГТИ 9 на выключаюпшй вход триггера 1 , и сигнал конца отработки кадра, поступающий через элемент ИЛИ 2 на включающий вход триггера 11.

Второй импульс распределителя 16 через элемент ИЛИ 7 поступает на счетный вход счетчика 31 адреса. При наличии в любом адресе устройства 29 оперативной памяти символов Забой или Пусто эти символы дешифрируются дешифратором 33 и через эле- менты ИЛИ 10 и НЕ 34 устанавливают на входе элемента И 27 запрещающий потенциал. При этом первьш импульс распределителя 17 не поступает на синхронизирующий вход устройства 32 и информация с данного адреса устройства 29 оперативной памяти не считывается. Этим обеспечивается возможность работы СЧПУ в режиме управления приводами подач блока 35 при на- личии в запоминающем устройстве неисправных ячеек памяти.

Распределитель 16 (17) импульсов (фиг.2) работает следующем образом,

Импульс пуска распределителя, поступая на сбрасывающий вход счетчика

36,устанавливает в нем нулевую информацию. Одновременно по заднему фронту этого импульса устанавлива- ется в единичное состояние триггер

37,выход которого соединен с П-вхо- дом триггера 3R. После установления единичной информации на D-входе триг гера 38 по заднему фронту импульса частоты f триггер 38 устанавливается

в единичное состояние, подготавливая элемент И 39 к прохождению через нег частоты f. Частота через элемент И 39 поступает на счетный вход счет- чика 36, выход которого соединен с входом дешифратора 40. На выходе дешифратора 40 при этом образуется последовательность сдвинутых во времени импульсов. Последний импульс с выхода дешифратора 40, поступая на сбрасывающий вход триггера 37, устанавливает его в нулевое состояние, после чего следующий импульс частоты устанавливает в нулевое состояние триггер 38, запрещая таким образом прохождение частоты f через элемент И 39. Выход дешифратора 40, соответ- ствуюш 1й нулевому состоянию счетчика

796

36, I) распределителе 16 не используется .

Цикл работы распределителя повторяется при поступлении на него следующего пускового импульса.

В распределителе 17 могут быть использованы любые два импульса с выхода дешифратора 40.

Формула изобретения

Система числового программного управления, состоящая из устройства числового программного управления, блока управления приводами и устройства оперативной памяти, отличающаяся тем, что, с целью повышения надежности системы, в нее дополнительно введены пульт оператора, фотосчитывающее устройство, первый и второй распределители импульсов, дешифратор, счетчик адреса, регистр, блок сравнения, первый, второй и третий триггеры, с первого по одиннадцатый элементы И, элемент НЕ, с первого по девятый элементы ИЛИ, первый и второй выходы дешифратора соединены с первьм и вторым входами первого элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с синхронизирующим входом устройства числового программного управления, вьгход второго элемента ИЛИ соединен с R-входом первого триггера, прямой выход которого соединен с входом Пуск-стоп фото- считываюцего устройства и с первым входом второго элемента И, второй вход которого соединен с входом f системы, а третий вход - с входом Считывание системы, выход второго элемента И соединен с управляющим входом первого распределителя импульсов, первый выход которого соединен с вторым входом первого элемента И, второй выход - с первым входом третьего элемента ИЛИ, а тактирующий вход - с входом f системы, первый вход второго элемента ИЛИ соединен с пусковым выходом пульта оператора, а второй вход - с выходом окончания отработки кадра устройства числового программного управления, выход третьего элемента И соединен с R-входом второго триггера, прямой выход

которого соединен с первым входом четвертого элемента И, выход которого соединен с первым входом четвертого элемента ШШ, выход которого соединен с управляюпитм входом второго распределителя импульсов, выход пятого элемента ИЛИ соединен с первым входом пятого элемента И, выход которого соединен с S-входом третьего триггера, прямой выход которого соединен с вторым входом четвертого элемента И и с первым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом счетчика адреса, выход которого соединен с адресным входом устройства оперативной памяти, информационный выход которого соединен с первым вхо- дом блока сравнения и с первым входом седьмого элемента И, ииверсный выход третьего триггера соединен с первым входом восьмого элемента И и с первым входом девятого элемента И, выход ко- торого соединен с первым входом шестого элемента ИЛИ, выход которого соединен с R-входом первого триггера, второй вход шестого элемента ИЛИ соединен с выходом окончания отработки LF устройства числового программного управления, выход седьмого элемента ИЛИ соединен с вторым входом восьмого элемента И, выход которого соединен с первым входом восьмого элемен- та ИЛИ, выход которого соединен с первым входом десятого элемента И, второй вход которого соединен с входом f системы, а выход - с входом записи устройства оперативной памяти, выход регистра соединен с первым

входом девятого элемента КТИ, выход которого соединен с первым входом одиннадцатого элемента И, выход которого соединен с инЛopмaциoнfгым входом устройства оперативной памяти и с вторым входом блока сравнения, выход которого соединен с вторым входом пятого элемента И и первым входом третьего элемента И, второй вход седьмого элемента И соединен с входом Считывание системы, а выход - с информационными входами устройства числового программного управления, регистра, дешифратора и с информационными выходами пульта оператора и фо- тосчитывающего устройства, вход f системы соединен с тактирующим входом второго распределителя импульсов, первый выход которого соединен с S-входом второго триггера, с R-входом третьего триггера и с вторым входом восьмого элемента ИЛИ, второй выход - с первым входом пятого элемента ИЛИ и вторым входом третьего элемента И, третий выход - с вторым входом девятого элемента Ш1И и с первым входом седьмого элемента ИЛИ, четвертый выход - с вторым входом пятого элемента ИЛИ, пятый выход - с эапрещающим входом одиннадцатого элемента И и с вторым входом седьмого элемента КГГИ, шестой выход - с третьим входом пятого элемента ИЛИ, седьмой выход - с третьим входом четвертого элемента И и с вторыми входами шестого и девятого элементов И, второй вход четвертого элемента ИЛИ соединен с входом записи регистра и с синхрониэи- рующими выходами пульта, оператора и фотосчитывающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания циклов в системах цифрового программного управления | 1985 |

|

SU1280575A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Система программного управления | 1984 |

|

SU1200245A1 |

| Устройство для контроля систем программного управления станком | 1988 |

|

SU1580320A1 |

| Устройство для программного управления позиционного типа | 1983 |

|

SU1158976A1 |

| Устройство для программного управления станком | 1985 |

|

SU1352458A1 |

| Устройство для программного управления | 1986 |

|

SU1397878A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

Изобретение относится к автомат тике и вычислительной технике и может быть использовано в системах числового программного управления станками. Целью изобретения является повышение надежности системы. Б систему числового программного управления (ЧПУ), состоящую из устройства ЧПУ (УЧПУ), блока управления приводами и устройства оперативной памяти, введены дополнительно пульт оператора, фото- считывающее устройство и логический блок, обеспечивающий совместную работу этих устройств в режимах считывания и записи. В режиме алписи информация из фотосчитывающего устройства записьгеается в устройство оперативной памяти. При зтом логический блок обеспечивает запись информации только в исправные ячейки памяти, автоматически определяя неисправные ячейки и записывая в них либо код Пусто, либо код Забой (коды ISO). В режиме считывания осуществляется чтение записанного массива информации из устройства оперативной памяти и передача его в УЧПУ, При зтом синхроимпульсы сопровождения, по которым осуществляется запись информации в УЧПУ, для кодов Пусто и Забой не вырабатываются. Сущность изобретения заключается в реализации автоматического обхода адресов устройства оперативной памяти без выключения системы и ее ремонта, 2 ил. & (Л со ( 00 со

.2

| Васильев В.В | |||

| и др | |||

| Устройство ЧПУ широкого применения на основе микропроцессоров.- Приборы и системы управления, 1978, № 11, с.8 | |||

| Авторское свидетельство СССР 1222083, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-05-23—Публикация

1986-10-14—Подача