Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных процессоров.

Целью изобретения является сокращение аппаратурных затрат.

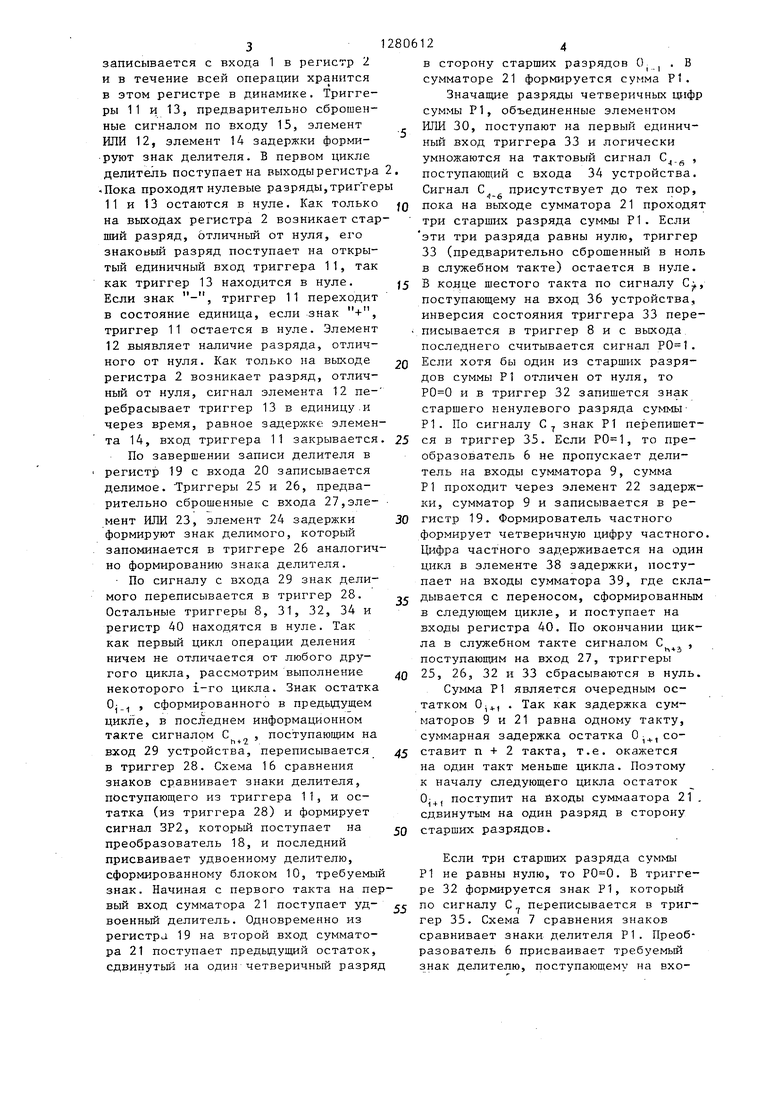

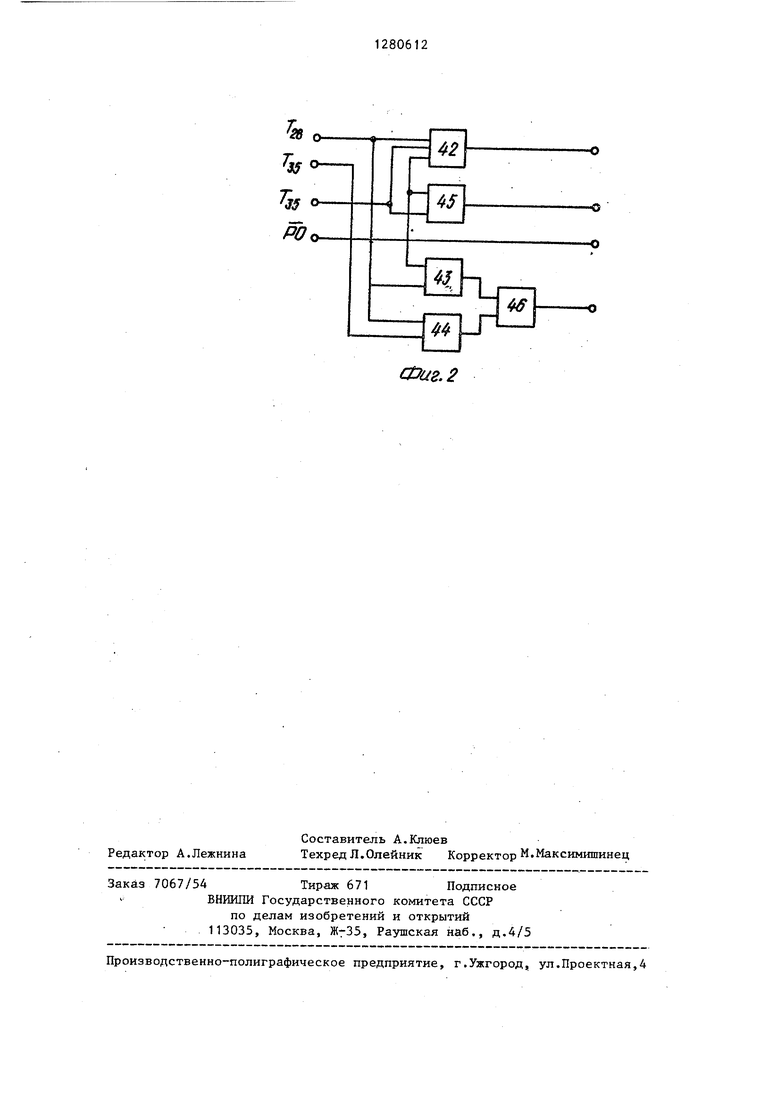

На фиг.1 представлена схема устройства для деления в избыточном кoдej на фиг.2 - схема узла формирования частного.

Устройство для деления в избыточном коде (фиг.1) содержит вход 1 делителя устройства, регистр 2 делителя, элементы 3-5 задержки, пре- образователь.6 в обратный код, схему 7 сравнения знаков, триггер 8, сумматор 9, блок 10 умножения на два, триггер 11, элемент ИЛИ 12, триггер 13, элемент 14 задержки, вход 15 сброса устройства, схему 16 сравнения знаков, элемент 17 задержки, преобразователь 18 в обрат- ный код, регистр 19 делимого, вход 20 делимого устройства, сумматор 21, элемент 22 задержки, элемент ИЛИ 23 элемент -24 задержки, триггеры25 и 26, вход 27 сброса .устройства, триггер 28, тактовый вход 29 устройства элемент ИЛИ 30, элемент 31 задержки, триггеры 32 и 33, тактовый вход 34 устройства, триггер 35, тактовый вход 36 устройства, узел 37 формирования частного, элемент 38 задержки сумматор 39, регистр 40 частного и выход 41 частного устройства.

Узел 37 формирования частного (фиг.2) содержит элементы И 42-44 и элементы ШШ- 45 и 46.

Регистр 2 делителя представляет собой последоватепьный (и + 3)-раз- рядньш .четверичный регистр для записи и хранения последовательных четверичных .чисел.

Элементы 3 и 5 задержки - одно- такт1П)1е четверичные элементы задержки, состоящие из трех обычных двоичных однотактньпс элементов задержки. Элемент 4 задержки представляет собой пятитактный четверичный элемент задержки.

Установка в единицу триггеров .11, 26, 32 и 33 происходит при подаче единичных значений на их первый и второй единичные входы. Преобразователь 6 в обратный код производит изменение-знака на противоположный при единичном значении на входе разO

0

5

5

решения преобразования, передача информации через преобразователь 6 запрещается при единичном значении на входе блокировки. Преобразователь 10 в обратный код производит изменение знака на противоположный при единичном значении на входе разрешения преобразования. Регистр 19 служит для хранения делимого и текущего остатка и представляет собой (п - 3) разрядный четверичный регистр. Регистр 40 представляет собой п-раз- рядный четверичный регистр сдвига, По завершении деления частное может быть считано в последовательном коде на выход 41 устройства.

Цикл деления занимает п + 3 так- та, из которых п + 2 такта - информационные и один - служебный. Информационные такты используются для передачи и обработки чисел старшими разрядами вперед, служебный так,т (п + 3) - для управления.

Сигнал на вход 15 подается перед 5 началом операции. Например, его можно подат.ь в такте (п + 3) в цикле записи делителя в регистр 2. Сигнал на вход 27 поступает в служебном такте (п +3) каждого.цикла. Сигнал на вход 29 поступает в последнем информационном такте (п + 2) каждого цикла. Сигнал на вход 34 поступает в тактах с четвертого по шестой. Сигнал на входе 36 имеет передний фронт на границе шестого и седьмого тактов. Например, можно иметь его .равным единице в течение седьмого такта.

Величина задерж.ки элементов 14, 24 и 31 выбирается не менее пяти времен срабатывания триггера, но не более одного такта.

Устройство для деления в избыточ-. ном коде работает следующим образом.

Делимое, делитель и частное представлены в избыточном четверичном коде, цифры которого кодируются еле-. дующим образом:

О - 000 - 1 - 111 +1-001 - 2 - 110

+2 - 010 +3 - 011

Остальные коды - запретные, т.е. четверичная цифра представляется в виде двоичной триады, старпшй разряд которой кодирует знак цифры, второй и первый разряды - саму цифру. Перед началом деления делитель

0

5

0

5

0

5

31280612

сывается с входа 1 в регистр 2 течение всей операции хранится ом регистре в динамике. Тригге1 и 13, предварительно сброшенсигналом по входу 15, элемент 12, элемент 14 задержки форми- знак делителя. Б первом цикле тель поступает на выходы регистра 2. проходят нулевые разряды,триггеры 13 остаются в нуле. Как только JQ ыходах регистра 2 возникает старразряд, Ьтличный от нуля, его овый разряд поступает на открыединичный вход триггера 11, так триггер 13 находится в нуле.

в су

су ИЛ ны ум по Си пок

три эти 33 в J5 В к пос инв пис пос Есл дов Р0 ста Р1 ся обр тел Р1 ки, гис фор Циф цик пае дыв в с вхо ла пос 25,

Если знак -, триггер 11 переходит в состояние единица, если знак +, триггер 11 остается в нуле. Элемент 12 выявляет наличие разряда, отличного от нуля. Как только на выходе регистра 2 возникает разряд, отлич- ньш от нуля, сигнал элемента 12 перебрасывает триггер 13 в единицу.и через время, равное задержке элемента 14, вход триггера 11 закрывается

По завершении записи делителя в регистр 19 с входа 20 записывается делимое. Триггеры 25 и 26, предварительно сброшенные с входа 27,эле-

мент ИЛИ 23, элемент 24 задержки формируют знак делимого, который запоминается в триггере 26 аналогично формированию знака делителя.

По сигналу с входа 29 знак делимого переписывается в триггер 28. Остальные триггеры 8, 31, 32, 34 и регистр 40 находятся в нуле. Так как первый цикл операции деления ничем не отличается от любого другого цикла, рассмотрим выполнение некоторого i-ro цикла. Знак остатка Oj , сформированного в предыдущем цикле, в последнем информационном такте сигналом С „ , поступающим на

h + Z

ВХОД 29 устройства, переписывается в триггер 28. Схема 16 сравнения знаков сравнивает знаки делителя, поступающего из триггера 11, и остатка (из триггера 28) и формирует сигнал ЗР2, который поступает на преобразователь 18, и последний присваивает удвоенному делителю, сформированному блоком 10, требуемый знак. Начиная с первого такта на первый вход сумматора 21 поступает уд- военный делитель. Одновременно из регистра 19 на второй вход сумматора 21 поступает предыдущий остаток, сдвинутьй на один четверичный разряд

в сторону старших разрядов 0 . В сумматоре 21 формируется сумма Р1.

Значащие разряды четверичных цифр суммы Р1, объединенные элементом ИЛИ 30, поступают на первый единичный вход триггера 33 и логически умножаются на тактовый сигнал С. , поступающий с входа 34 устройства. Сигнал С присутствует до тех пор, пока на выходе сумматора 21 проходят

три старших разряда суммы Р1. Если эти три разряда равны нулю, триггер 33 (предварительно сброшенный в ноль в служебном такте) остается в нуле. В конце шестого такта по сигналу С, поступающему на вход 36 устройства, инверсия состояния триггера 33 пере- писывается в триггер 8 и с выхода, последнего считывается сигнал . Если хотя бы один из старших разрядов суммы Р1 отличен от нуля, то и в триггер 32 запишется знак старшего ненулевого разряда суммы- Р1. По сигналу С знак Р1 перепишется в триггер 35. Если , то преобразователь 6 не пропускает делитель на входы сумматора 9, сумма Р1 проходит через элемент 22 задержки, сумматор 9 и записывается в регистр 19. Формирователь частного формирует четверичную цифру частного. Цифра частного задерживается на один цикл в элементе 38 задержки, поступает на входы сумматора 39, где складывается с переносом, сформированным в следующем цикле, и поступает на входы регистра 40. По окончании цикла в служебном такте сигналом С , поступающим на вход 27, триггеры 25, 26, 32 и 33 сбрасываются в нуль.

Сумма Р1 является очередным остатком 0-4., . Так как задержка сум

маторов 9 и 21 равна одному такту, суммарная задержка остатка 0-, составит п + 2 такта, т.е. окажется на один такт меньше цикла. Поэтому к началу следующего цикла остаток Oj, поступит на йходы суммаатора 21 . сдвинутым на один разряд в сторону старших разрядов.

Если три старших разряда суммы Р1 не равны нулю, то . В триггере 32 формируется знак Р1, который по сигналу С переписывается в триггер 35. Схема 7 сравнения знаков сравнивает знаки делителя Р1. Преобразователь 6 присваивает требуемый знак делителю, поступающему на входы сумматора 9. В последнем формируется сумма Р2.

Сумма Р2 записывается в регистр 19 как очередной остаток. Формирователь 37 частного формирует очередной разряд частного. Как н в предыдущем случае сформированная цифра частного задерживается на один в элементе 38 задержки, в сумматоре 39 складывается с переносом следующего цикла и поступает на входы регистра 40. В служебном такте содержимое регистра 40 сдвигается на один такт в сторону старших разрядов, триггеры 25, 26, 32 и 33 обнуляются. Остаток 0. сдвигается на один разряд в сторону старших разрядов н вновь поступает на входы сумматора 21.

По выполнении таким образом (п + 1)-го цикла в регистре 40 окажется полноразрядное частное. Подавая п сигналов сдвига на тактовый вход регистра 40 частного, на выходе 41 устройства можно получить последовательный код частного старшими разрядами вперед.

Формула изобретения

Устройство для деления в избыточном коде, содержащее регистры делимого, делителя и частного, блок умножения на два, первьй преобразователь .в обратный код, два сумматора, две схемы сравнения знаков, два триггера, два элемента задержки,три элемента И, причем в устройстве входы делителя и делимого устройства соединены соответственно с устано- вочныьш входами регистров делителя и делимого, выходы второго и третьего разрядов регистра делителя соединены соответственно с вторым и первым разрядами входа блока умножения на два, разрядный выход первого преобразователя в обратный код соединен с входом первого слагаемого первого сумматора, разрядный выход которого соединен с информационным входом регистра делимого, выход пер вого триггера соединен с первыми входами первого, второго и третьего элементов И узла формирования частного, выход первого элемента И которого соединен через первьй элемент задержки с третьим разрядом входа слагаемого второго сумматора, разрядный выход суммы которого соедине

с информационным входом частного, выход которого является выходом частного устройства, первый тактовый вход которого соединен с тактовым

входом первого триггера, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит третий сумматор, второй преобразователь в обратный код, семь

триггеров, семь элементов задержки, узел формирования частного содержит два элемента ИЛИ, причем выходы первого и второго разрядов регистра делителя соединены через первый элемент

5 ИЛИ с единичным входом второго триггера, нулевой выход которого через второй элемент задержки соединен с первым единичным входом третьего триггера, выход которого соединен

0 с первыми входами первой и второй схем сравнения знаков, EЬLKoды которых соединены соответственно с выходами разрешения преобразования первого и второго преобразователей в

5 обратный код, второй единичный вход третьего триггера соединен с вькодом третьего разряда регистра делителя, выходы разрядов которого через третий и четвертьй элементы задержки

0 соединены с соответствующиш- разряда- и информационного входа первого преобразователя в аварийный код, разряды с четвертого по шестой информационного входа которого через пятый

5 элемент задержки соединены соответственно с разрядами с первого по третий информационного входа первого преобразователя в обратный код, вход блокировки которого соединен с еди0 ничным выходом четвертого триггера, нулевой выход которого соединен с вторыми входами первого и второго элементов И и с первым входом первого элемента ИЛИ узла формирования 45 частного, выход первого элемента ИЛИ,, первый вход первого элемента ИЛИ которого через первый элемент задержки соединены соответственно с вторым и первым разрядами входа 50 слагаемого второго сумматора, вход переноса которого соединен с выходом второго элемента ИЛИ узла формирования частного, первый разряд выхода третьего элемента задержки соединен

55 ( третьим разрядом входа блока умно- |жения на два, первый, второй и третий разряды выхода которого соединены с соответствующими разрядами информационного входа второго преоб

разователя в обратный код и через шестой элемент задержки соответственно с четвертым, пятым и шестым разрядами информационного входа второго преобразователя в обратный код, выход которого и выход регист- ра делимого соединены соответственно с входами первого и второго слагаемых третьего сумматора, выход которого через седьмой элемент задержки соединен с входом второго слагаемого первого сумматора, первый и второй разряды выхода которого соединены через второй элемент ИЛИ с единичным входом пятого триггера, нулевой выход которого через восьмой элемент задержки соединен с первым единичным входом шестого триггера, второй единичный вход и выход которого соединены соответственно с третьим разрядом выхода первого сумматора и с информационным входом первого триггера, нулевые входы второго и третьего триггеров соединены с первым входом сброса устройства, второй вход сброса которого соединен с нулевыми входами пятого, шестого, седьмого и восьмого триггеров первьй и второй разряды выхода третьего сумматора соединены через третий элемент ИЛИ с первым единич

O

5

0

0

5

ным входом седьмого триггера, инверс ный выход которого соединен информационным входом четвертого триггера и через девятый элемент задержки - с первым единичным входом восьмого триггера,второй единичный вход и выход которого соединены соответственно с третьим разрядом выхода третьего сумматора и с информационным входом девятого триггера, единичный выход которого соединен с вторым входом первой схемы сравнения знаков и с вторым входом третьего элемента И узла формирования част- Horof третий вход первого элемента И и второй вход первого элемента ИЛИ которого соединены с нулевым выходом девятого триггера, выход первого триггера соединен с вторым входом второй схемь сравнения знаков, второй единичный вход седьмого триггера соединен с вторым тактовьм входом устройства, третий тактовый вход которого соединен с тактовыми входами четвер ого и девятого триггеров, а также в узле формирования частного выходы второго и третьего элементов И соедине - ны соответственно с первым и вторым входами второго элемен - та ИЛИ.

г

s

Редактор А.Лежнина

Составитель А.Клюев

Техред Л.Олейник Корректор М.Максимишинец

Заказ 7067/54Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фа г. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство для деления чисел в системе остаточных классов | 1985 |

|

SU1287152A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

Изобретение относится к области вычислительной техники и может быть использовано,в специализированных процессорах. Целью изобретения явля- ется сокращение аппаратурных затрат; Поставленная цель достигается тем, что устройство для деления в избыточном коде содержащее регистры делимого, делителя и частного, блок умножения на два, первьй преобразователь в обратный код, два сумматора, две схемы сравнения знаков, два триггера, два элемента задержки, три элемента И и узел формирования частного, содержит третш сумматор, второй преобразователь в обратный код, семь триггеров, семь элементе задержки, 2 ил.

| Фоторегистратор | 1976 |

|

SU580544A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1984-07-04—Подача