Изобретение относится к вычислительной технике, а именно к цифровым вычислительным устройствам последова тельно-параллельного действия, и может быть использовано в однородных вычислительных системах. Известно устройство для деления чисел, содержащее сумматор делимого, регистр делителя, сумматор делимого, регистр сдвига, сумматор частного, три блока передачи кодов 1 . Недостаток устройства - низкое быстродействие, малый диапазон представления чисел. Известно также делительное устрой ство без восстановления остатка, содержащее регистр частного, регистр делителя, сумматор, схему анализа знаков, логические элементы 2. Недостаток такого устройства - ни кое быстродействие и малый диапазон представления чисел. Наиболее близким к предлагаемому является устройство для деления, содержащее регистр делителя,два сумматора, вспомогательный регистр, регистр сдвига, регистр частного, блок управления, логические элементы з. К недостаткам этого устройства также следует отнести низкое быстродействие и малый диапазон представления чисел. Цель изобретения - повышение быстродействия, увеличение диапазона представления чисел. Поставленная цель достигается тем, что устройство для деления с плавающей запятой, содержащее регистр делителя, два комбинационных сумматора, элементы И, ИЛИ, ИЛИ-НЕ, вспомогательный регистр, входы которого соединены с разрядными выходами первого комбинационного сумматора, входы первой группы которого соединены с выходами второго комбинационного сумматора соответственно, содержит преобразователь кода порядка частного в избыточный код, триггер управления, два элемента задержки, два элемента И-ИЛИ, причем первый и второй входы второго комбинационного сумматора, которые являются входами знакоразрядных кодов устройства, соединены соответственно с первым и вторым входами элемента ИЛИ,выход которого соединен соответственно с первыми входами первого и второго элементов И, вторые входы которорых соединены соответственно с входами выделения мантиссы порядка устройства, выходы первого

и второго элементов И соединены с информационными входами первой группы второго комбинационного сумматора, информационные входы второй группы которого соединены со сдвигом на один разряд в сторону старших разрядов с выходами вспомогательного регистра, входы второй группы первого комбинационного сумматора соединены с выходами регистра делителя, выходы четырех старших разрядов первого комбинационного сумматора соединены соответственно со входами с первого по четвертый преобразователя кода порядка частного в избыточный код, первый и второй выходы которого соединены соответственно с первыми входами первых групп первого и второго элементов И-ИЛИ, третий выход преобразователя порядка частного в избыточный код соединен со входом старшего знакового разряда вспомогательного регистра, выходы двух младших знаковых и трех старших информационных разрядов первого комбинационного сумматора соединены соответственно со входами с первого по пятый узла выделения мантиссы частного, шестой вход которого соединен с выхрдом старшего знакового разряда регистра делителя, выходы узла выделения мантиссы частного соединены соответственно с первым и вторым входами первого элемента ИЛИ-НЕ, со входами первого и вт-орого элементов задержки и с первыми входами вторых групп первого и второго элементов И-ИЛИ, выходы первого и второго элементов задержки соединены соответственно с управляющими входами первого комбинационного сумматора, с первым и вторым входами второго элемента ИЛИ-«Е и с первыми входами третьих групп первого и второго элементов И-ИЛИ, вторые входы вторых и третьих групп которых соединены с выходом триггера управления, единичный вход которого соединен со входом четверто группы второго элемента И-ИЛИ и с выходом третьего элемента И, первый и второй входам которого соединены соответственно с выходами первого и второго элементов ИЛИ-НЕ, а третий вход соединен со входом нормализации мантиссы результата вычисления устройства, нулевой вход триггера управления соединен со входом младшего знакового разряда регистра делителя и входом сброса в нуль устройства, вторые входы первых групп первого и второго элементов И-ИЛИ и третьи входы вторых и третьих групп первого и второго элементов Я-ИЛИ соединены соответственно со вторыми входами второго и первого элементов И/ вход младшего информационного разряда регистра делителя соединен со входом записи порядка и мантиссы устройства вход третьего информационного разрядэ регистра делителя соединен со входом вьодачи порядка устройства, вход одиннадцатого информационного разряда регистра делителя соединен со входом вьщачи мантиссы устройства.

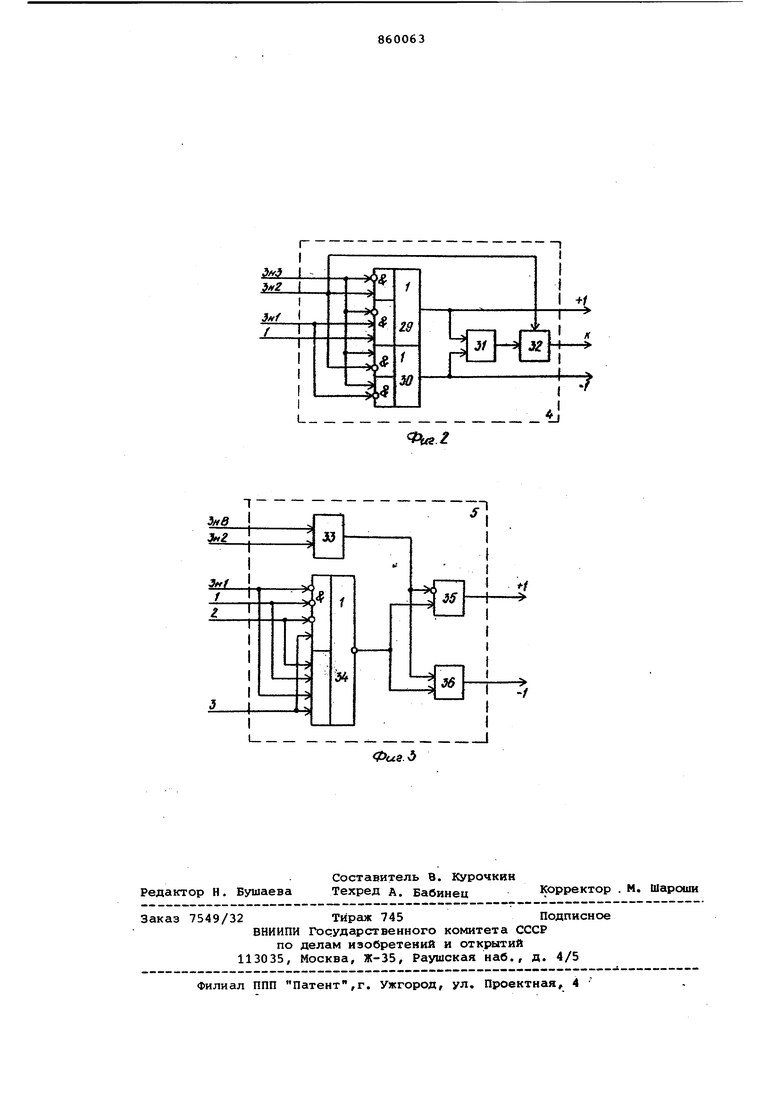

Преобразователь кода порядка частного в знакоразрядный код содержит два элемента И-ИЛИ, элемент ИЛИ и сумматор по модулю два, причем первы вход преобразователя соединен соответственно с первыми входами первых и вторых групп первого и второго элементов И-ИЛИ, выходы которых соединены соответственно с первым и вторым выходами преобразователя, и с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом сумматора по модулю два, второй вход которого соединен со вторым входом первой группы второго элемента И-ИЛИ а выход соединен с третьим выходом преобразователя, второй вход которог соединен со вторым входом первой группы первого элемента И-ИЛИ, трети вход преобразователя соединен со вторыми входами вторых групп первого и второго элементов И-ИЛИ, четвертый вход преобразователя соединен с третим входом второй группы первого элемента И-ИЛИ .

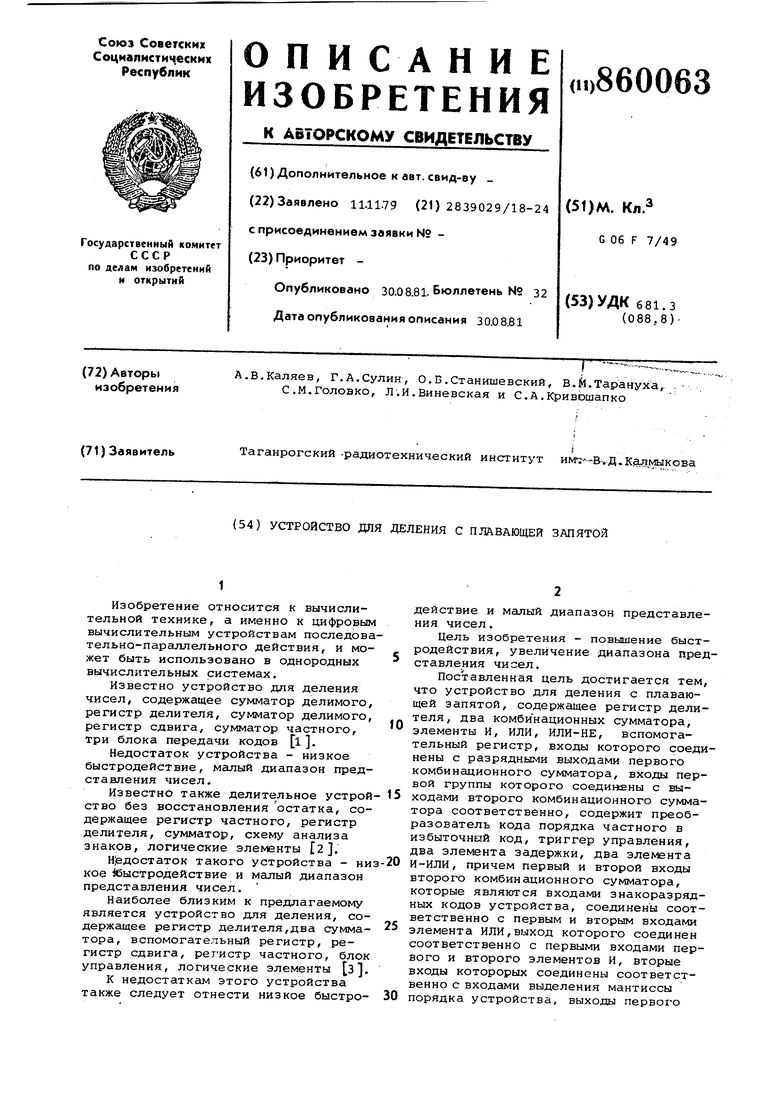

Узел выделения мантиссы частного содержит сумматор по модулю два,| элемент И-ИЛИ-НЕ, два элемента И, причем входы первой и второй групп элемента И-ИЛИ-НЕ соединены со вторым, третьим, четвертым и пятым входами узла, а выход соединен с первым входами первого и второго элементов И, вторые входы которых подключены к выходу сумматора по модулю два, а выходы соединены соответственно с первым и вторым выходами узла,входы сумматора по модулю два соединены с первым и шестым входами узла.

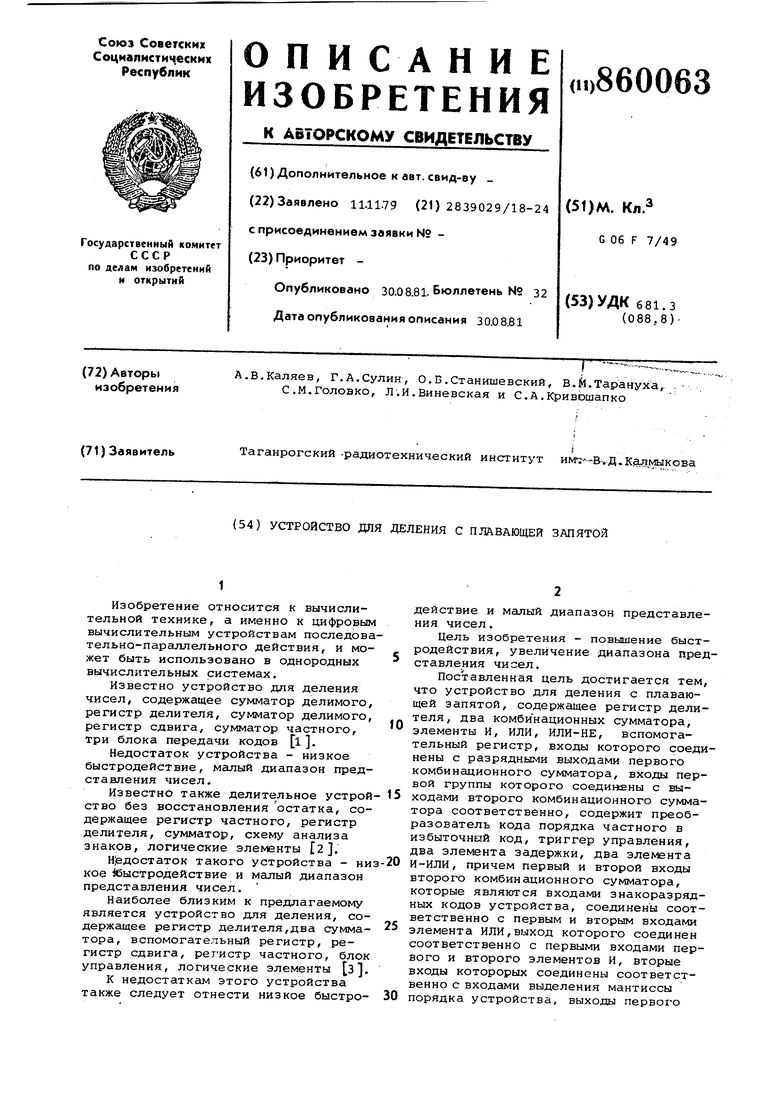

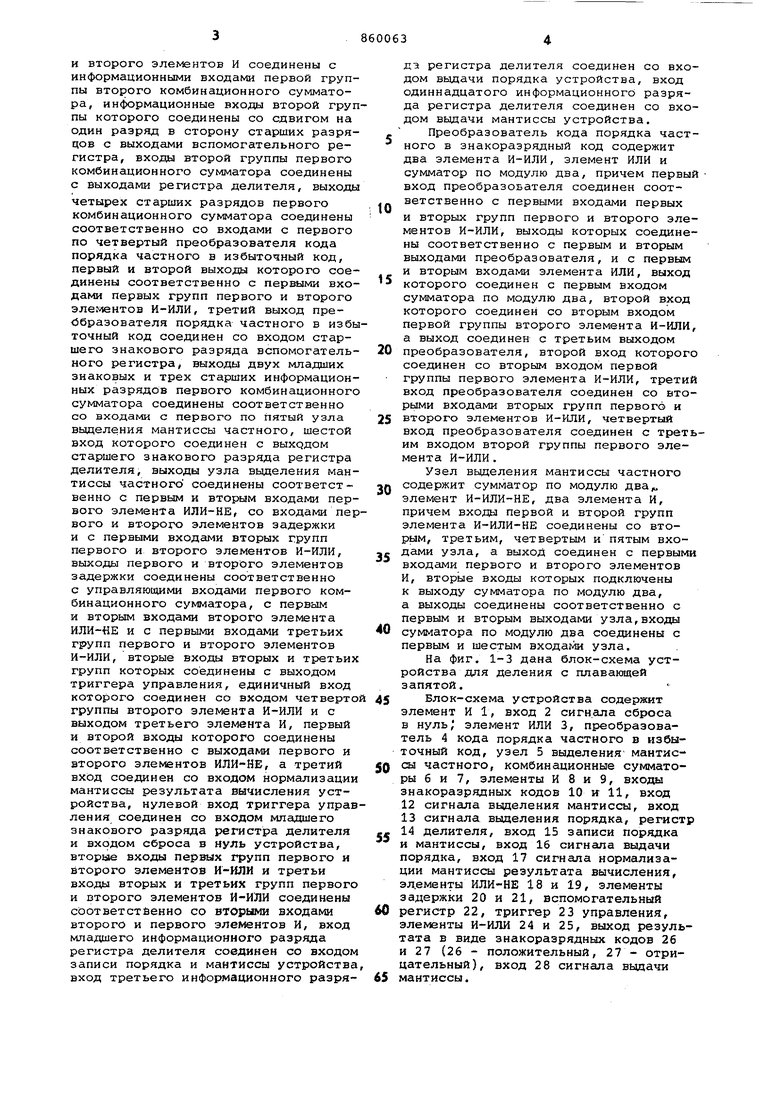

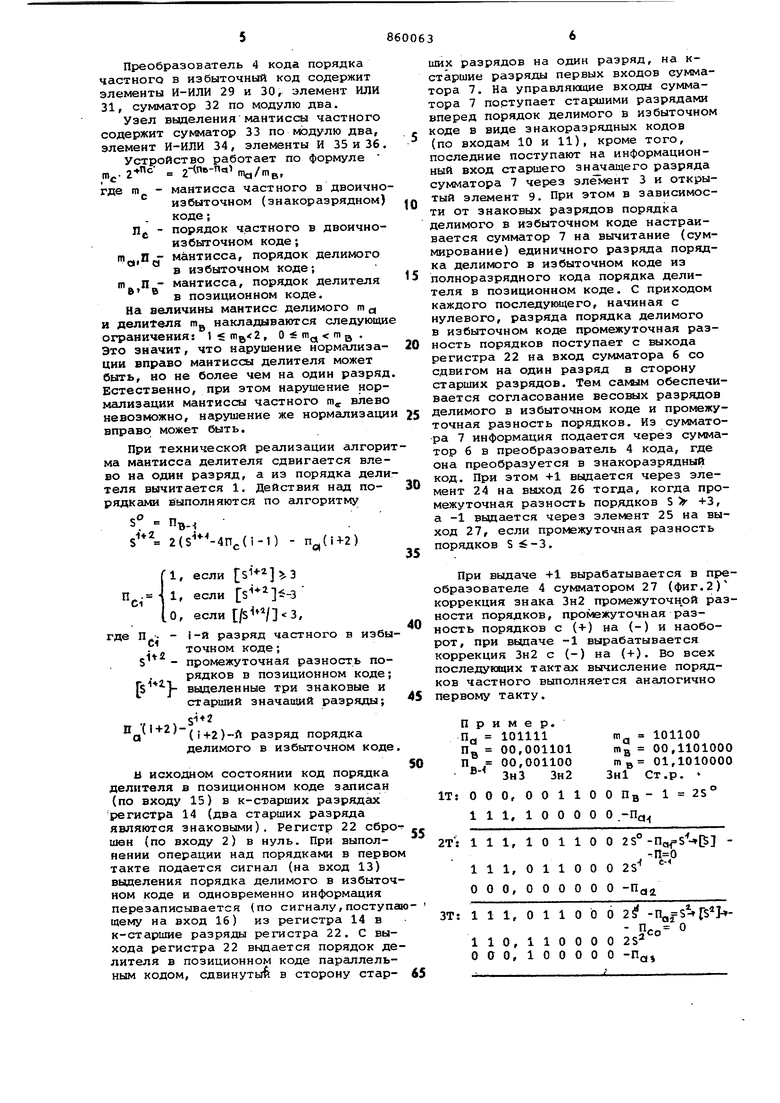

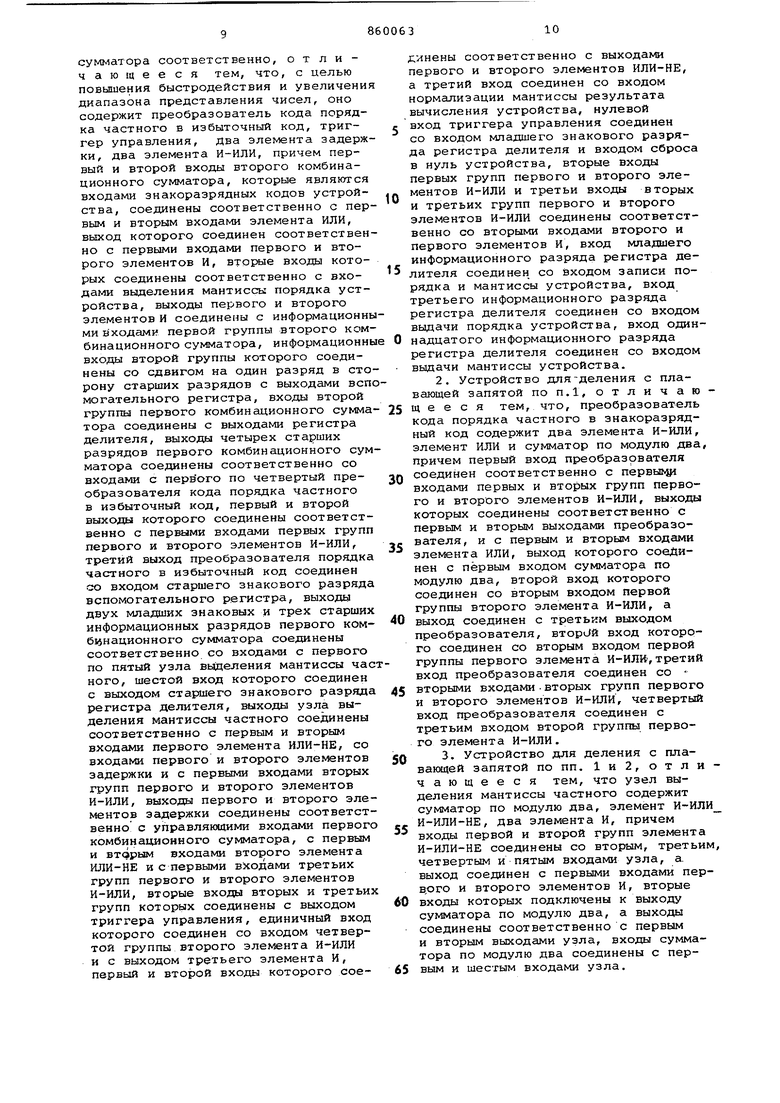

На фиг. 1-3 дана блок-схема устройства для деления с плавающей запятой.

Блок-схема устройства содержит элемент И 1, вход 2 сигн.ала сброса в нуль, элемент ИЛИ 3, преобразователь 4 кода порядка частного в избыточный код, узел 5 выделения- мантиссы частного, комбинационные сумматоры 6 и 7, элементы И 8 и 9, входы знакоразрядных кодов 10 и 11, вход

12сигнала вьиеления мантиссы, вход

13сигнала выделения порядка, регист

14делителя, вход 15 записи порядка и мантиссы, вход 16 сигнала выдачи порядка, вход 17 сигнала нормализации мантиссы результата вычисления, эдементы ИЛИ-НЕ 18 и 19, элементы задержки 20 и 21, вспомогательный регистр 22, триггер 23 управления, элементы И-ИЛИ 24 и 25, выход результата в виде знакоразрядных кодов 26

и 27 (26 - положительный, 27 - отрицательный), вход 28 сигнала выдачи мантиссы. Преобразователь 4 кода порядка частного в избыточный код содержит элементы И-ИЛИ 29 и 30, элемент ИЛИ 31, сумматор 32 по модулю два. Узел вьаделения мантиссы частного содержит сумматор 33 по модулю два, элемент И-ИЛИ 34, элементы И 35 и 36. Устройство работает по формуле тс- . где m - мантисса частного в двоично избыточном (знакораэрядном) П - порядок частного в двоичноизбыточном коде; 1Т1„,П.г мантисса, порядок делимого в избыточном коде; m ,П - мантисса, порядок делителя в позиционном коде. Иа величины мантисс делимого m и делителя т накладываются следующи ограничения: , О m m . Это значит, что нарушение нормапизации вправо мантиссы делителя может быть, но не более чем на один разряд Естественно, при этом нарушение нормализации мантиссы частного т влево невозможно, нарушение же нормализаци вправо может быть. При технической реализации алгори ма мантисса делителя сдвигается влево на один разряд, а из порядка дели теля вычитается 1. Действия над порядками выполняются по алгоритму 2(5 -4Пс{ -П - п() 1, если si-- j.a 1, если О, если , - i-й разряд частного в избы точном коде; промежуточная разность выделенные три знаковые и старший значащий разряды; а (i+2)-ft разряд порядка делимого в избыточном коде в исходном состоянии код порядка делителя в позиционном коде записан (по входу 15) в к-старших разрядах регистра 14 (два старших разряда являются знаковыми). Регистр 22 сбро шен (по входу 2) в нуль. При выполнении операции над порядками в перво такте подается сигнал (на вход 13) выделения порядка делимого в избыточ ном коде и одновременно информация перезаписывается (по сигналу,поступ щему на вход 16) из регистра 14 в к-старшие разряды регистра 22. С выхода регистра 22 вндается порядок де лителя в позиционном коде параллельным кодом, сдвинутый в сторону старших разрядов на один разряд, на кстаршие разряды первых входов сумматора 7. На управляющие входы сумматора 7 поступает старшими разрядами вперед порядок делимого в избыточном коде в виде знакораэрядных кодов (по входам 10 и 11), кроме того, последние поступают на информационный вход старшего значащего разряда сумматора 7 через элемент 3 и открытый элемент 9, При этом в зависимости от знаковых разрядов порядка делимого в избыточном коде настраивается сумматор 7 на вычитание (суммирование) единичного разряда порядка делимого в избыточном коде из полноразрядного кода порядка делителя в позиционном коде. С приходом каждого последующего, начиная с нулевого, разряда порядка делимого в избыточном коде промежуточная разность порядков поступает с выхода регистра 22 на вход сумматора 6 со сдвигом на один разряд в сторону старишх разрядов. Тем caiuUM обеспечивается согласование весовых разрядов делимого в избыточном коде и промежуточная разность порядков. Из сумматора 7 информация подается через сумматор 6 в преобразователь 4 кода, где она преобразуется в знакоразрядный код. При этом +1 выдается через элемент 24 на выход 26 тогда, когда промежуточная разность порядков 5 +3, а -1 вьщается через элемент 25 на выход 27, если промежуточная разность порядков S -3. При выдаче +1 вырабатывается в преобразователе 4 сумматором 27 (фиг.2) коррекция знака Зн2 промежуточнрй разности порядков, промежуточная разность порядков с (+) на (-) и наоборот, при ВЕадаче -1 вырабатывается коррекция Зн2 с (-) на (+). Во всех последующих тактах вычисление порядков частного выполняется аналогично первому такту. Пример. Год 101100 Пд 101111 тв 00,1101000 П 00,001101 П 00,001100 т 01,1010000 ° ЗнЗ Зн2 Зн1 Ст.р. IT: О О О, О О 1 1 О О Пв - 1 25° 111,100000 -Псц 2Т: 1 1 1, 1 О 1 1 О О 2S°-nofS- 5 1 1 1, О 1 1 О О О 000, 000000 -Па5 ЗТ: 111, 0110002 -no Псо О 110, 110000 25 000, 100000 -Па, 4Т: 1 1 1,О 1 О О О Оs- О 110,10000025 111,1-Па4 5Т: 1 1 О,О О О О О , 000,0000002С$ -4Пс2) О О О,1-ПОУ 000,1000002 ()-Па5 с-а Гс51зЧГзТ -г, 001, 000000 1, 1 1, 1-П 7Т: 000, 100000 О 8Т: О О 1, О О О О О О -Пс5 О 010, 000000 -Псб О По окончании выполнения операции над порядками снимается сигнал, поступающий на вход 13, и подается сигнал (на вход 9) вьщеления мантис сы операнда. Вычисление и нормализация мантиссы частного осуществляется по алгоритму 4 , «-аг О е 2еЧ т( i+2 ). 2-- Шц. т..; 11,если {Знтц+Зн26) ; 1,если (3Hnig+Зн28) -, О,если /2 f 2-; если О А т. 4 О ; если т, со о л га.. О ; «г-1о; со ° 0; й если т О л тс 0; где f- 1-е значение остатка; вьоделенные два знаковые и три старших значащих разряда т( I-Н )-(i+ 1 )-й разряд мантиссы част ного; вычисленное значение мантисс частного; т нормализованное значение ман тиссы частного; m, нулевой и первый разряды ман тиссы частного; дПд - приращение порядка частного В исходном состоянии код мантиссы делителя записан (по входу 15) в регистр 14. Регистр 22 и триггер 23 управления сброшены (по входу 2) в нуль. При выполнении операции делени мантисса делимого/мантисса делителя в каждом такте выдается из регистра 14 (по сигналу, поступающему на вход 28) манстисса делителя, которая подается параллельным кодом на одни входы сумматора 6. На управлянадие входа сумматора 7 поступает старши1Сш разрядами вперед мантисса делимого в виде знакоразрядного кода (по входам 10 и 11). Кроме того, этот же код поступает на информационный вход (3) сумматора 7 с уменьшенным весом в три раза, т.е. . В сумматоре 7 выполняется операция ,()- 2 Значение остатка б поступает с выхода регистра 22 на вход сумматора 6 со сдвигом на один разряд в сторону старших разрядов. Результат сумматора 7 поступает на вторые входы сумматора 6. На управляющие входы сумматора 6 поступа;ет инверсный знакоразрядный код мантиссы частного. Результат, два знаковых и три значащих разряда, подается из сумматора 6 на схему 5. Кроме того, на эту же схему поступает знак мантиссы делителя из выхода регистра 14. В схеме 5 (фиг, 3) анализируются два знаковых и три старших значащих разряда остатка, и на основании анализа формируется частное в виде знакоразрядного кода. При этом +1 выдается элементами 33,34 и 35, когда (Знтр© 3H2t-)Х02-€Ч 2- , а -1 выдается элементами 33, 34 и 35, если (Знпд © )лр2еЧЗ /2- . В остальных случаях выдается нуль. Нормализация вычисленной мантиссы т осуществляется во втором такте TIO сигналу, поступсцощему на вход 17. Если nij.jj О и iflc4 элементом 1 выдается отрицательное приращение порядка (йПс -1), которое поступает на выход 27 через элемент 25. По прира щению лПс переключается триггер 23 управления в единичное состояние и потенциалом открываются соответствующие схемы И элементов 24 и 25. При этом выключаются элементы 20 и 21 задержки, что равносильно увеличению веса вычисленной мантиссы т в два раза. Введение в устройство новых элементов и связей позволяет увеличить диапазон изменения чисел, за счет выполнения операций над числами с плавающ ей запятой,, например при шестиразрядном порядке числа могут изменяться в диапазоне от 2 до , повышается быстродействие в два раза за счет совмещения операций сдвига и суммирования. Кроме того, сокращается расход оборудования операции как над мантиссами, так и над порядками выполняются на одних и тех же сумматорах , Использование изобретения позволяет повысить эффективность однородных вычислительных структур. Формула изобретения 1. Устройство для деления с плавающей запятой, содержащее регистр делителя, два комбинационных сумматора, элементы И, ИЛИ,-ИЛИ-НЕ, вспомогательный регистр. Входы которого соединены с разрядными выходами первого комбинационного сумматора,входы первой группы которого соединены с выходами второго комбинационного сумматора соответственно, отличающееся тем, что, с целью повышения быстродействия и увеличени диапазона представления чисел, оно содержит преобразователь кода порядка частного в избыточный код, триггер управления, два элемента задерж ки, два элемента И-ИЛИ, причем первый и второй входы второго комбинационного сумматора, которые являются входами знакоразрядных кодов устройства, соединены соответственно с пер вым и вторым входами элемента ИЛИ, выход которого соединен соответствен но с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с входами выделения мантиссы порядка устройства, выходы первого и второго элементов И соединены с информационн ми входами первой группы второго ком бинационного сумматора, информационн входы второй группы которого соединены со сдвигом на один разряд в сто рону старших разрядов с выходами всп могательного регистра, входы второй группы первого комбинационного сумма тора соединены с выходами регистра делителя, выходы четырех старших разрядов первого комбинационного сум матора соединены соответственно со входами с первого по четвертый преобразователя кода пор51дка частного в избыточный код, первый и второй выходы которого соединены соответственно с первыми входами первых групп первого и второго элементов И-ИЛИ, третий выход преобразователя порядка частного в избыточный код соединен со входом старшего знакового разряда вспомогательного регистра, выходы двух младших знаковых и трех старших информационных разрядов первого комб1(}надионного сумматора соединены соответственно со входами с первого по пятый узла выделения мантиссы час ного, шестой вход которого соединен с выходом старшего знакового разряда регистра делителя, выходы узла выделения мантиссы частного соединены соответственно с первым и вторым входс1ми первого элемента ИЛИ-НЕ, со входами первого и второго элементов задержки и с первыми входами вторых групп первого и второго элементов И-ИЛИ, выходы первого и второго элементов задержки соединены соответственно с управляющими входс1ми первого комбинационного сумматора, с первым и вторым входалщ второго элемента ИЛИ-НЕ и с первыми входами третьих групп первого и второго элементов И-ИЛИ, вторые входы вторых и третьих групп которых соединены с выходом триггера управления, единичный вход которого соединен со входом четвертой группы второго элемента И-ИЛИ и с выходом третьего элемента И, первый и второй входы которого соед; 1нены соответственно с выходами первого и второго элементов ИЛИ-НЕ, а третий вход соединен со входом нормализации мантиссы результата вычисления устройства, нулевой вход триггера управления соединен со входом младшего знакового разряда регистра делителя и входом сброса в нуль устройства, вторые входы первых групп первого и второго элементов И-ИЛИ и третьи входы вторых и третьих групп первого и второго элементов И-ИЛИ соединены соответственно со вторыми входами второго и первого элементов И, вход младшего информационного разряда регистра делителя соединен со входом записи порядка и мантиссы устройства, вход третьего информационного разряда регистра делителя соединен со входом выдачи порядка устройства, вход одиннадцатого информационного разряда регистра делителя соединен со входом выдачи мантиссы устройства. 2.Устройство для-деления с плавающей запятой ПОП.1, отличающееся тем, что, преобразователь кода порядка частного в знакоразрядный код содержит два элемента И-ИЛИ, элемент ИЛИ и сумматор по модулю два, причем первый вход преобразователя соединен соответственно с первыли входами первых и вторых групп первого и второго элементов И-ИЛИ, выходы которых соединены соответственно с первым и вторым выходами преобразователя, и с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом сумматора по модулю два, второй вход которого соединен со вторым входом первой группы второго элемента И-ИЛИ, а выход соединен с третьим выходом преобразователя, второй вход которого соединен со вторым входом первой группы первого элемента И-ИЛН,третий вход преобразователя соединен со вторыми входами.вторых групп первого и второго элементов И-ИЛИ, четвертый вход преобразователя соединен с третьим входом второй группы первого элемента И-ИЛИ. 3.Устройство для деления с плавакмцей запятой по пп. 1и2, отличающееся тем, что узел выделения мантиссы частного содержит сумматор по модулю два, элемент И-ИЛИ И-ИЛИ-НЕ, два элемента И, причем входы первой и второй групп элемента И-ИЛИ-НЕ соединены со вторым, третьим, четвертым и пятым входами узла, а. выход соединен с первыми входами перв,ого и второго элементов И, вторые входы которых подключены к выходу сумматора по модулю два, а выходы соединены соответственно с первым и вторым выходами узла, входы сумматора по модулю два соединены с первым и шестым входами узла.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 549808, кл. G 06 F 7/52, 1975.

2.Папорнов А.А. Логические основы ЦВТ. Советское радио, 1972,

с. 234-236.

3.Авторское свидетельство СССР

.№ 556435 , кл. G 06 F 7/ь2, 1975 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Вычислительное устройство | 1983 |

|

SU1173411A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

г /5 f ,у

I

t«/

Фи.9 Ь

Авторы

Даты

1981-08-30—Публикация

1979-11-11—Подача