ш

t1283804

Изобретение относится к вычислительной технике и может быть испель- зовано в устройствах преобразования информации.

Цель изобретения - упрощение и повышение разрешающей способности преобразования.

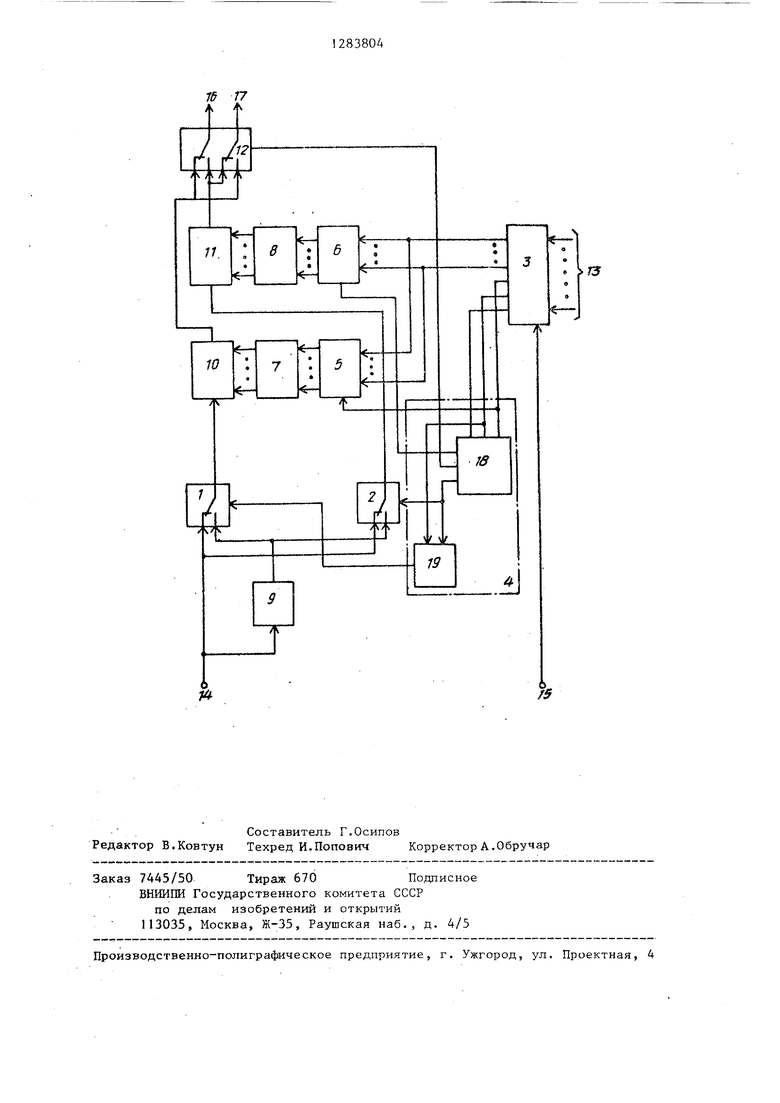

На чертеже схематически представен преобразователь.

Преобразователь содержит первый 1 и второй 2 переключатели, регистр 3 кода аргумента, селектор 4 октанта, первый 5 и второй 6 преобразователи .прямого кода в дополнительный, первый 7 и второй 8 блоки постоянной памяти, инвертор 9, первый 10 и второй 1I умножающие цифроанапого- вые преобразователи, выходной коммутирующий блок 12, информационный вход 13, вход 14 преобразуемЬго напряжения, синхронизирующий вход 13, синусный 16 и косинусный 17 выходы. Селектор 4 содержит трехразрядный блок 18 сложения с единицей и элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ.

is

20

25

Преобразователь работает следуюим образом,

В первом, четвертом, пятом и осьмом октантах блок 7 используется для формирования синусной, а блок 8 - для формирования косинусной заисимости. В остальных октантах они еняются ролями. Это обеспечивается выходным коммутирующим блоком 12. Преобразователи 5 и прямого кода в дополнительный обеспечивают формирование нарастающих участков зависимостей, если код передается без изменения, и убывающих участков, если на выходе преобразователей формируется дополнительный код.

Дополнительный код формируется на выходе преобразователя 16 в четырех октантах, а на выходе преобразователя 17 - в нечетных октантах. Кроме того, за счет подачи инвертированного или неивертированного напряжений через переключатели 1 и 2 обеспечивается требуемое изменение знака синусной и косинусной функций за пол- ньй период изменения аргумента.

Цикл преобразования начинается с записи в регистр 3 очередного значения аргумента. Частота повторения циклов преобразования лимитируется временем установления сигналов на выходах преобраз&ателя и задается по синхронизирующему входу 15.

s

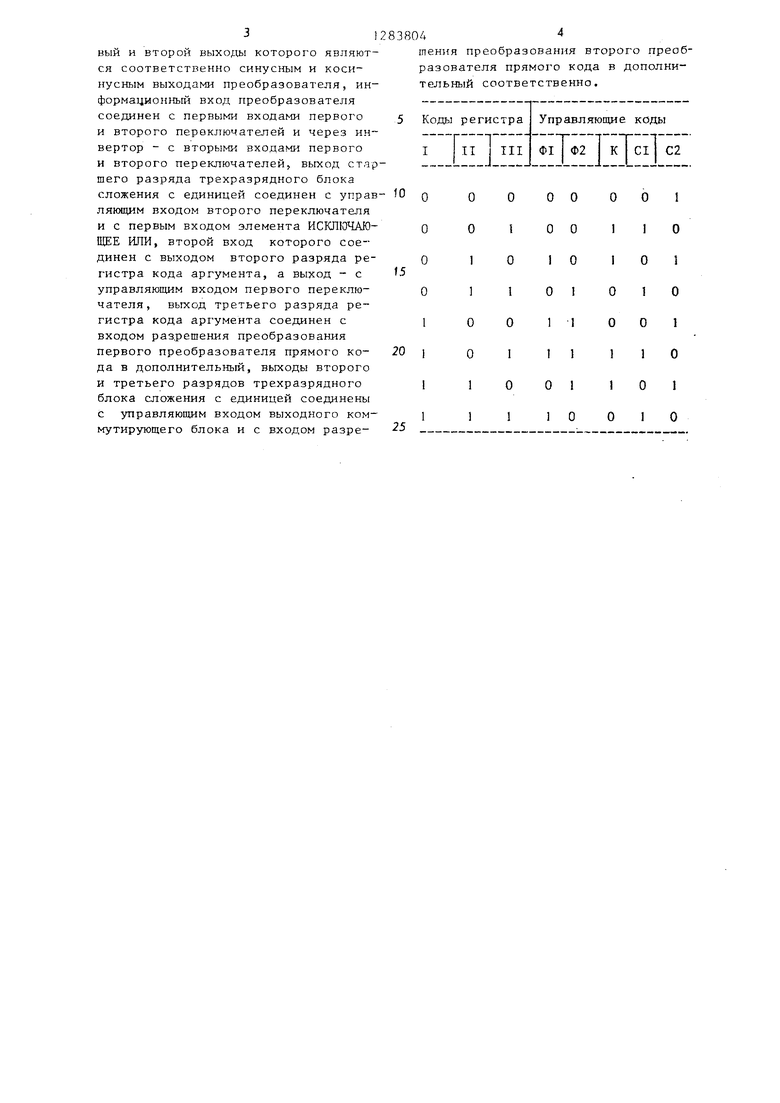

В таблице приведены значения управляющих сигналов в зависимости от номера октанта ( кода трех старших разрядов регистра 3),

В таблице римскими цифрами обозначены старшие разряды регистра 3, Ф1 и Ф2 - управляющие входы первого 1 и второго 2 переключателей соответственно, К - управляющий вход выходного переключающего блока, С1 и 02 - управляющие входы первого 5 и второго 6 преобразователей прямого кода в дополнительный.

Формула изобретения

0

5

5

0

СинуСИо-косинусный преобразователь, содержащий регистр кода аргумента, информационный вход которого является входом преобразователя, а вход записи соединен с синхронизирующим входом преобразователя, выходы трех старщих регистра соединены с входами селектора октанта, два умножающих цифроаналоговых преобразователя, ДБЯ блока постоянной памяти, первый у второй переключа- т ели, отличающийся тем, что, с целью упрощения и повы0 шения разрещающей способности преобразования, он содержит инвертор, два преобразователя прямого кода в дополнительный и выходной коммутирующий блок, содержаящй два переключателя, при этом селектор октанта содержит трехразрядный блок сложения с единицей и элемент ИСКЛЮЧАКЩЕЕ ИЛИ, входы разрядов трехразрядного блока сложения с единицей являются соот- ветствуюш 1ми входами селектора октанта, группа выходов младших разрядов регистра кода аргумента соединена с информационными входами первого и второго преобразователей пря5 мого кода в дополнительный, выходы которых соедине1Ш с входами соответствующего блока постоянной памяти, выходы которых соединены с кодовыми входами первого и второго умножающих

0 цифроаналоговых преобразователей соответственно, выход первого из которых соединен с первым входом первого и вторым входом второго переключателей выходного коммутирукг5 щего блока, а выход второго умножающего цифроаналогового преобразователя - с вторым входом первого и первым входом второго переключателей выходного коммутирующего блока, первый и второй выходы которого являются соответственно синусным и косинусным выходами преобразователя, ин- формацно}1нь й вход преобразователя соединен с первыми входами первого и второго переключателей и через инвертор - с вторыми входами первого и второго переключателей, выход стар шего разряда трехразрядного блока сложения с единицей соединен с управ ляющим входом второго переключателя и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго разряда регистра кода аргумента, а выход - с управляющим входом первого переключателя, выход третьего разряда регистра кода аргумента соединен с входом разрешения преобразования первого преобразователя прямого кода в дополнительный, выходы второго и третьего разрядов трехразрядного блока сложения с единицей соединены с управляющим входом выходного коммутирующего блока и с входом разре2838044

шения преобразования второго преобразователя прямого кода в дополнительный соответственно.

гз

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Многоканальный преобразователь угла поворота вала в код | 1987 |

|

SU1462478A2 |

| Синусно-косинусный преобразователь | 1987 |

|

SU1462367A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1213543A1 |

| Преобразователь угла поворота вала в код | 1979 |

|

SU860107A1 |

| ВСЕСОЮЗНАЯ f ПйТ:;йтно«|1Х1и{^:: H^^f | 1973 |

|

SU364098A1 |

| Синусно-косинусный кодовый преобразователь | 1972 |

|

SU464006A1 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU970417A1 |

| Преобразователь угол-код | 1973 |

|

SU458846A1 |

| Устройство для определения аргумента вектора | 1982 |

|

SU1023347A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования информации. Цель изобретения упрощение и првьппение разрешающей способности.преобразования. Преобразователь содержит два переключателя, регистр кода аргумента, селектор октанта, два преобразователя прямого кода в дополнительный, два блока постоянной памяти, два умножающих дифроаналоговых преобразователя, выходной коммутирующий блок. Селектор содержит трехразрядный блок слежения с единицей и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. За счет инвертирования преобразуемого напряжения, изменения кодов с прямого на дополнительный и переключения выходных каналов формируются синусная и косинусная зависимости на полном периоде изменения аргумента при хранеш и в блоках постоянной памяти ординат синуса и косинуса в пределах первого октанта 1. ил. сл 1чЭ 00 00 00

| Устройство для синусно-косинусного преобразования кода в напяжение | 1982 |

|

SU1089588A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1183989, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-02-28—Подача