дом первого коммутатора, выходом сброса первого триггера запроса, входом разрешения сброса первого счетчика и входом разрешения установки в нуль первого триггера повторного запроса, единичный выход которого соединен с третьим управляюш,им входом первого коммутатора, а нулевой выход соединен с вторыми входами первого и второго элементов И, входом разрешения сброса первого триггера запроса и четвертым управляющим входом первого коммутатора, первая и вторая группы выходов выбора канала регистра микрокоманд соединены с группами информационных входов первого и второго регистров выбора каналов соответственно, первый и второй выходы имитации ошибки регистра микрокоманд являются соответственно первым и вторым выходами имитируемой ошибки устройства, первый выход требования имитации регистра микрокоманд соединен с единичными входами первого триггера запроса и первого триггера повторного запроса и первыми информационными входами первого коммутатора, второй выход требования имитации регистра микрокоманд соединен с единичными входами второго триггера запроса и второго триггера повторного запроса и первым информационным входом второго коммутатора, группа выходов второго регистра выбора каналов соединена с группой управляющих входов демультиплексора выходной информации, группа выходов которого является группой выходов . последовательного кода устройства, выход второго коммутатора соединен с входом синхронизации второго регистра выбора каналов и входом синхронизации записи второго регистра сдвига, выход младшего разряда которого соединен с информационным входом демультиплексора выходной информации, нулевой выход второго триггера

запроса соединен с первым управляющим входом второго коммутатора, единичный выход второго триггера запроса соединен с входами разрешения сдвига второго регистра сдвига, разрешения счета второго счетчика и разрешения записи единицы второго триггера повторного запроса, единичный выход которого соединен с вторым управляющим входом второго коммутатора, нулевой выход второго триггера запроса соединен с третьими входами первого и второго элементов И, третьим управляющим входом второго коммутатора и входом разрешения установки в нуль второго триггера запроса, выход переполнения второго счетчика соединен с нулевым входом первого триггера запроса, входом разрешения установки в нуль второго триггера повторного запроса, входом разрешения сброса второго счетчика и четвертым управляющим входом второго коммутатора, вторая группа выходов мультиплексора выходной информации соединена с группой информационных входов второго регистра сдвига, вход старшего разряда которого соединен с шиной нулевого потенциала, вход первого разряда группы синхровходов устройства соединен с синхровходом первого регистра сдвига, счетными входами первого и второго счетчиков и входом синхронизации сдвига второго регистра сдвига, вход второго разряда группы синхровходов устройства соединен с вторыми информационными входами первого и второго коммутаторов, входами синхронизации установки в нуль первого и второго триггеров запроса, входом синхронизации регистра логических условий, вход третьего разряда группы синхровходов устройства соединен с входами сброса первого и второго счетчиков и нулевыми входами первого и второго триггеров повторного запроса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256025A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОБЪЕКТА КОНТРОЛЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, первый регистр выбора канала, регистр логических условий, первый и второй счетчики, мультиплексор выходной информации, мультиплексор адреса, первый и второй элементы И, причем группа выходов регистра логических условий соединена с первой группой, информационных входов мультиплексора адреса, группа выходов которого соединена с первой группой информационных входов регистра адреса, выходы регистра адреса соединены с группой адресных входов блока памяти микрокоманд, информационные входы которого соединены с группой информационных входов регистра микрокоманд, группы выходов немодифицируемых разрядов адреса очередной микрокоманды, управления мультиплексором адреса, управления мультиплексором выходной информации, выходного кода регистра микрокоманд соединены соответственно с второй группой информационных входов регистра адреса, второй группой информационных входов мультиплексора адреса, группой управляющих входов мультиплексора адреса, группой управляющих входов мультиплексора выходной информации, группой информационных входов мультиплексора выходной информации, первая группа выходов которого является группой выходов имитируемого объекта устройства, выход конца режима регистра микрокоманд соединен с управляющим входом мультиплексора адреса, выходы конца режима и выход конца программы регистра микрокоманд соединены соответственно с первым и вторым выходами группы выходов условий имитируемых устройств, группа входов устройства и группа входов задания режима устройства соединены соответственно с третьей и четвертой группами информационных входов мультиплексора адреса, первый и второй тактовые входы устройства соединены с первыми входами первого и второго элементов И соответственно, отличающееся тем, что, с целью повышения быстродействия, в него введены первый и второй регистры сдвига, второй регистр выбора канала, первый и второй триггеры запроса, первый и второй триггеры повтор(Л ного запроса, мультиплексор входной информации, демультиплексор выходной информации, первый и второй коммутаторы, причем группа выходов первого регистра выбора канала соединена с группой управляющих входов мультиплексора входной информации, выход которого соединен с информационным входом младшего разряда первого регистра сдвига, группа входов имитации последовательной работы устройства соединена 00 00 с группой информационных входов мультиплексора входной информации, единичный выход первого триггера запроса соединен 4 с входом разрешения счета первого счетчика, оо входом разрешения записи единицы первого триггера повторного запроса и входом разрешения сдвига первого регистра сдвига, группа выходов которого соединена с группой информационных входов регистра логических условий, нулевой выход первого триггера запроса соединен с первым управляющим входом первого коммутатора, выход которого соединен с входом синхронизации первого регистра выбора каналов, выход переполнения первого счетчика соединен с входом разрешения записи регистра логических условий, вторым управляющим вхо

1

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для имитации объекта контроля и управления в автоматизированных системах для контроля бортовых вычислительных и управляющих комплексов летательных аппаратов (ЛА).

Цель изобретения - повышение быстродействия устройства.

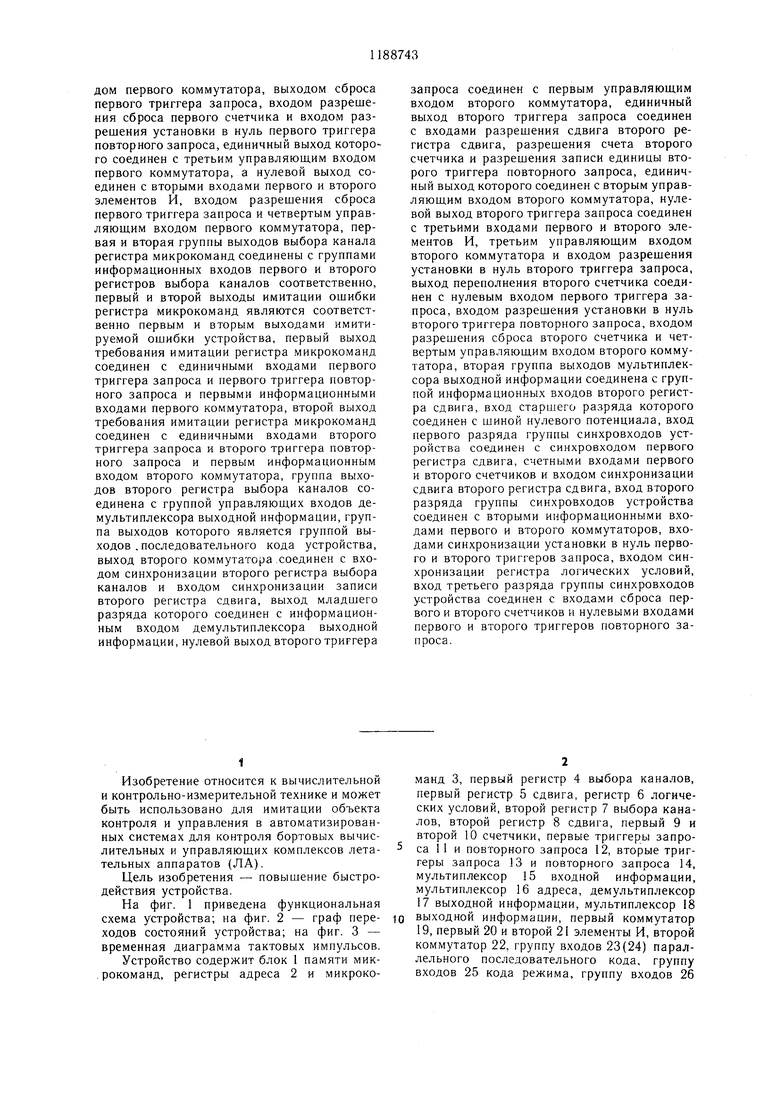

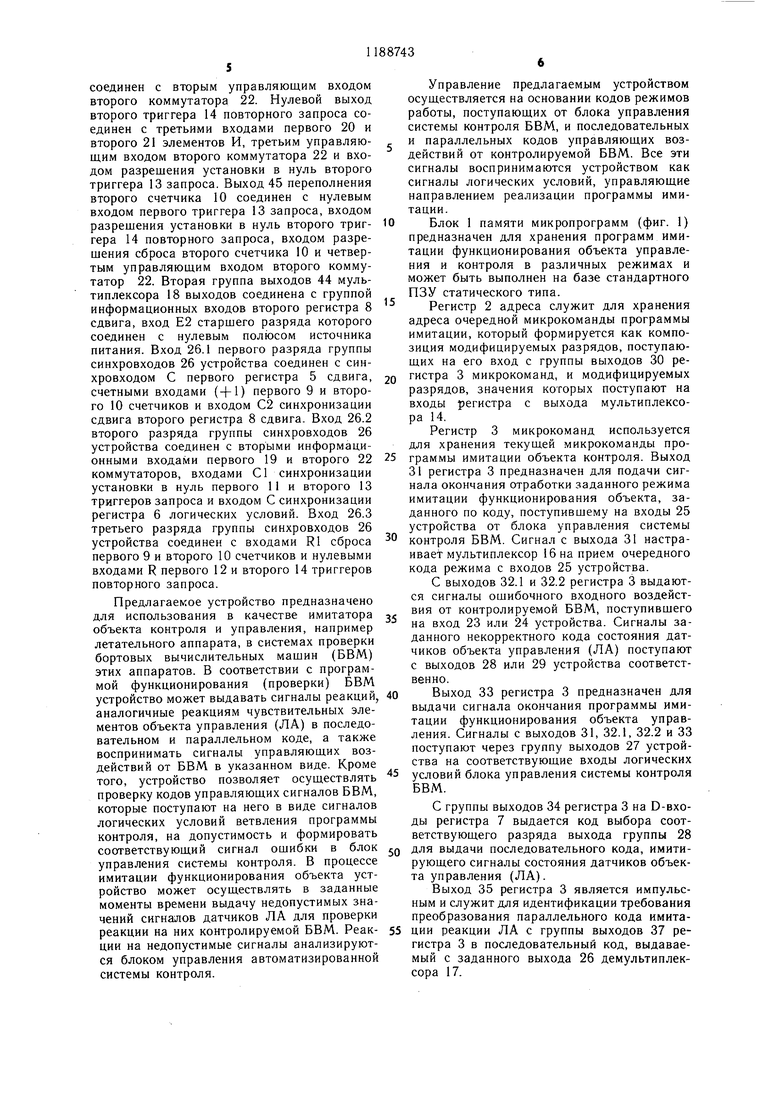

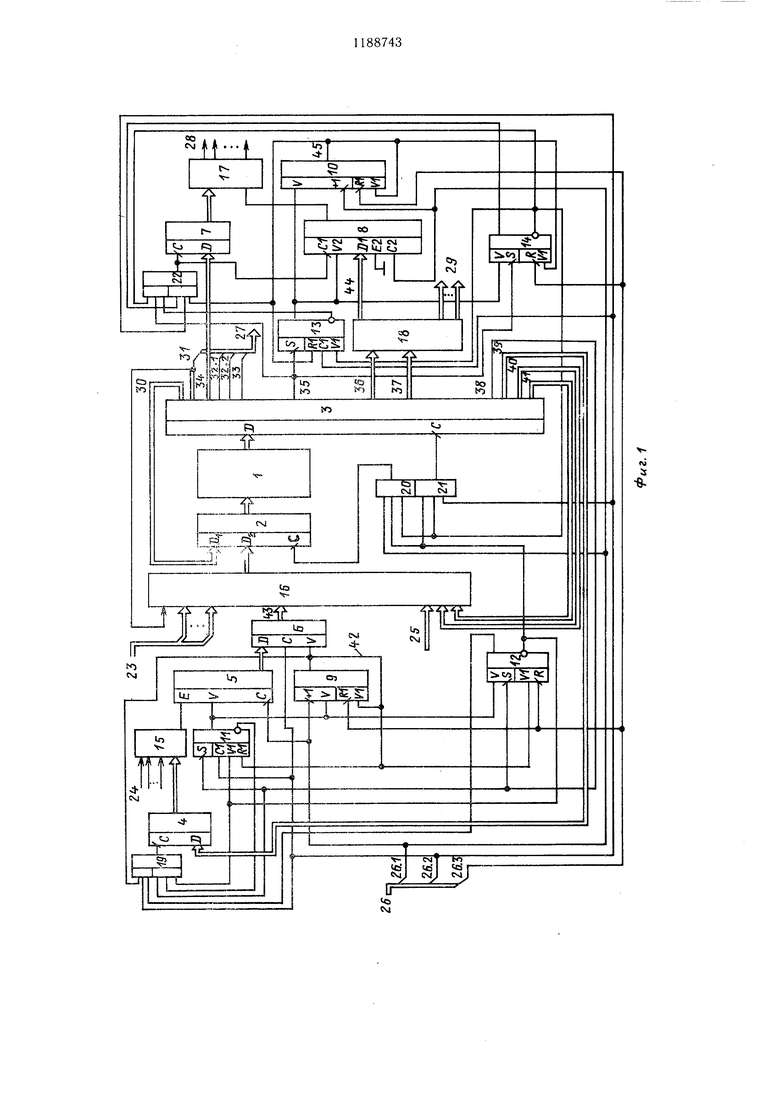

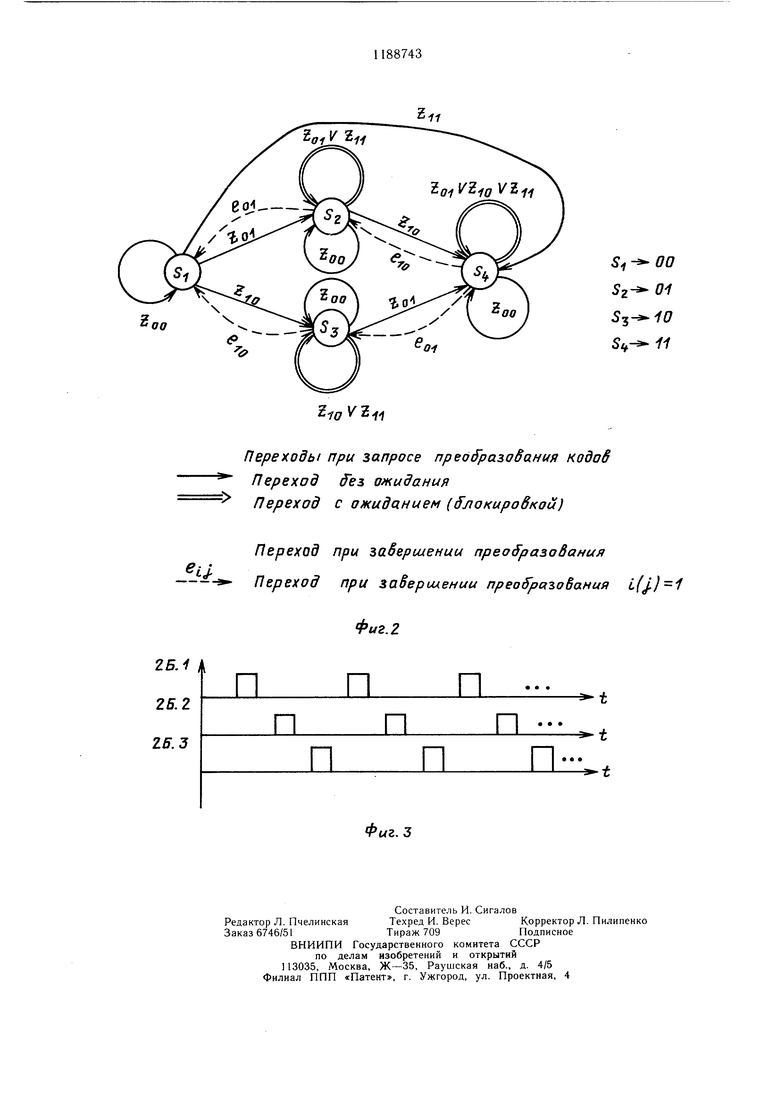

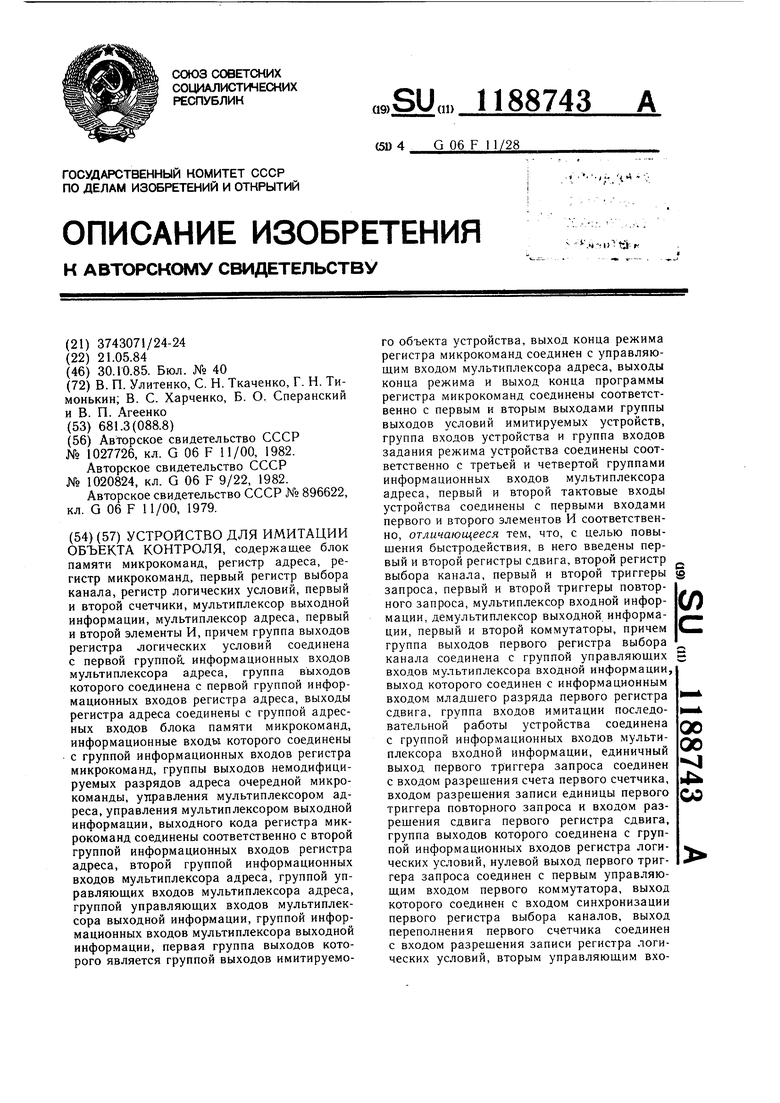

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - граф переходов состояний устройства; на фиг. 3 - временная диаграмма тактовых импульсов.

Устройство содержит блок 1 памяти мик. рокоманд, регистры адреса 2 и микрокоманд 3, первый регистр 4 выбора каналов, первый регистр 5 сдвига, регистр 6 логических условий, второй регистр 7 выбора каналов, второй регистр 8 сдвига, первый 9 и второй 10 счетчики, первые триггеры запроса 11 и повторного запроса 12, вторые триггеры запроса 13 и повторного запроса 14, мультиплексор 15 входной информации, мультиплексор 16 адреса, демультиплексор 17 выходной информации, мультиплексор 18

выходной информации, первый коммутатор 19, первый 20 и второй 21 элементы И, второй коммутатор 22, группу входов 23(24) параллельного последовательного кода, группу входов 25 кода режима, группу входов 26

синхронизации, группу выходов 27 условий, группу выходов 28 (29) последовательного (параллельного) кода устройства, группу выходов 30 немодифицируемых разрядов адреса очередной микрокоманды, выход 31 конца режима, первый 32.1 и второй 32.2 выходы ошибки, выход 33 конца программы, вторую 34 группу выходов выбора канала, второй выход 35 запроса, группу выходов 36 управления мультиплексором 18, группу выходов 37 выходного кода, первый выход 38 запроса, первую группу выходов 39 выбора канала, группу выходов 40 модифицируемых разрядов адреса, группу выходов 41 управления мультиплексором 16 адреса, выход 42 переполнения счетчика 9, группу выходов 43 регистра 6, вторую группу выходов 44 мультиплексора 18 и выход 45 переполнения счетчика 10. Группа выходов 43 регистра б логических условий соединена с первой группой информационных входов 43 мультиплексора 16 адреса, группа выходов которого соединена с первой группой DZ информационных входов регистра 2 адреса. Выходы регистра 2 адреса соединены с группой входов блока 1 памяти микрокоманд, выходы которого соединены с группой информационных входов регистра 3 микрокоманд. Группы выходов немодифицируемых разрядов адреса очередной микрокоманды 30, модифицируемых разрядов адреса очередной микрокоманды 40, управления мультиплексором адреса 41, управления мультиплексором 36 и выходного кода 37 соединены соответственно с второй группой информационных входов DI регистра 2 адреса, второй группой информационных входов 40 мультиплексора 16 адреса, группой управляющих входов 41 мультиплексора 16 адреса, группой управляющих входов 36 мультиплексора 18, группой информационных входов 37 мультиплексора 18, первая группа выходов 29 которого является группой выходов 29 параллельного кода устройства. Выход 31 конца режима регистра 3 микрокоманд соединен с управляющим входом 31 мультиплексора 16 адреса и является выходом 31 первого разряда группы выходов 27 условий устройства, выход 33 второго разряда которой является выходом 33 конца программы регистра 3 микрокоманд. Группа входов 23 параллельного кода устройства и группа входов 25 кода режима устройства соединены соответственно с входами третьей 23 и четвертой 25 групп информационных входов мультиплексора 16 адреса. Входы первого 26.1 и второго 26.2 разрядов группы синхровходов 26 устройства соединены с первыми входами первого 20 и второго 21 элементов И соответственно. Группа выходов первого регистра 4 выбора канала соединена с группой управляющих входов мультиплексора 15, выход, которого соединен с информационным входом Е младщего разряда первого регистра 5 сдвига. Группа входов 24 последовательного

кода устройства соединена с группой информационных входов 24 мультиплексора 15 входов. Единичный выход первого триггера 11 запроса соединен с входом разрещения счета первого счетчика 9, входом V разрешения записи единицы первого триггера 12 повторного запроса и входом V разрешения сдвига первого регистра 5 сдвига, группа выходов которого соединена с группой информационных входов D регистра 6 логических условий. Нулевой выход первого триггера 11 запроса соединен с первым управляющим входом первого коммутатора 19, выход которого соединен с входом С синхронизации первого регистра 4 выбора каналов. Вы.ход 42 переполнения первого счетчика 9 соединен с входом V разрешения записи регистра 6 логических условий, вторы.у; управляющим входом первого коммутатора 19, входом R сброса первого триггера 1 i запроса, входом VI разрешения сброса перг.ого с .етчика 9 и входом VI разрешения ус:т:;)пнки в нуль первого триггера 12 првторкого запроса, единичный вЫход которого соединен с третьим управляющи.м входом первого коммутатора 19, а нулевой выход - с вторыми входами первого 20 и второго 21

5 элементов И. входом разрешения сброса первого триггера 11 запроса и четвертым управляющим входом первого коммутатора 19. Первая 39 и вторая 34 группы выходов выбора каналов регистра 3 микрокоманд соединены с группами информационных

0 входов первого 4 и второго 7 регистров выбора каналов соответственно. Первый 32.1 и агорой 32.2 выходы ошибки регистра 3 микрокоман.,а. являются выходами соответственно третьего 32.1 и четвертого 32.2 разрядов группы выходов 27 условий устройства. Первый 38 (второй 35) выход запроса регистра 3 микрокоманд соединен с единичным ; входами первого 12 (второго 14) триггера повторного запроса и первого 11 (второго 13) триггера запроса, а также с первым

0 информационным входом первого 19 (второго 22) коммутатора. Группа выходов второго регистра 7 выбора каналов соединена с группой управляющих в.ходов демультиплексора 17, группа выходов 28 которого является группой выходов 28 последовательного кода

5 устройства. Выход второго коммутатора 22 соединен с входом С синхронизации второго регистра 7 выбора каналов и входом С1 синхронизации записи второго регистра 8 сдвига, выход младшего разряда которого соединен с информационным входом демультиплексора 17. Нулевой выход второго триггера 13 запроса соединен с первым управляющим входом второго коммутатора 22, единичный выход второго триггера 13 запроса соединен с входами разрешения сдвига

5 V2 второго регистра 8 сдвига, разрешения счета V второго счетчика 10 и разрешения записи единицы V второго триггера J4 поSToporo запроса, единичный выход которого соединен с вторым управляющим входом второго коммутатора 22. Нулевой выход второго триггера 14 повторного запроса соединен с третьими входами первого 20 и второго 21 элементов И, третьим управляющим входом второго коммутатора 22 и входом разрешения установки в нуль второго триггера 13 запроса. Выход 45 переполнения второго счетчика 10 соединен с нулевым входом первого триггера 13 запроса, входом разрешения установки в нуль второго триггера 14 повторного запроса, входом разрешения сброса второго счетчика 10 и четвертым управляюш,им входом второго коммутатор 22. Вторая группа выходов 44 мультиплексора 18 выходов соединена с группой информационных входов второго регистра 8 сдвига, вход Е2 старшего разряда которого соединен с нулевым полюсом источника питания. Вход 26.1 первого разряда группы синхровходов 26 устройства соединен с синхровходом С первого регистра 5 сдвига, счетными входами (-f 1) первого 9 и второго 10 счетчиков и входом С2 синхронизации сдвига второго регистра 8 сдвига. Вход 26.2 второго разряда группы синхровходов 26 устройства соединен с вторыми информационными входами первого 19 и второго 22 коммутаторов, входами С1 синхронизации установки в нуль первого 11 и второго 13 триггеров запроса и входом С синхронизации регистра 6 логических условий. Вход 26.3 третьего разряда группы синхровходов 26 устройства соединен с входами R1 сброса первого 9 и второго 10 счетчиков и нулевыми входами R первого 12 и второго 14 триггеров повторного запроса. Предлагаемое устройство предназначено для использования в качестве имитатора объекта контроля и управления, например летательного аппарата, в системах проверки бортовых вычислительных машин (БВМ) этих аппаратов. В соответствии с программой функционирования (проверки) БВМ устройство может выдавать сигналы реакций, аналогичные реакциям чувствительных элементов объекта управления (ЛА) в последовательном и параллельном коде, а также воспринимать сигналы управляюш,их воздействий от БВМ в указанном виде. Кроме того, устройство позволяет осуществлять проверку кодов управляющих сигналов БВМ, которые поступают на него в виде сигналов логических условий ветвления программы контроля, на допустимость и формировать соответствующий сигнал ошибки в блок управления системы контроля. В процессе имитации функционирования объекта устройство может осуществлять в заданные моменты времени выдачу недопустимых значений сигналов датчиков ЛА для проверки реакции на них контролируемой БВМ. Реакции на недопустимые сигналы анализируются блоком управления автоматизированной системы контроля. Управление предлагаемым устройством осуществляется на основании кодов режимов работы, поступающих от блока управления системы контроля БВМ, и последовательных и параллельных кодов управляющих воздействий от контролируемой БВМ. Все эти сигналы воспринимаются устройством как сигналы логических условий, управляющие направлением реализации программы имитации. Блок 1 памяти микропрограмм (фиг. 1) предназначен для хранения программ имитации функционирования объекта управления и контроля в различных режимах и может быть выполнен на базе стандартного ПЗУ статического типа. Регистр 2 адреса служит для хранения адреса очередной микрокоманды программы имитации, который формируется как композиция модифицируемых разрядов, поступающих на его вход с группы выходов 30 регистра 3 микрокоманд, и модифицируемых разрядов, значения которых поступают на входы регистра с выхода мультиплексора 14. Регистр 3 микрокоманд используется для хранения текущей микрокоманды программы имитации объекта контроля. Выход 31 регистра 3 предназначен для подачи сигнала окончания отработки заданного режима имитации функционирования объекта, заданного по коду, поступившему на входы 25 устройства от блока управления системы контроля БВМ. Сигнал с выхода 31 настраивает мультиплексор 16 на прием очередного кода режима с входов 25 устройства. С выходов 32.1 и 32.2 регистра 3 выдаются сигналы ошибочного входного воздействия от контролируемой БВМ, поступивщего на вход 23 или 24 устройства. Сигналы заданного некорректного кода состояния датчиков объекта управления (ЛА) поступают с выходов 28 или 29 устройства соответственно. Выход 33 регистра 3 предназначен для выдачи сигнала окончания программы имитации функционирования объекта управления. Сигналы с выходов 31, 32.1, 32.2 и 33 поступают через группу выходов 27 устройства на соответствующие входы логических условий блока управления системы контроля БВМ. С группы выходов 34 регистра 3 на D-BXOды регистра 7 выдается код выбора соответствующего разряда выхода группы 28 для выдачи последовательного кода, имитирующего сигналы состояния датчиков объекта управления (ЛА). Выход 35 регистра 3 является импульсным и служит для идентификации требования преобразования параллельного кода имитации реакции ЛА с группы выходов 37 регистра 3 в последовательный код, выдаваемый с заданного выхода 26 демультиплексора 17.

Группа выходов 36 предназначена для задания направления передачи кода с выходов 37 регистра 3 на одну из групп 44 или 29 выходов мультиплексора 18.

Выход 38 регистра 3 является импульсным и выдает сигнал требования преобразования последовательного кода управляющего воздействия БВМ, поступающего на один из входов группы 24, задаваемый кодом с группы выходов 39 регистра 3 и хранимый в регистре 4. в параллельный код, накапливаемый в регистре 5.

Группы выходов 40 и 41 регистра 3 предназначены для задания значений модифицируемых разрядов адреса очередной команды и управления мультиплексором 16 соответственно.

Регистры 5 и 6 используются для приема последовательного - выдачи параллельного кодов и приема параллельного - выдачи последовательного кодов соответственно.

Счетчики 9 и 10 предназначены для подсчета числа принимаемых и выдаваемых разрядов последовательного кода соответственно.

Исходным состояние счетчиков 9 и 10 является нулевое. Счет импульсов, поступающих на соответствующий вход ( + 1) счетчиков 7 и 8 с входа 26.1 группы тактовых входов 26 устройства, может происходить только при наличии сигнала на входе (V) разрешения.

Триггеры 11 и 13 предназначены для фиксации состояния преобразования входного последовательного кода в параллельный и выходного параллельного кода в последовательный соответственно. Изменение состойний всех триггеров и регистров устройства может происходить только при наличии соответствующих сигналов на V- и С-входах.

Триггеры 12 и 14 осуществляют фиксацию повторного запроса на выполнение преобразований, отличаемых триггерами 11 и 13 соответственно. При поступлении повторного запроса одного из указанных типов (или обоих типов) триггеры 12 или (и) 14 устанавливаются в единичное состояние и блокируют через элементы И 20 и 21 поступление тактовых импульсов на соответствующие G-входы регистров 2 и 3.

Установка триггера 12 (14) в единичное состояние при поступлении повторного запроса на преобразование последовательного (параллельного) входного (выходного) кода в параллельный (последовательный) выходной (входной) во время выполнения устройством указанной операции происходит по заднему фронту импульса на S-входе при наличии разрешающего потенциала на Vвходе с единичного выхода триггера 11 (13).

Регистр 6 предназначен для подачи на входы 43 мультиплексора 16 сформированного в регистре 5 сдвига параллельного кода.

Запись в регистр 6 происходит при наличии разрешающего сигнала с выхода 42 переполнения счетчика 7 по второму тактовому импульсу с входа 26.2 устройства. 5 Элемент И 20 (21) используется для подачи каждого первого (второго) тактового импульса с входа 26.1 (26.2) группы входов 26 устройства при наличии разрейдающих сигналов с нулевых выходов триггеров 12 и 14.

На группу входов 23 (24) поступают сигналы управляющих воздействий от контролируемой БВМ в виде параллельного (последовательного) кода.

Группа входов 25 предназначена для подачи на одноименный вход мультиплексо5 ра 16 кода задания режима имитации функционирования объекта управления (ЛА).

Группа тактовых входов 26 предназначена для подачи на эле.менты и узлы устройства последовательности сдвинутых друг относительно друга тактовых импульсов 0 в соответствии с временной диаграммой на фиг. 3.

Устройство включается в работу с началом подачи тактовых импульсов на входы 26. В случае прекращения подачи тактовых импульсов на входы 26 устройство прекращает функционирование.

С группы выходов 28 (29) выделяются сигналы последовательного (параллельного) выходного кода, имитирующие сигналы датQ чиков объекта управления (ЛА).

Коммутаторы 19 и 22 предназначены для управления записью кодов настройки мультиплексоров 15 и 17 соответственно в начале реализации преобразования входного последовательного или выходного параллельного 5 кода.

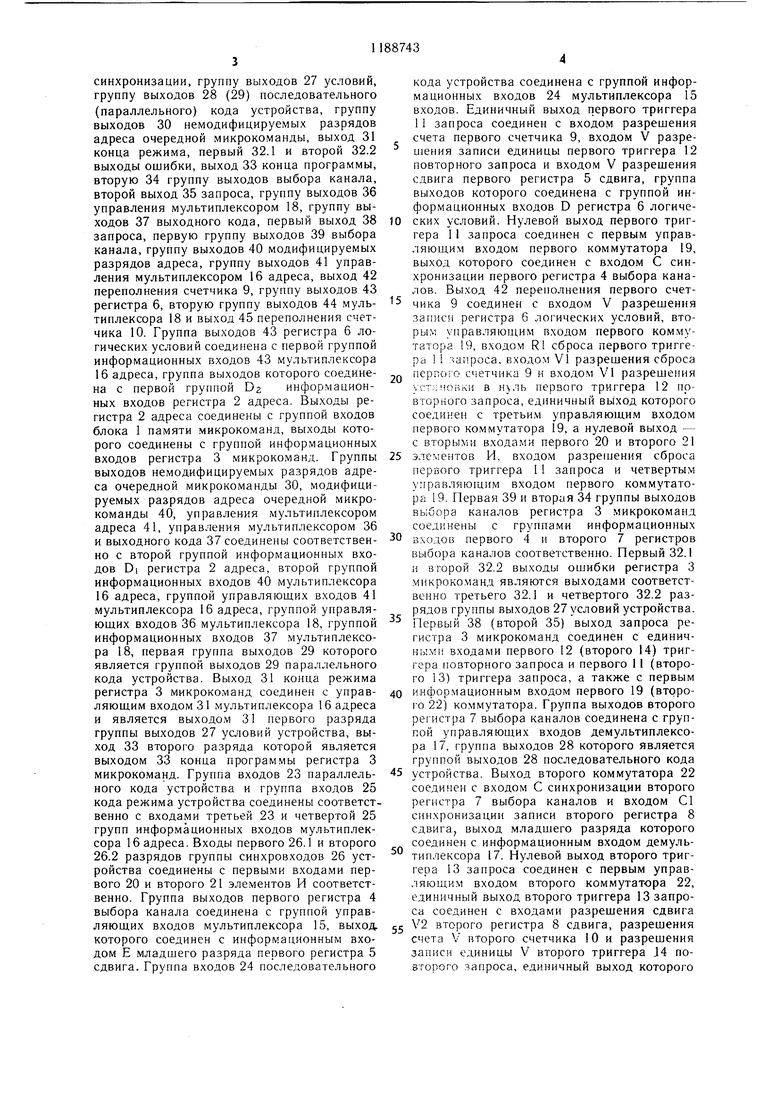

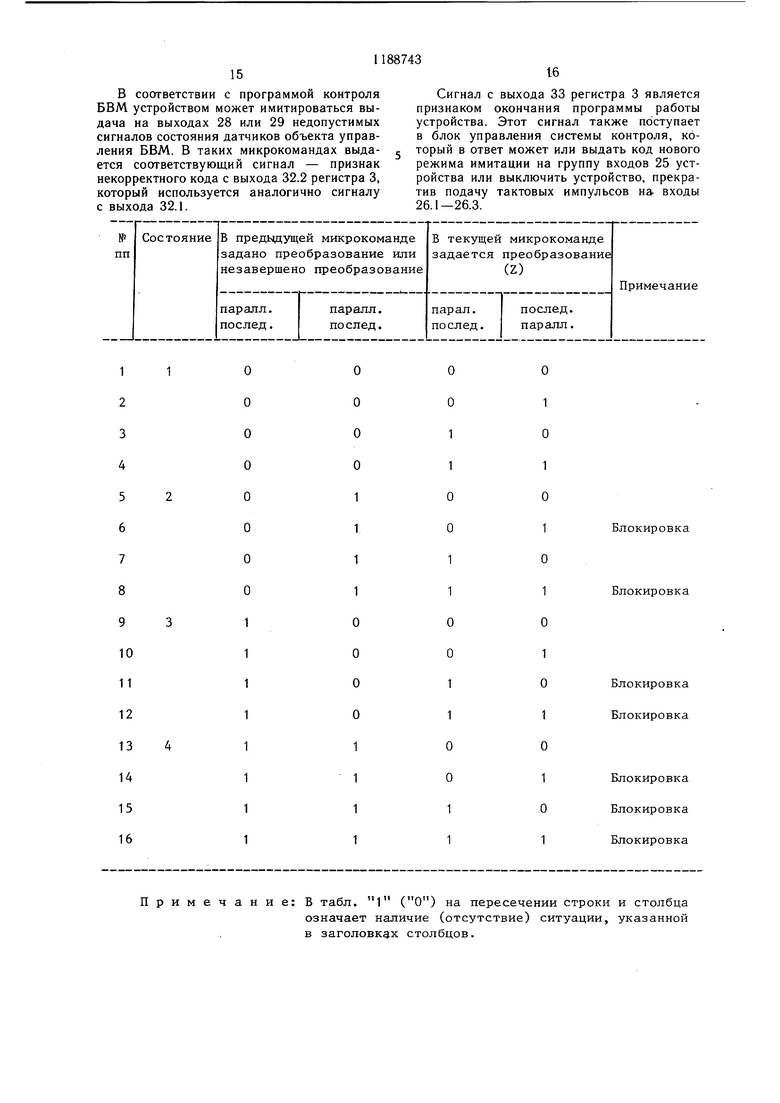

На фиг. 2 приведен граф переходов состояний устройства. Обозначения, использованные на фиг. 2, соответствуют следующей таблице состояний устройства.

В ситуациях 6, 8, 1 1, 12, 14, 15 и 16 устройство переходит в состояние блокировки, в котором запрещается выходными сигналами (нулевыми) триггеров 12, 14 подача тактовых импульсов на входы синхронизации записи регистров 2 и 3 до момента завершения преобразования кодов и установки триггеров 12 и (или) 14 в нулевое состояние. При этом длительность ожидания ATgjj в состоянии блокировки определяется по формуле:

АТбл Ткач -f At - Тповт 0 где Тнач - время начала преобразования последовательного (параллельного) кода в параллельный (последовательный); At -длительность преобразования

кода;

ТПОБТ -время поступления повторного запроса на преобразование последовательного кода в параллельный.

Предлагаемое устройство работает следующим образом.

В отношении реализации адресного тракта выборки микрокоманд, состоящего из блоков 16, 2, 1 и 3 устройство не отличается от известных.

Сущность изобретения состоит в дополнительном введении конструктивных средств, которые позволяют повысить производительность и расщирить область применения устройства при одновременной (или в произвольной последовательности) выдаче микрокоманд выполнения преобразований последовательного кода Б параллельный или (и) наоборот. Поэтому целесообразно функционирование устройства рассматривать на примере реализации указанных микрокоманд в различной комбинации их поступления, поскольку именно последовательность таких микрокоманд составляет микропрограмму (программу имитации функционирования объекта управления (ЛА).

Конкретные значения, разрядность, последовательность выдачи с выходов 28 и 29 и приема на входы 23, 24 кодов состояния датчиков ЛА и управляющих кодов БВМ определяются характеристиками объекта управления (ЛА) и БВМ.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии, на выходе 31 регистра 3 присутствует единичный сигнал, настраивающий мультиплексор 16 (фиг. 1) на задание значения модифицируемых разрядов адреса очередной команды на входах регистра 2 в соответствии с кодом режима имитации, поступающим на группу входов 25 устройства. Устройство начинает функционировать с подачей первого тактового импульса на вход 26.1 устройства. Этот импульс через элемент И 20, открытый сигналом с нулевого выхода триггера 12, поступает на синхровход (С) регистра 2 и разрешает запись в этот регистр кода режима имитации с входов 25 устройства, которым задается начало микропрограммы имитации функционирования объекта в данном режиме.

Код адреса очередной микрокоманды поступает на входы блока 1 памяти, на выходах которого появляется код соответствующей микрокоманды. По второму тактовому импульсу, который поступает на вход 26.2 устройства и далее через открытый элемент И 21 проходит на синхровход (С) регистра 3, осуществляется запись кода (текущей) микрокоманды в регистр 3. Дальнейшие действия устройства определяются содержимым этой микрокоманды.

С группы выходов 30 регистра 3 на входы DI регистра 2 поступает код немодифицируемых разрядов адреса очередной микрокоманды. Сигналы на выходах 31, 32.1, 32.2 и 33 равны нулю.

С выходов 36 может выдаваться код настройки мультиплексора 18 на соединение группы выходов 37 параллельного кода, выдающие код, имитирующий состояние

датчиков ЛА, с одной из групп разрядов группы выходов 44 или 29 мультиплексора 18. С выходов соответствующей группы разрядов выходов 29 на входы соответствующей группы входов параллельного кода БВМ поступает параллельный код, имитирующий состояние соответствующего датчика ЛА. С выходов 44 мультиплексора при соответствующем коде настройки с выходов 36 задается параллельный код, который должен быть преобразован в последовательный.

Если в текущей микрокоманде задано преобразование параллельного кода с выходов 37 в последовательный, то при установке состояния регистра 3 с выхода 35 выдается импульс, устанавливающий по заднему фронту в единичное состояние триггер 11, который

потенциалом с единичного выхода разрешает работу счетчика 10, сдвиг информации в регистре 8 (по входу V2) и открывает по входу V триггер 14 для записи единицы.

В коде, записанному по второму тактовому импульсу в регистр 3, может быть задано также преобразование последовательного кода с входов одного из разрядов группы входов 24, выбираемого кодом настройки с выходов группы выходов 39 регистра 3

Q в параллельный код, накапливаемый в регистре 5 сдвига. Для этого выдается импульсный сигнал с выхода 38 регистра 3, который по всему заднему фронту устанавливает триггер 11 в единичное состояние. 11отенциал с единичного выхода триггера 11 открывает

триггер 12 по входу V для установки в единицу, регистр 5 по входу V для сдвига и счетчик 7 по входу V.

Кроме того, в рассматриваемом случае на выходах 34 регистра 3 выдается код настройки демультиплексора 17 на соединение его информационного входа с заданным входом группы выходов 28. Этот код по переднему фронту импульса, поступающего с выхода 25 через коммутатор 22 на С-вход регистра 5, записывается в регистр 5. Аналогично происходит запись в регистр 4 с выходов 39 регистра 3.

Кроме того, в случае задания необходимости преобразования параллельного кода с выходов 37 регистра 3 в последовательный

регистр 7 записывается с выходов 34 регистра 3 код выбора соответствующего выхода группы 28 для соединения с выходом регистра 9 сдвига, осуществляющего требуемое преобразование кодов. Одновременно этим же сигналом с выхода коммутатора 22 параллельный код с выходов 44 мультиплексора 18 записывается через входы 1 в регистр 8 по синхросигналу на входе С1. После записи адреса микрокоманды в регистр 2

11

аналогично описанному выше на выходах блока 1 памяти формируется код очередной микрокоманды.

По очередному второму тактовому импульсу с входа 26.2 группы входов 26 устройства через элемент И 21 разрешается запись кода очередной микрокоманды в регистр 3. При этом возможны ситуации, которые предопределяются алгоритмом дальнейшей работы устройства в соответствии с приведенной выше таблицей.

Рассмотрим последовательно отмеченные в таблице ситуации.

Из таблицы видно, что в момент формирования текущей микрокоманды устройство может быть в состоянии, когда не выполняются никакие операции по преобразованию кодов. Это состояние является первым (S1), ему соответствуют ситуации 1-4 таблицы. Второму состоянию соответствует случай, когда в одной из предыдущих микрокоманд задано преобразование входного последовательного кода с входов 24 в параллельный код. Этому состоянию соответствуют ситуации 5-8 таблицы. Третьему состоянию соответствует случай, когда в одной из предыдущих микрокоманд задано незавершенное, к рассматриваемому моменту времени, преобразование параллельного кода с выходов 37 в последовательный код на заданном выходе группы выходов 28. Этому состоянию соответствуют ситуации 9-12 таблицы. соответствуют ситуации 9-12 таблицы. Четвертому состоянию соответствует случай, когда в одной или двух предыдущих микрокомандах задано преобразование как последовательного, так и параллельного кода. Этому состоянию соответствуют ситуации 13-16 таблицы.

Если устройство находится в первом состоянии (S1) и задается импульсом с выхода 35 преобразование параллельного кода с выходов 37 в последовательный (ситуации 3 и/или 4), по импульсу с выхода 35 регистра 3 срабатывает коммутатор 22, открытый потенциалами с нулевых выходов триггеров 13 и 14, и по переднему фронту этого импульса осуществляется запись кода выбора соответствующего выхода демультиплексора 17 в регистр 7 с выходов 34 регистра 3, а также запись по сигналу на входе С1 параллельного кода с выходов 44 мультиплексора 18 через входы D1 в регистр 8 сдвига.

По очередному первому и второму тактовому импульсу с входов 26 и 26.2 устройства соответственно происходит аналогично описанному выще запись кода адреса в регистр 2 и микрокоманды в регистр 3. По этому очередному первому импульсу и по следующим первым импульсам с входа 26.1 происходит увеличение на единицу значения кода в счетчике 8, а также сдвиг кода в регистре 8 по синхросигналу на входе С2 и

12

сигналу разрешения сдвига с единичного выхода V2 триггера 14. При этом по мере сдвига происходит заполнение нулями освободившихся старших разрядов регистра 8

с входа Е2, соединенного с нулевым полюсом источника питания. По отношению к текущей микрокоманде, записанной в регистр 3, устройство может находиться в состояниях 3 или 4, если в предыдущей команде было имитировано преобразование входного последовательного кода в параллельный. Если в микрокоманде, записанной в регистр 3, снова задается выполнение преобразования выходного параллельного кода в последовательный, то по заднему фронту

5 импульса с выхода 35 регистра 3 устанавливается в единичное состояние открытый по входу V триггер 14, который фиксирует повторный запрос на аналогичное преобразование и закрывает регистры 7 и 8 для записи информации с выходов 34 и 44 соответственно, а также закрывает элементы И 20 и 21 для пропуска тактовых импульсов с входов 26.1 и 26.2 на регистры 2 и 3. Тем самым устройство переводится в состояние блокировки, которое может соответствовать ситуациям 1 1, 12, 15 и 16 таблицы.

Ожидание продолжается до тех пор, пока по очередному первому тактовому и.мпульсу с входа 26.1 не произойдет переполнение счетчика 10. Сигнал с выхода 45 переполнения счетчика 10 открывает для сброса по

Q входу R1 триггер 13, по входу VI счетчик 10, по входу VI триггер 14, а также открывает коммутатор 22 для выдачи сигнала записи в регистр 7.

Триггер 13 устанавливается по второму

, тактовому импульсу с входа 26.2 в нулевое состояние только в случае отсутствия повторного запроса на аналогичное преобразование кодов, чему соответствует, в рассматриваемый момент времени, нулевое состояние триггера 14, подаю дего со своего

0 нулевого выхода потенциал на вход VI разрешения сброса триггера 13. Если триггер 14 находится в единичном состоянии, т. е. фиксировал наличие повторного запроса, то триггер 13 по второму тактовому импульсу устанавливается в нулевое состояние. Кроме

того, по второму импульсу срабатывает коммутатор 22, и по переднему фронту данного импульса осуществляется запись кодов в регистры 8 и 7, соответствующих очередному запросу, аналогично описанному вьш1е.

Q По очередному третьему тактовому импульсу с входа 26.3 (по переднему его фронту) триггер 14 устанавливается в нулевое состояние (либо его нулевое состояние подтверждается), а по заднему фронту этого импульса сбрасывается в исходное состояние

5 счетчик 10.

Триггер 14 снимает блокировку с тон И 20 и 21, поэтому очередной исгВьп:

импульсс входа 26.1 осуществляет запись кода адреса очередной микрокоманды в регистр 2, и,кроме того, осуществляется дальнейшее выполнение преобразования параллельного кода в последовательный аналогично описанному выше. Таким образом, с указанного момента времени устройство снова находится в состояниях 3 и (или) 4. Если преобразование выходного параллельного кода не задано, то устройство переходит в состояние первое или второе (см. таблицу).

Независимо от описанных преобразований может выполняться и преобразование входного последовательного кода в параллельный в регистре 5 сдвига.

Рассмотрим функционирование устройства в соответствующих ситуациях. Предположим, что предыдущим состоянием устройства является нулевое (см. таблицу).

Если в текущей микрокоманде, считываемой но второму тактовому импульсу с входа 26.2 устройства, задастся преобразование входного последовательного кода с входов одного из разрядов группы входов 24 в параллельный код, то импульс с выхода 38 регистра 3 устанавливает по задне.му фронту в единичное состояние триггер 1 1, который потенциалом с единичного выхода открывает по входу VI счетчик 9 и разрешает сдвиг по входу V в регистре 5.

Кроме того, импульсный сигнал с выхода 38 регистра 3 поступает на соответствующий вход открытого сигналами с пулевых выходов триггеров 11 к 12 коммутатора 19, который срабатывает, и по переднему фронту этого сигнала осуществляется ;и::1ись кода настройки мультиплексора 15 с выходов 39 регистра 3 в регистр 4. Описанная ситуация соответствует ситуациям 2, 4, 10 и (или) 12 таблицы.

Далее по каждому очередному первому тактово.му импульсу с входа 26.1 устройства осуществляется сдвиг информации в регистре 5, запись в младший разряд по входу Е очередного импульса последовательного кода с выхода мультиплексора 15 и одновременно с этим увеличение на единицу содержимого счетчика 9. Запись в регистр 4 Не происходит, так как коммутатор 19 закрыт.

Если во время преобразования последовательного кода в параллельный будет считана микрокоманда в регистр 3, в которой будет снова задано преобразование входного последовательного кода, то импульс с выхода 36 регистра 3 поступает на D-вход триггера 12, открытый по входу V потенциалом с единичного выхода триггера 1 1. Этот триггер устанавливается в единичное состояние по заднему фронту этого импульса. При этом коммутатор 19 не срабатывает.

Нулевым потенциалом с нулевого выхода триггера 12 закрываются элементы И 20 и 21, вследствие чего устройство переходит в состояние блокировки, во время которого состояния регистров 2 и 3 не изменяются.

Выход из состояния блокировки происходит следующим образом.

При приеме по первому тактовому импульсу с входа 26.1 последнего разряда последовательного кода в регистр 5 происходит переполнение счетчика 9, который выдает сигнал на выходе 42. По этому сигналу открывается коммутатор 19, разрещается по V-входу запись в регистр 6, по V -входу сброс счетчика 9, по VI-входу сброс триггера 12 и по Rl-входу сброс триггера 11.

По очередному второму тактовому импульсу с входа 26.2 осуществляется запись информации с выхода регистра 5 в регистр 6, срабатывает коммутатор 19 и разрешает запись в регистр 4 кода настройки мультиплексора 15 с выходов 39 регистра 3. При этом триггер 11 не сбрасывается, так как его сброс по входу запрещен нулевым потенциалом с нулевого выхода триггера 12.

Q Далее по переднему фронту очередного третьего тактового nMnyvibca с входа 26.3 устройства триггер 12 устанавливается в нулевое состояние и открывает элементы И 20 и 21 синхронизации регистров 2 и 3. По заднему фронту этого же импульса по входу

R1 устанавливается в исходное состояние счетчик 9. После этого с приходом очередного первого тактового импульса с входа 26.1 регистр 5 и счетчик 9 продолжают функционирование аналогичного описанному выще для второго и (или) четвертого состояния.

0 Кроме того, по этому импульсу в perHtTp 2 записывается адрес очередной микрокоманды, модифицированный разрядами кода, содержагцегося в регистре 6. Далее по второму тактовому импульсу по адресу в регистре 2 выбирается команда и записывается

5 в регистр 3. Далее устройство функционирует аналогично описанному.

Если бы в процессе преобразования входного последовательного кода повторный

0 запрос с выхода 38 не поступил, что соответствует ситуациям 9, 10, 13 и (или) 14, то триггер 12 находился бы в нулевом состоянии в момент переполнения счетчика 9. Поэтому в отличие от рассмотренной ситуации по второму тактовому импульсу с входа 26.2 коммутатор 19 не срабатывает и запись в регистр 4 не происходит.

Проверка кода логических условий, содержащегося после выполнения преобразования в регистре 6, может осуществляться в любой последующей микрокоманде до завершения

0 следующего цикла преобразования. Если окажется, что содержимое счетчика 6 не соответствует допустимым значениям, то произойдет переход к микрокоманде, генерирующей сигнал на выходе 32.1 группы выхо, дов 27, который является признаком ошибочности входного воздействия и используется блоком управления системы контроля для принятия решения.

В соответствии с программой контроля БВМ устройством может имитироваться выдача на выходах 28 илн 29 недопустимых сигналов состояния датчиков объекта управления БВМ. В таких микрокомандах выдается соответствующий сигнал - признак некорректного кода с выхода 32.2 регистра 3, который используется аналогично сигналу с выхода 32.1. Примечание:

Сигнал с выхода 33 регистра 3 является признаком окончания программы работы устройства. Этот сигнал также поступает в блок управления системы контроля, к6торый в ответ может или выдать код нового режима имитации на группу входов 25 устройства илн выключить устройство, прекратив подачу тактовых импульсов на входы 26.1-26.3. В табл. 1 (О) на пересечении строки и столбца означает наличие (отсутствие) ситуации, указанной в заголовках столбцов.

00 01 iO

i1

Фиг. 3 ,оУг Переходы при запросе преобразования кодов Переход fez ожидания Переход с ожиданием (планировкой} Переход при ъаВершении преобразования Переход при заВермении прео5 рс(гоВания L{j.)i Фиг. 2

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020824A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1984-05-21—Подача