4 1чЭ

СО о: о:

1

Изобретение относится к ке и вычислительной технике быть использовано при разра ропрограммируемых контролледелительных вычислительных систем управления технологи процессами.

Цель изобретения - расшиласти применения модуля;, за ганизации смены микропрограшения числа выводов,

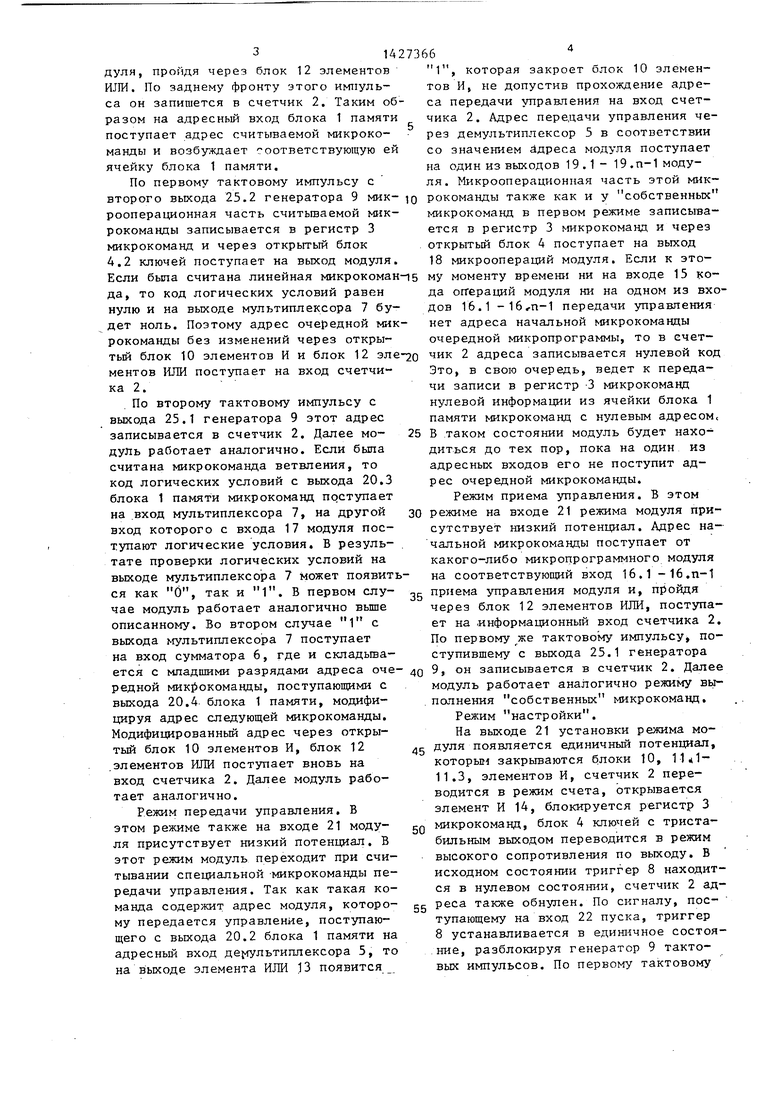

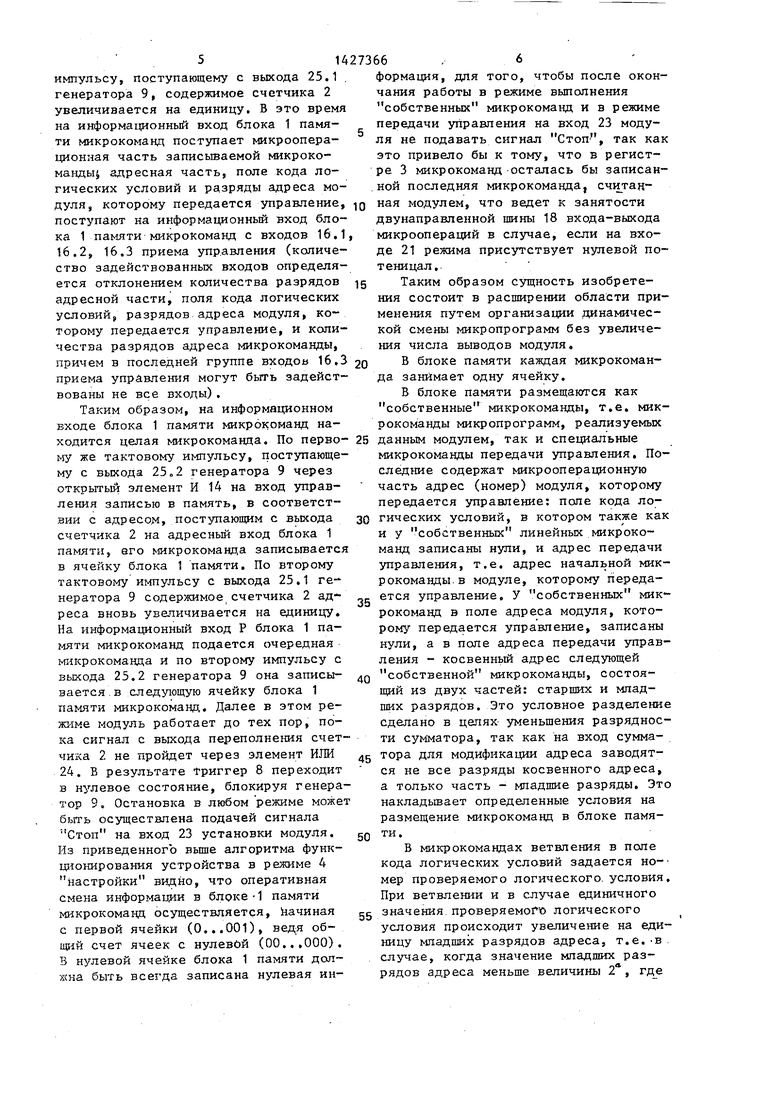

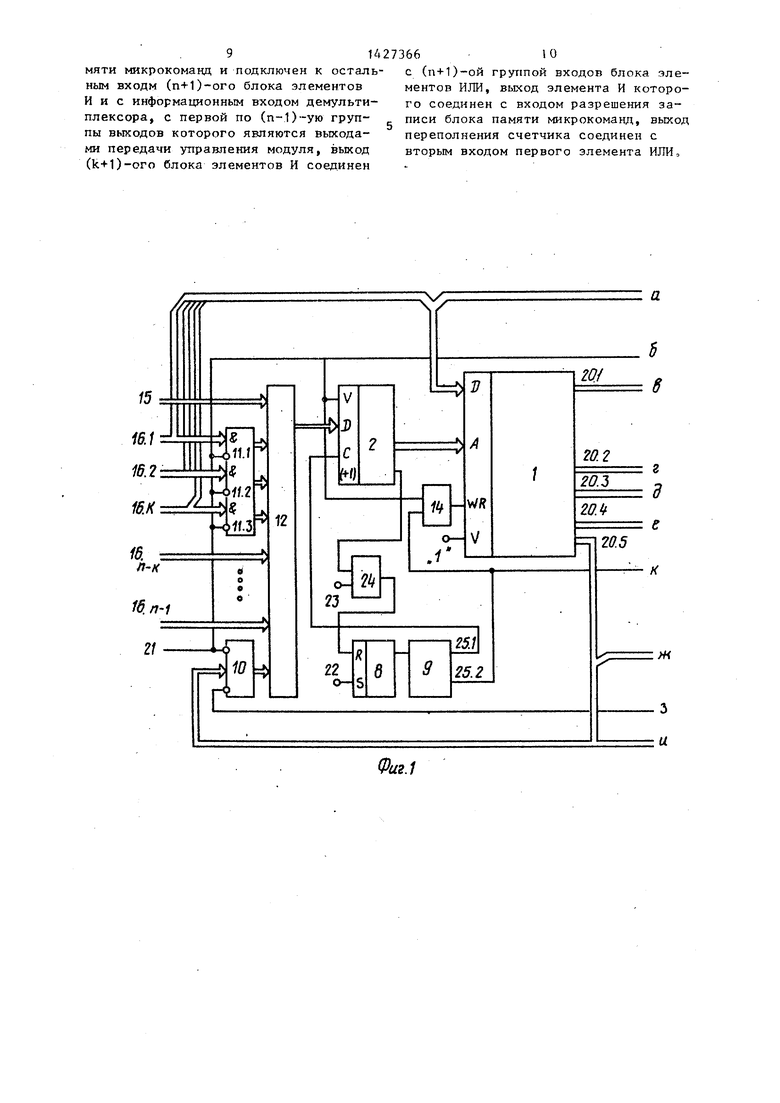

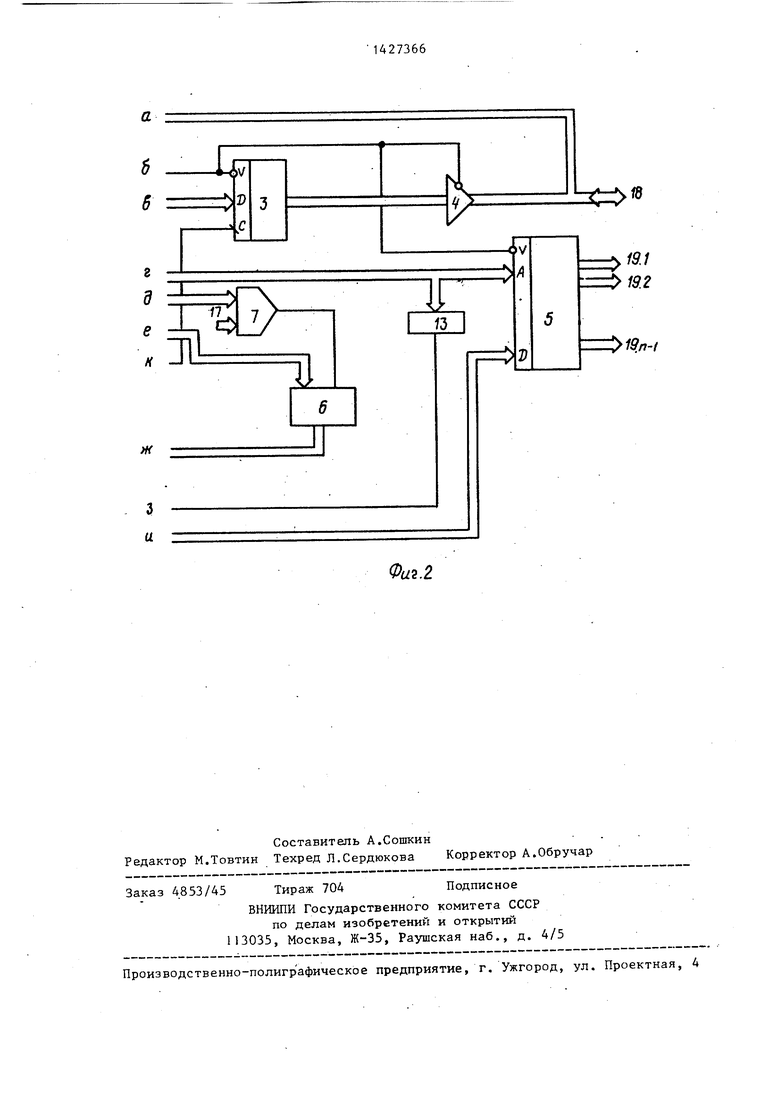

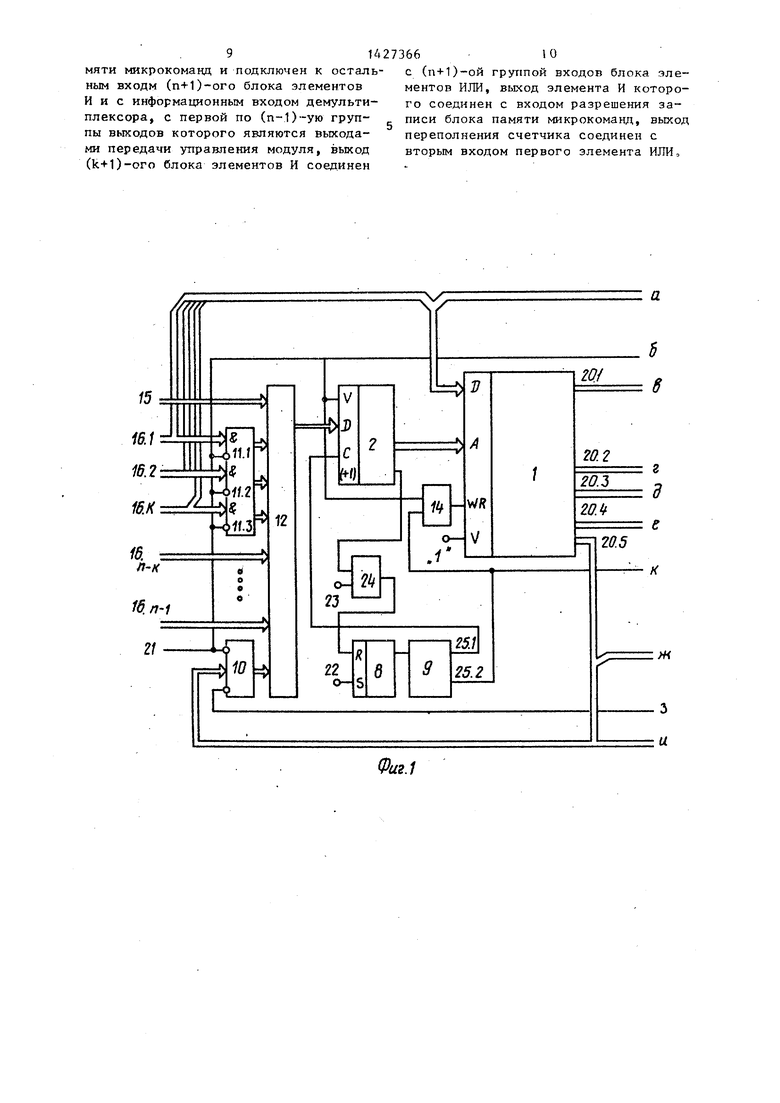

На фиг. 1,2 представлена нальная схема микропрограмм

ля ,

Устройство (фиг. 1,2) содержит блок 1 памяти микрокоманд, счетчик 2 адреса, регистр 3 микрокоманд, блок 4 ключей с тристабильным выходом, демультиплексор 5, сумматор 6, муль- типлексор 7, триггер 8 пуска, генератор 9 тактовых импульсов, (k+1)- бл о- ков 10 элементов И (k - количество входов приема управления, прием инфор мallJ и с которых блокируется), первьй 11.1, второй 11.2 и (n-k) 11.3 блоки элементов И (п -г количество входов приема управления), блок 12 элементов ИЛИ, второй элемент ИЛИ 13, элемент И 14, вход кода 15 операций модуля, первый 16.1-(п-1) - 16.П-1 входы приема управления модуля (от первого, второго - (п-1)-Го микропрограммных модулей соответственно), вход 17 лоQ5

0 5 0

писи и хранения микрооперационной части очередной считываемой микрокоманды. Блок ключей с тристабильным выходом служит для обеспечения нормальной работы двунаправленной шины 18 микроопераций модуля. Демультиплексор 5. (передачи управления) предназначен дпя коммутации адреса передачи управления на соответствующий микропрограммный модуль. Сумматор 6 предназначен для модификации младших разрядов адреса очередной микрокоманды. Мультиплексор 7 предназначен для выделения значения логического условия, соответствующего заданному коду, поступающему с выхода 20.3 логических условий блока 1 памяти микрокоманд. Триггер 8 пуска предназначен для запуска или остановки генератора 9 тактовых импульсов. Генератор 9 служит для вь щачи двух серий тактовых импульсов. Блок 10 элементов И служит для блокировки входа счетчика.2 адреса при считывании микрокоманды передачи управления, а также в режиме Настройка. Блоки 11.1, 11.2, 11.3 элементов И служат для блокировки входа счетчика 2 адреса при реализа ции режима Настройка. Блок 12 элементов ИЛИ служит для передачи информации на вход регистра - счетчика 2 адреса.Элемент ИЛИ 13 служит для управления блоком 10 элементов И при

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

40

45

гических условий модуля, вход - выход ос считывании специальной микрокоманды 18 модуля, первый 19,1(п-1) - 19.п-1 выходы передачи управления модуля (первому, второму - (п-1)-ому микропрограммным модулям соответственно), выход 20.1 поля микроопераций, выход 20.2 поля адреса модуля, выход 20.3 поля кода логических условий, выход .20.4 поля мпадщих разрядов адресной части микрокоманд, вьйсод 20.5 поля старших разрядов адресной части микрокоманд, вход 21 режима модуля, вход 22 пуска модуля, вход 23 остановки модуля, первый элемент ИЛИ 24, первый 25.1 и второй 25.2 выходы генератора 9 тактовых импульсов.

Блок 1 памяти микрокоманд предназначен для хранения микрокоманд. В блоке 1 памяти микрокоманд каждая микрокоманда занимает одну ячейку. Счетчик 2 адреса предназначен для записи и изменения адреса ячейки блока 1 памяти при записи в блок 1 памяти микрокоманд новой микропрограммы. Регистр 3 микрокоманд служит для за50

55

передачи управления..Элемент И 14 предназначен дл я установки блока 1 памяти микрокоманд либо в режим запи си информации, либо в режим считывания.

Предлагаемый модуль имеет четьцэе режима работы и функционирует следую щим образом. В исходном состоянии вс элементы памяти находятся в нулевом состоянии. Цепи установки исходного состояния условно не показаны. Для нормального функционирования блока памяти на вход обращения V постоянн подается единичный потенциал.

Режим выполнения собственных ми рокоманд. В этом режиме на входе 21 модуля О. Таким образам счетчик 2 адреса находится в режиме записи ин формации. На вход 22,подается сигнал Пуск, триггер В разблокирует гене ратор 9 и первый синхроимпульс с вы да 25.1 поступает на синхровход сче чика 2. Адрес начальной микрокоманд поступает с входа 15 кода операции

считывании специальной микрокоманды

передачи управления..Элемент И 14 предназначен дл я установки блока 1 памяти микрокоманд либо в режим записи информации, либо в режим считывания.

Предлагаемый модуль имеет четьцэе режима работы и функционирует следующим образом. В исходном состоянии все элементы памяти находятся в нулевом состоянии. Цепи установки исходного состояния условно не показаны. Для нормального функционирования блока 1 памяти на вход обращения V постоянно подается единичный потенциал.

Режим выполнения собственных микрокоманд. В этом режиме на входе 21 модуля О. Таким образам счетчик 2 адреса находится в режиме записи информации. На вход 22,подается сигнал Пуск, триггер В разблокирует генератор 9 и первый синхроимпульс с выхода 25.1 поступает на синхровход счетчика 2. Адрес начальной микрокоманды поступает с входа 15 кода операции модуля, пройдя через блок 12 элементов ИЛИ. По заднему фронту этого импульса он запишется в счетчик 2. Таким образом на адресный вход блока 1 памяти поступает адрес считываемой микрокоманды и возбу;1 дает соответствующую ей ячейку блока 1 памяти.

По первому тактовому импульсу с

второго выхода 25.2 генератора 9 мик- д рокоманды также как и у собственных

рооперационная часть считьюаемой микрокоманды записывается в регистр 3 микрокоманд и через открытый блок А.2 ключей поступает на выход модуля.

Если была считана линейная микрокоман-15 му моменту времени ни на входе 15 кода оп ераций модуля ни на одном из входов 16.1 -16.-П-1 передачи управления нет адреса начальной микрокоманды очередной микропрограммы, то в счеттый блок 10 элементов И и блок 12 эле-2о 2 адреса записывается нулевой код

да, то код логических условий равен нулю и на выходе мультиплексора 7 будет ноль. Поэтому адрес очередной микрокоманды без изменений через открыментов 1ШИ поступает на вход счетчика 2.

По второму тактовому импульсу с выхода 25.1 генератора 9 этот адрес записывается в счетчик 2. Далее модуль работает аналогично. Если была считана микрокоманда ветвления, то код логических условий с выхода 20.3 блока 1 памяти микрокоманд поступает на вход мультиплексора 7, на другой вход которого с входа 17 модуля поступают логические условия. В результате проверки логических условий на выходе мультиплексора 7 может появитьтак и 1 . В первом слуся как О, чае модуль работает аналогично выше описанному. Во втором случае 1 с выхода мультиплексора 7 поступает на вход сумматора 6, где и складьтается с младшими разрядами адреса оче- 40 ° записывается в счетчик 2. Далее

редной микрокоманды, поступающими с выхода 20.4 блока 1 памяти, модифицируя адрес следующей микрокоманды. Модифицированный адрес через открытый блок 10 элементов И, блок 12 .элементов ИЛИ поступает вновь на вход счетчика 2. Далее модуль работает аналогично.

Режим передачи управления. В этом режиме также на входе 21 модуля присутствует низкий потенциал. В этот режим модуль переходит при считывании специальной микрокоманды передачи управления. Так как такая команда содержит адрес модуля, которому передается управление, поступающего с выхода 20.2 блока 1 памяти на адресный вход де ультиплексора 5, то на выходе элемента ИЛИ 13 появится

1, которая закроет блок 10 элементов И, не допустив прохождение адреса передачи управления на вход счетчика 2. Адрес передачи управления через демультиплексор 5 в соответствии со значением йдреса модуля поступает на один из выходов 19.1 - 19 . п-1 модуля. Микрооперационная часть этой микмикрокоманд в первом режиме записывается в регистр 3 микрокоманд и через открытый блок 4 поступает на выход 18 микроопераций модуля. Если к этоЭто, в свою очередь, ведет к передачи записи в регистр -3 микрокоманд нулевой информации из ячейки блока 1 памяти микрокоманд с нулевым адресом,

25 В таком состоянии модуль будет находиться до тех пор, пока на один из адресных входов его не поступит адрес очередной микрокоманды.

Режим приема управления. В этом

30 режиме на входе 21 режима модуля присутствует низкий потенциал. Адрес на- чальной микрокоманды поступает от какого-либо микропрограммного модуля на соответствующий вход 16.1 -16.П-1

2g приема управления модуля и, пройдя через блок 12 элементов ИЛИ, поступает на информационный вход счетчика 2, По первому же тактовому импульсу, поступившему с выхода 25.1 генератора

модуль работает аналогично режиму вь1- полнения собственных микрокоманд.

Режим настройки.

На выходе 21 установки режима мо- 45 дуля появляется единичный потенциал, которьс закрываются блоки 10, 11.3, элементов И, счетчик 2 переводится в режим счета, открывается элемент И 14, блокируется регистр 3

микрокоманд, блок 4 ключей с триста- бильным выходом переводится в режим высокого сопротивления по выходу. В исходном состоянии триггер 8 находится в нулевом состоянии, счетчик 2 адреса также обнулен. По сигналу, поступающему на вход 22 пуска, триггер 8 устанавливается в eAHHii4Hoe состояние, разблокируя генератор 9 тактовых импульсов. По первому тактовому

генератора 9, содержимое счетчика 2 увеличивается на единицу. В это время на информационный вход блока 1 памяти микрокоманд поступает микрооперационная часть записываемой микроко- мавды адресная часть, поле кода логических условий и разряды адреса модуля, которому передается управление, IQ ная модулем, что ведет к занятости поступают на информационный вход бло- двунаправленной шины 18 входа-выхода

ка 1 памяти микрокоманд с входов 16.1, 16.2, 16.3 приема управления (количество задействованных входов определяется отклонением количества разрядов ig адресной части, поля кода логических условий, разрядов адреса модуля, ко торому передается управление, и количества разрядов адреса микрокоманды, причем в последней группе входоь 16.3 2о приема управления могут быть задействованы не все входы) .

Таким образом, на информационном входе блока 1 памяти микрокоманд находится целая микрокоманда. По перво- 25 данным модулем, так и специальные

му же тактовому импульсу, поступающе- микрокоманды передачи управления. Пому с выхода 25,

2 генератора 9 через открытььч элемент И 14 на вход управления записью в память, в соответствии с адресом, поступающим с выхода счетчика 2 на адресный вход блока 1 памяти, его микрокоманду записьгоается в ячейку блока 1 памяти. По второму тактовому импульсу с выхода 25,1 генератора 9 содержимое счетчика 2 адреса вновь увеличивается на единицу. На информационный вход Р блока 1 памяти микрокоманд подается очередная микрокоманда и по второму импульсу с выхода 25,2 генератора 9 она записывается, в следующую ячейку блока 1 памяти микрокоманд. Далее в этом режиме модуль работает до тех пор, пока сигнал с выхода переполнения счетчика 2 не пройдет через элемент ИЛИ 24. В результате триггер 8 переходит в нулевое состояние, блокируя генератор 9. Остановка в любом режиме мозкет быть осуществлена подачей сигнала Стоп на вход 23 установки модуля. Из приведенного выше алгоритма функционирования устройства в режиме 4 настройки видно, что оперативная смена информащи в блрке 1 памяти микрокоманд осуществляется, Начиная с первой ячейки (О,.,001), ведя общий счет ячеек с нулевой (00...000), В нулевой ячейке блока 1 памяти должна быть всегда записана нулевая ин35

следние содержат микрооперационную часть адрес (номер) модуля, которому передается управление: поле кода ло30 гических условий, в котором также как и у собственных линейных микрокоманд записаны нули, и адрес передачи управления, т.е. адрес начальной микрокоманды, в модуле, которому передается управление, У собственных микрокоманд в поле адреса модуля, которому передается управление, записаны нули, а в поле адреса передачи управления - косвенньтй адрес следующей

40 собственной микрокоманды, состоящий из двух частей: старших и младших разрядов. Это условное разделение сделано в целях- уменьшения разрядности сумматора, так как на вход сумма45 тора для модификации адреса заводятся не все разряды косвенного адреса, а только часть - младшие разряды. Это накладывает определенные условия на размещение микрокоманд в блоке памя50 ™.

В микрокомандах ветвления в поле кода логических условий задается но-- мер проверяемого логического, условия. При ветвлении и в случае единичного

gg значения проверяемого логического

условия происходит увеличение на единицу младших разрядов адреса, т,е. В случае, когда значение младших разрядов адреса меньше величины 2, где

чания работы в режиме выполнения собственных микрокоманд и в режиме передачи управления на вход 23 модуля не подавать сигнал Стоп , так как это привело бы к тому, что в регистре 3 микрокоманд осталась бы записан- ,ной последняя микрокоманда, считанмикроопераций в случае, если на входе 21 режима присутствует нулевой по- теницал.

Таким образом сущность изобретения состоит в расширении области применения путем организации динамической смены микропрограмм без увеличе- 1ИЯ числа выводов модуля,

В блоке памяти каткдая микрокоманда занимает одну ячейку,

В блоке памяти размещаются как собственные микрокоманды, т,е, микрокоманды микропрограмм, реализуемых

следние содержат микрооперационную часть адрес (номер) модуля, которому передается управление: поле кода логических условий, в котором также как и у собственных линейных микрокоманд записаны нули, и адрес передачи управления, т.е. адрес начальной микрокоманды, в модуле, которому передается управление, У собственных микрокоманд в поле адреса модуля, которому передается управление, записаны нули, а в поле адреса передачи управления - косвенньтй адрес следующей

собственной микрокоманды, состоящий из двух частей: старших и младших разрядов. Это условное разделение сделано в целях- уменьшения разрядности сумматора, так как на вход сумматора для модификации адреса заводятся не все разряды косвенного адреса, а только часть - младшие разряды. Это накладывает определенные условия на размещение микрокоманд в блоке памя™.

В микрокомандах ветвления в поле кода логических условий задается но-- мер проверяемого логического, условия. При ветвлении и в случае единичного

значения проверяемого логического

условия происходит увеличение на единицу младших разрядов адреса, т,е. В случае, когда значение младших разрядов адреса меньше величины 2, где

а - количество младших разрядов кос- венного адреса микрокомавды. Микрокоманды, следующие после микрокоманды ветвления, должны располагаться в соседних ячейках блока памяти. В случае же равенства младших разрядов адреса величине при увеличении на единицу переноса единицы в следующий старший разряд не происходит, и таким образом значение младших разрядов адреса становится равным нулю. Таким образом в этом случае одна из микрокоманд, следующих за ветвлением, размещается в соответствии с кос- is ков элементов И, с первым входом элевенным адресом микрокоманды ветвления, а другая - в ячейке с адресом, у которого значение старших разрядов соответствует значению старших разрядов косвенного адреса микрокоманды ветвления, а младшие разряды равны нулю.

Для обеспечения динамической сме- ны (коррекции) микропрограмм осуществляется многофункциональное исполь зо1зание части выводов модуля, по которым в рабочем режиме циркулирует рабочая информация, и в режиме записи - адреса и микрокоманды .новой микропрограммы.

Ф ормула изобретения

Микропрограммный модуль, содержащий блок памяти микрокоманд, счетчик регистр микрокоманд, демультиплексор мультиплексор, триггер пуска, генератор тактовых импульсов, блок элементов ИЛИ, причем группа входов кода операций модуля соединена с первой группой входов блока элементов ИЛИ, выход которого соединен с информационным входом счетчика с (n-k)-ro по (п-1)-ый, группа информационных входов модуля соединены соответственно .с второй по (п-и-1)-ый группами входов блока элементов ИЛИ (где п - количество групп входов приема управления, k -количество входов приема

управления, прием информащю от кото- 50 информационным входом регистра

рых блокируется) вход пуска модуля соединен с единичньм входом триггера пуска, выход которого соединен с входом запуска генератора тактовых иммикрокоманд, выход поля кода логических условий блока памяти микрокоманд соединен с адресным входом мультиплек сора, выходы мультиплексора и поля

пульсов, первый выход генератора так- gg младших разрядов адреса блока памяти

товьк импульсов соединен с входом синхронизации счетчика, информациой- ный выход которого соединен с адресным входом блока памяти,микрокоманд.

вход логических условий модуля соединен с информационным входом мультиплексора, отличающийся тем, что, с целью расширения области применения за счет организации смены микропрограмм и уменьшения числа выводов модуля, он допапни- тельно содержит блок ключей с три- стабильным выходом, (k+1) блоков элементов И, элемент И, первый и второй элементы ШШ, сумматор, причем вход задания режима модуля соединен с входом с первого по (п+1)-ый бло0

g

мента-И, с входом задания режима работы Счетчика с входом разрешения записи регистра микрокоманд, с входом управления блока ключей с триста0 бильным выходом, со стробируюш 1м входом демультиплексора, выход поля адреса модуля блока памяти микрокоманд соединен с адресным входом демульти- плексора и с входом второго элемента

5 ИЛИ, выход которого соединен с вторым входом (k+1)-oro блока элементов И, с первого по k-ый входы приема управления модуля соединены с первой груп- пой информационных входов блока памя-

0 ти микрокоманд и с группой входов с первого по k блоков элементов И соответственно, выходы которых соединены- соответственно с (n-k)-ой по п-ую группами входов блока элементов ИЛИ, вход останова модуля соединен с первым входом первого элемента ИЛИ, выход д оторого соединен с входом установки в О триггера пуска, второй выход генератора тактовых импульсов соединен с вторым входом элемента И и с входом синхронизации регистра микрокоманд, выход которого соединен с информационным входом блока ключей с тристабильным выходом, выход которого соединен с информационным входом- выходом модуля и входами второй группы информационных входов блока памяти микрокоманд, выход поля микроопераций блока памяти микрокоманд соеди5

микрокоманд, выход поля кода логических условий блока памяти микрокоманд соединен с адресным входом мультиплексора, выходы мультиплексора и поля

микрокоманд соединены соответственно с первым и вторым входами сумматора, выход которого объединен с выходом поля старших разрядов адреса блока памяти микрокоманд и подключен к остальным входм (п+1)-ого блока элементов И и с информационным входом демульти- плексора, с первой по (п-1)-ую группы выходов которого являются выходами передачи управления модуля, выход (k+1)-oro блока элементов И соединен

с (п+1)-ой группой входов блока элементов ИЛИ, выход элемента И которого соединен с входом разрешения записи блока памяти микрокоманд, выход переполнения счетчика соединен с вторым входом первого элемента ИЛИ,

Фа.2

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1986-05-22—Подача