Изобретение относится к вычислительной технике и предназначено для использования в микропроцессорных устройствах с магистральной ,организацией внутреннего обмена данными.

Цель изобретения - упрощение и повышение быстродействия устройства.

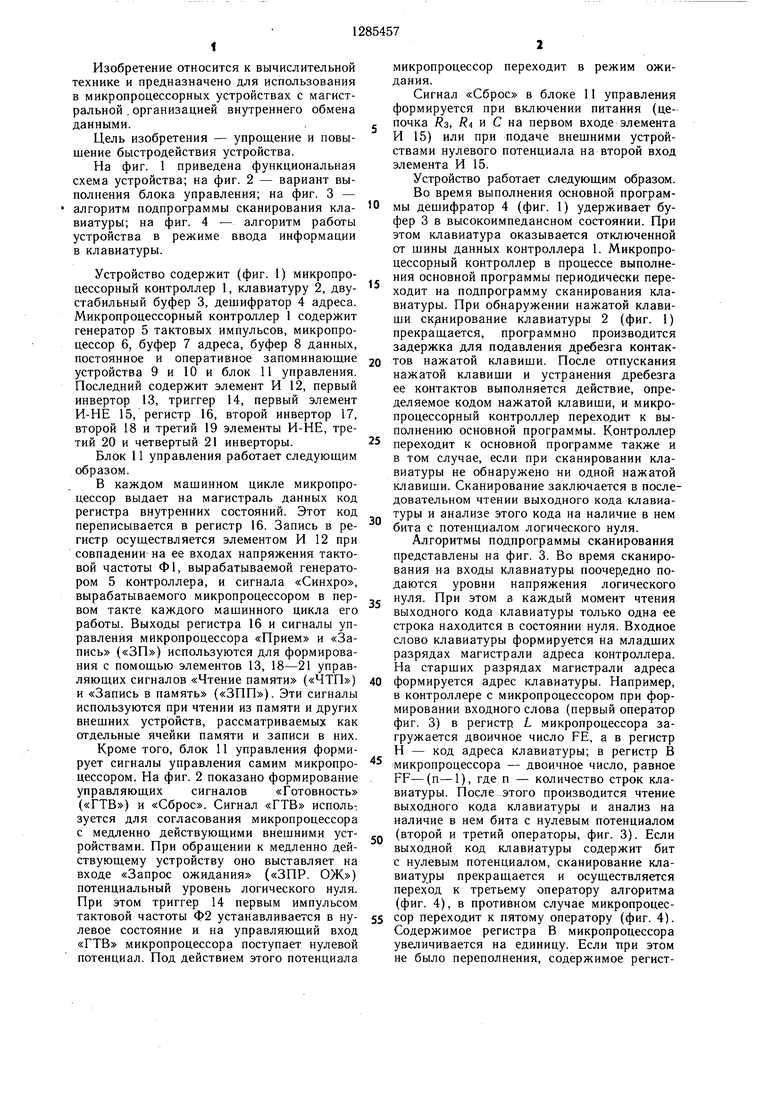

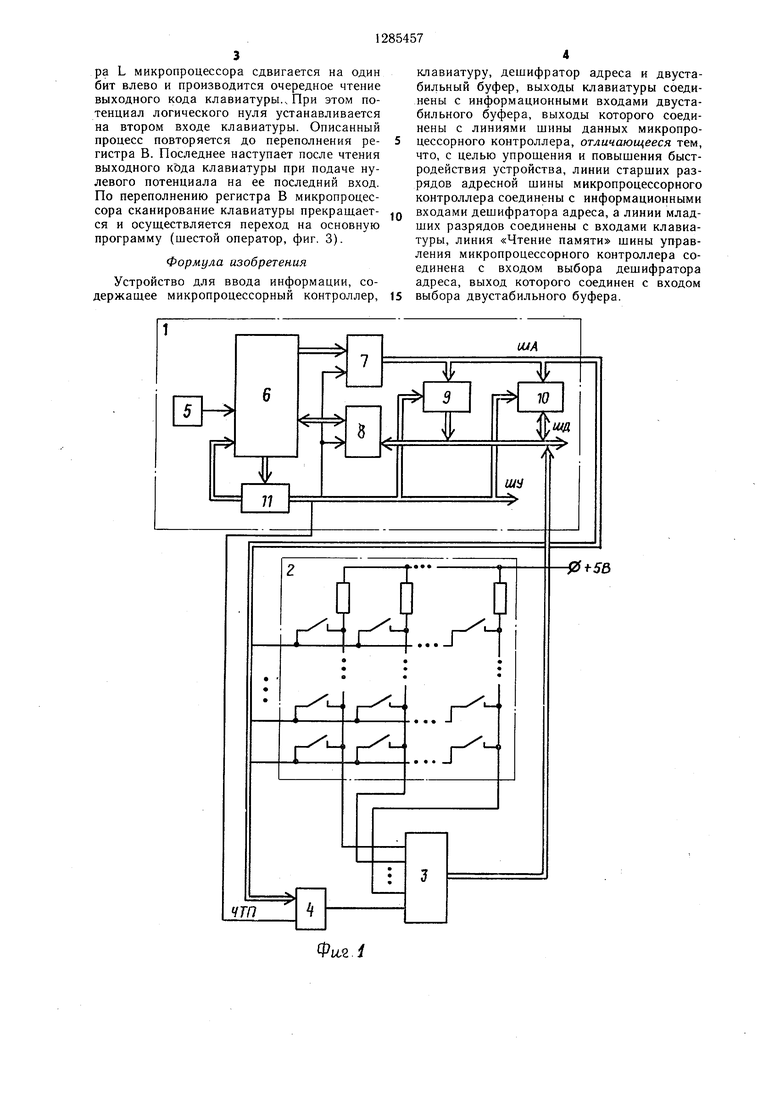

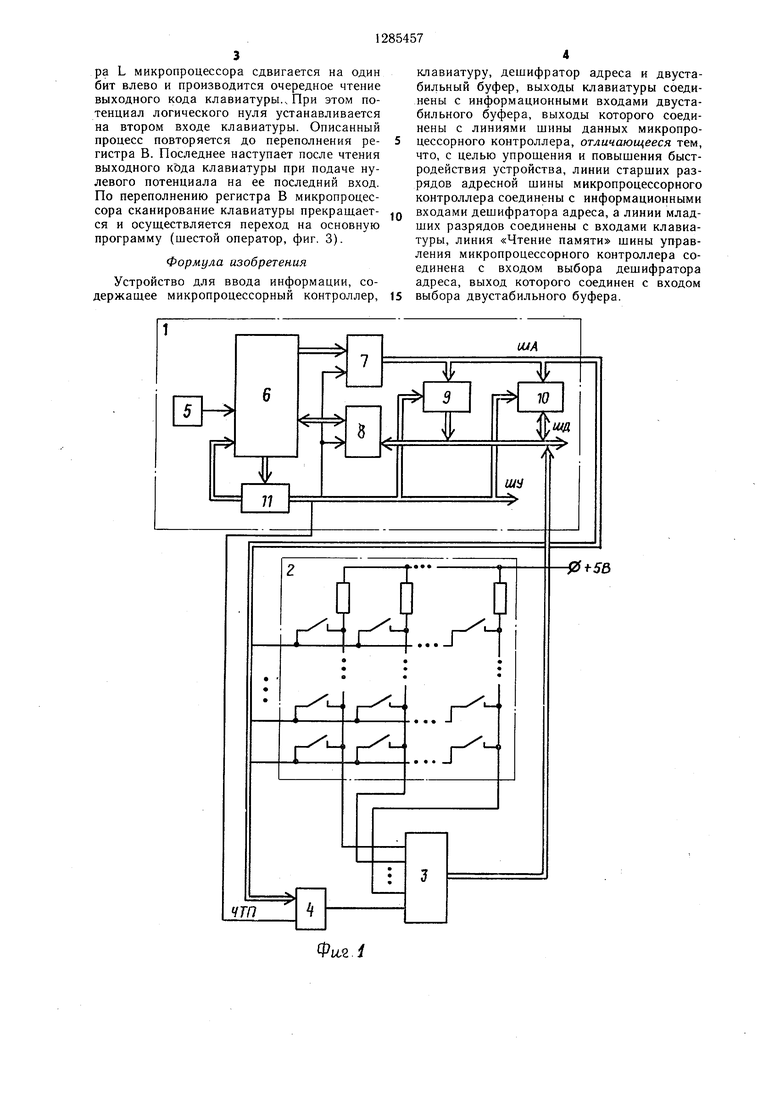

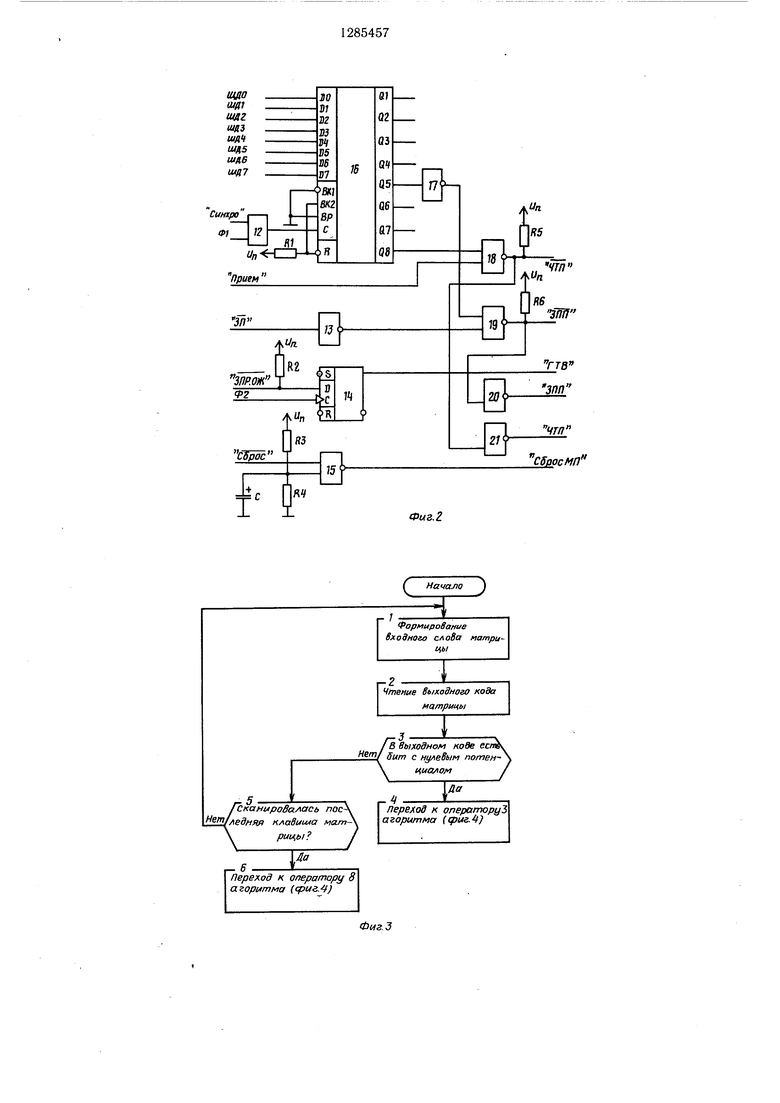

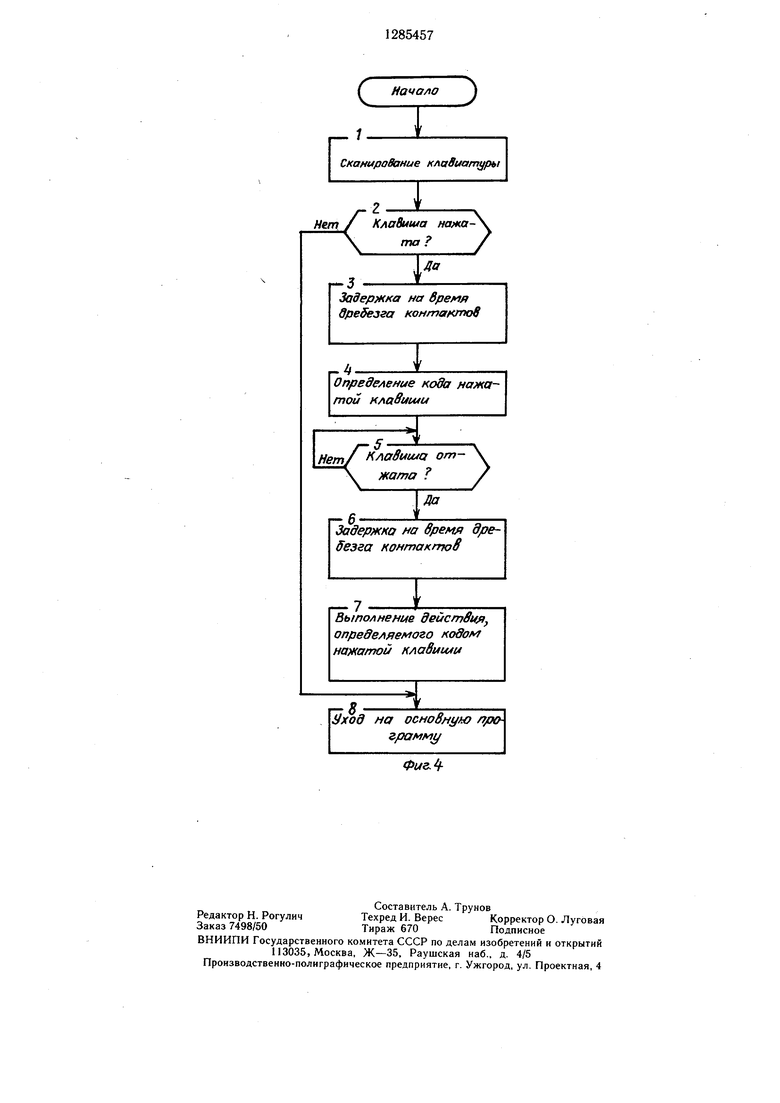

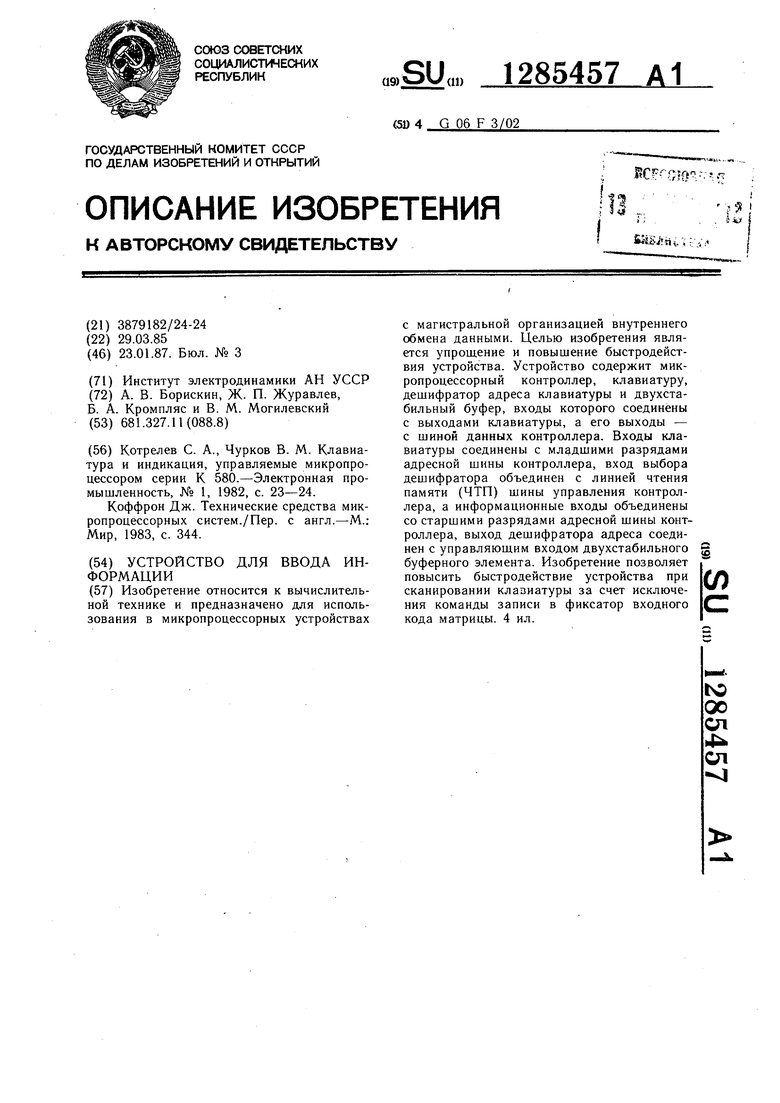

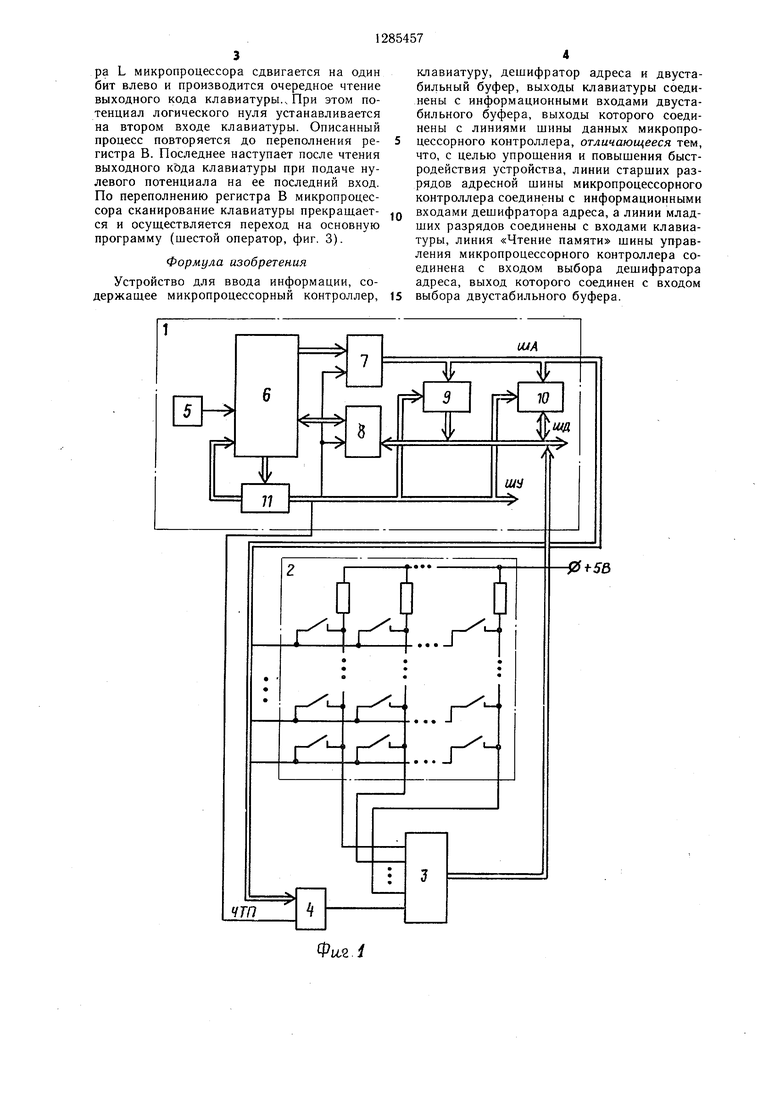

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - вариант выполнения блока управления; на фиг. 3 - алгоритм подпрограммы сканирования клавиатуры; на фиг. 4 - алгоритм работы устройства в режиме ввода информации в клавиатуры.

Устройство содержит (фиг. 1) микропроцессорный контроллер 1, клавиатуру 2, дву- стабильный буфер 3, дешифратор 4 адреса. Микропроцессорный контроллер 1 содержит генератор 5 тактовых импульсов, микропроцессор 6, буфер 7 адреса, буфер 8 данных, постоянное и оперативное запоминающие устройства 9 и 10 и блок 11 управления. Последний содержит элемент И 12, первый инвертор 13, триггер 14, первый элемент И-НЕ 15, регистр 16, второй инвертор 17, второй 18 и третий 19 элементы И-НЕ, третий 20 и четвертый 21 инверторы.

Блок 11 управления работает следующим образом.

В каждом машинном цикле микропроцессор выдает на магистраль данных код регистра внутренних состояний. Этот код переписывается в регистр 16. Запись в регистр осуществляется элементом И 12 при совпадении на ее входах напряжения тактовой частоты Ф1, вырабатываемой генератором 5 контроллера, и сигнала «Синхро, вырабатываемого микропроцессором в первом такте каждого машинного цикла его работы. Выходы регистра 16 и сигналы управления микропроцессора «Прием и «Запись («ЗП) используются для формирования с помощью элементов 13, 18-21 управляющих сигналов «Чтение памяти («ЧТП) и «Запись в память («ЗПП). Эти сигналы используются при чтении из памяти и других внещних устройств, рассматриваемых как отдельные ячейки памяти и записи в них.

Кроме того, блок 11 управления формирует сигналы управления самим микропроцессором. На фиг. 2 показано формирование управляющих сигналов «Готовность («ГТВ) и «Сброс. Сигнал «ГТВ испольт зуется для согласования микропроцессора с медленно действующими внещними устройствами. При обращении к медленно действующему устройству оно выставляет на входе «Запрос ожидания («ЗПР. ОЖ) потенциальный уровень логического нуля. При этом триггер 14 первым импульсом тактовой частоты Ф2 устанавливается в нулевое состояние и на управляющий вход «ГТВ микропроцессора поступает нулевой потенциал. Под действием этого потенциала

микропроцессор переходит в режим ожидания.

Сигнал «Сброс в блоке 11 управления формируется при включении питания (цепочка Rs, и С на первом входе элемента И 15) или при подаче внешними устройствами нулевого потенциала на второй вход элемента И 15.

Устройство работает следующим образом. Во время выполнения основной программы дешифратор 4 (фиг. 1) удерживает буфер 3 в высокоимпедансном состоянии. При этом клавиатура оказывается отключенной от шины данных контроллера 1. Микропроцессорный контроллер в процессе выполне- ния основной программы периодически переходит на подпрограмму сканирования клавиатуры. При обнаружении нажатой клавиши сканирование клавиатуры 2 (фиг. 1) прекрашается, программно производится задержка для подавления дребезга контак0 тов нажатой клавиши. После отпускания нажатой клавиши и устранения дребезга ее контактов выполняется действие, определяемое кодом нажатой клавиши, и микропроцессорный контроллер переходит к выполнению основной программы. Контроллер

5 переходит к основной программе также и в том случае, если при сканировании клавиатуры не обнаружено ни одной нажатой клавиши. Сканирование заключается в последовательном чтении выходного кода клавиатуры и анализе этого кода на наличие в нем бита с потенциалом логического нуля.

Алгоритмы подпрограммы сканирования представлены на фиг. 3. Во время сканирования на входы клавиатуры поочер.едно подаются уровни напряжения логического

- нуля. При этом 3 каждый момент чтения выходного кода клавиатуры только одна ее строка находится в состоянии нуля. Входное слово клавиатуры формируется на младших разрядах магистрали адреса контроллера. На старших разрядах магистрали адреса

0 формируется адрес клавиатуры. Например, в контроллере с микропроцессором при формировании входного слова (первый оператор фиг. 3) в регистр L микропроцессора загружается двоичное число FE, а в регистр Н - код адреса клавиатуры; в регистр В микропроцессора - двоичное число, равное FF-(п-1), где п - количество строк клавиатуры. После этого производится чтение выходного кода клавиатуры и анализ на наличие в нем бита с нулевым потенциалом

(второй и третий операторы, фиг. 3). Если выходной код клавиатуры содержит бит с нулевым потенциалом, сканирование клавиатуры прекращается и осуществляется переход к третьему оператору алгоритма (фиг. 4), в противном случае микропроцес5 сор переходит к пятому оператору (фиг. 4). Содержимое регистра В микропроцессора увеличивается на единицу. Если при этом не было переполнения, содержимое регист5

pa L микропроцессора сдвигается на один бит влево и производится очередное чтение выходного кода клавиатуры.. При этом потенциал логического нуля устанавливается на втором входе клавиатуры. Описанный процесс повторяется до переполнения ре- гистра В. Последнее наступает после чтения выходного кода клавиатуры при подаче нулевого потенциала на ее последний вход. По переполнению регистра В микропроцессора сканирование клавиатуры прекращает- ся и осуществляется переход па основную программу (щестой оператор, фиг. 3).

Формула изобретения

Устройство для ввода информации, содержащее микропроцессорный контроллер,

клавиатуру, дешифратор адреса и двуста- бильный буфер, выходы клавиатуры соединены с информационными входами двуста- бильного буфера, выходы которого соединены с линиями щины данных микропроцессорного контроллера, отличающееся тем, что, с целью упрощения и повыщения быстродействия устройства, линии старщих разрядов адресной щины микропроцессорного контроллера соединены с информационными входами дешифратора адреса, а линии младших разрядов соединены с входами клавиатуры, линия «Чтение памяти шины управления микропроцессорного контроллера соединена с входом выбора дешифратора адреса, выход которого соединен с входом выбора двустабильного буфера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1418727A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

Изобретение относится к вычислительной технике и предназначено для использования в микропроцессорных устройствах с магистральной организацией внутреннего обмена данными. Целью изобретения является упрощение и повышение быстродействия устройства. Устройство содержит микропроцессорный контроллер, клавиатуру, дешифратор адреса клавиатуры и двухста- бильный буфер, входы которого соединены с выходами клавиатуры, а его выходы - с шиной данных контроллера. Входы клавиатуры соединены с младшими разрядами адресной шины контроллера, вход выбора дешифратора объединен с линией чтения памяти (ЧТП) шины управления контроллера, а информационные входы объединены со старшими разрядами адресной шины контроллера, выход дешифратора адреса соединен с управляющим входом двухстабильного буферного элемента. Изобретение позволяет повысить быстродействие устройства при сканировании клавиатуры за счет исключения команды записи в фиксатор входного кода матрицы. 4 ил. (в (Л |С 00 ел сд |

1Г

Фил i

F

1

Сканирование клавиатуры

Нет

д°

г-5 - Задер)кка на время дребезга контактов

VonpedeAeHue кода нажа- той клавими

Нет/ 1 лаВиша отHem/ f

жата

Задержка на время дребезга контакгтюВ

Выполнение deucmSufl определяемого кодом нажатой клаВими

8,

на основную /ух г/замму

С

Начало

1

Клавиша

та

д°

а вре онта

лаВиша отжата

Фиг.

| Котрелев С | |||

| А., Чурков В | |||

| М | |||

| Клавиатура и индикация, управляемые микропроцессором серии К 580.-Электронная промышленность, № 1, 1982, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем./Пер | |||

| с англ.-М.: Мир, 1983, с | |||

| Способ получения жидкой протравы для основных красителей | 1923 |

|

SU344A1 |

Авторы

Даты

1987-01-23—Публикация

1985-03-29—Подача