Изобретение относится к области вычислительной техники и может быть использовано в специализированных быстродействующих вычислителях.

Цель изобретения - расширение функциональных возможностей за счет возможности вычисления выражения У

распределителя 1 импульсов формируется импульс, по которому осуществляется сдвиг информации на регистрах 5 сдвига, т. е. на выходе блока регистров сдвига - Хп-з. Аналогично вычисляются на схеме 4 вычисления квадратного корня из суммы квадратов двух чисел следующие значения Уз, которые записываются в регистр 6 суммы. Работа устройства заканчивается обработкой наибольшего числа.

-v xf+X2+...+X , |;,...1.1, начиная с младших чисел.

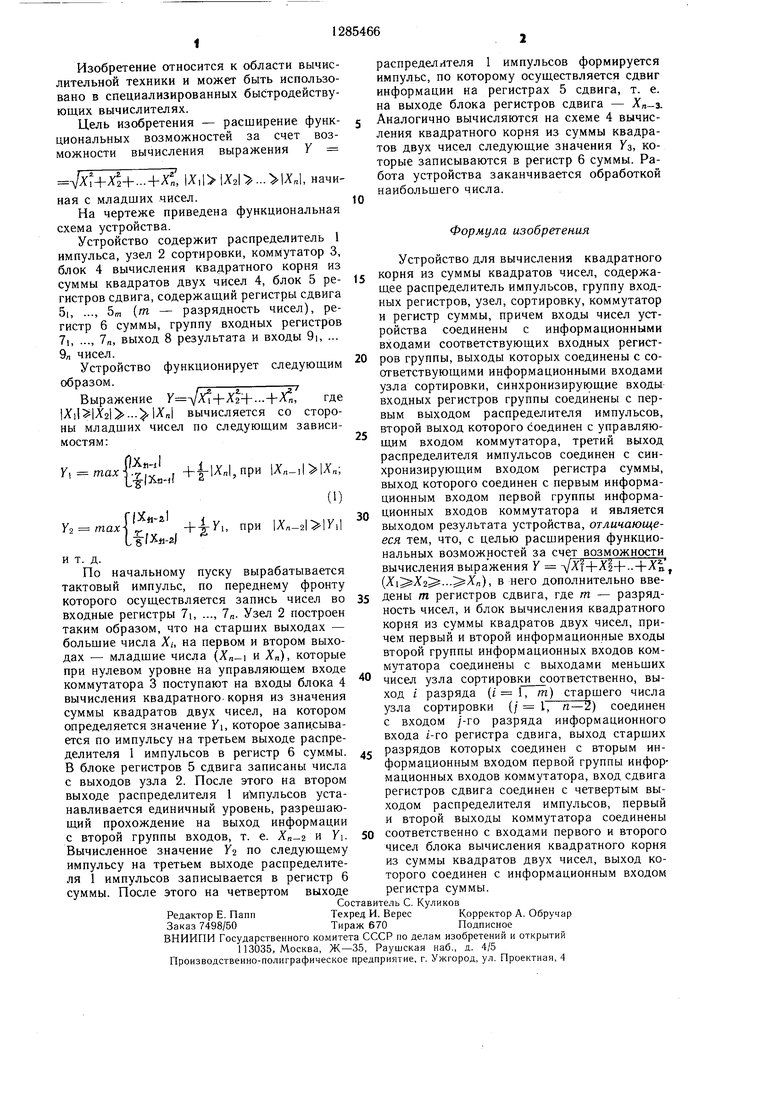

На чертеже приведена функциональная схема устройства.

Устройство содержит распределитель 1 импульса, узел 2 сортировки, коммутатор 3, блок 4 вычисления квадратного корня из суммы квадратов двух чисел 4, блок 5 ре- 15 Р « суммы квадратов чисел, содержа- ..щее распределитель импульсов, группу входФормула изобретения Устройство для вычисления квадратного

гистров сдвига, содержащий регистры сдвига 5i, ..., 5m (т - разрядность чисел), регистр 6 суммы, группу входных регистров 7i, ..., 7„, выход 8 результата и входы 9i, ... 9п чисел.

Устройство функционирует следующим образом.

Выражение y YXt+A 24--..-f, где IXiI ...1А „| вычисляется со стороны младших чисел по следующим зависимостям:

У max И +1-1Х„|,при 1Х„,

(1) У2 тах( +4-У,, при ,|

LffX«-2)

и Т. д.

По начальному пуску вырабатывается тактовый импульс, по переднему фронту которого осуществляется запись чисел во входные регистры 7i, ..., 7„. Узел 2 построен таким образом, что на старших выходах - большие числа Xi, на первом и втором выходах - младшие числа (Х„ и Хп), которые при нулевом уровне на управляющем входе коммутатора 3 поступают на входы блока 4 вычисления квадратного корня из значения суммы квадратов двух чисел, на котором определяется значение Уи которое записывается по импульсу на третьем выходе распределителя 1 импульсов в регистр 6 суммы. В блоке регистров 5 сдвига записаны числа с выходов узла 2. После этого на втором выходе распределителя 1 и1«пульсов устанавливается единичный уровень, разрешающий прохождение на выход информации с второй группы входов, т. е. Хп-г и Y. Вычисленное значение У2 по следующему импульсу на третьем выходе распределителя 1 импульсов записывается в регистр 6 суммы. После этого на четвертом выходе

25

ных регистров, узел, сортировку, коммутатор и регистр суммы, причем входы чисел устройства соединены с информационными входами соответствующих входных регист20 ров группы, выходы которых соединены с соответствующими информационными входами узла сортировки, синхронизирующие входы входных регистров группы соединены с первым выходом распределителя импульсов, второй выход которого соединен с управляющим входом коммутатора, третий выход распределителя импульсов соединен с синхронизирующим входом регистра суммы, выход которого соединен с первым информационным входом первой группы информа30 ционных входов коммутатора и является выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности вычисления выражения У - IX i- -Xl-{-.. (), в него дополнительно вве35 дены т регистров сдвига, где т - разрядность чисел, и блок вычисления квадратного корня из суммы квадратов двух чисел, причем первый и второй информационные входы второй группы информационных входов коммутатора соединены с выходами меньших чисел узла сортировки соответственно, выход i разряда (г 1, т) старшего числа узла сортировки (/ п-2) соединен с входом /-ГО разряда информационного входа г-го регистра сдвига, выход старших разрядов которых соединен с вторым информационным входом первой группы информационных входов коммутатора, вход сдвига регистров сдвига соединен с четвертым выходом распределителя импульсов, первый и второй выходы коммутатора соединены

50 соответственно с входами первого и второго чисел блока вычисления квадратного корня из суммы квадратов двух чисел, выход которого соединен с информационным входом

40

45

регистра суммы. Составитель С. Куликов Редактор Е. ПаппТехред И. ВересКорректор А. Обручар

Заказ 7498/50Тираж 670Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

распределителя 1 импульсов формируется импульс, по которому осуществляется сдвиг информации на регистрах 5 сдвига, т. е. на выходе блока регистров сдвига - Хп-з. Аналогично вычисляются на схеме 4 вычисления квадратного корня из суммы квадратов двух чисел следующие значения Уз, которые записываются в регистр 6 суммы. Работа устройства заканчивается обработкой наибольшего числа.

« суммы квадратов чисел, содержа- распределитель импульсов, группу входФормула изобретения Устройство для вычисления квадратного

ных регистров, узел, сортировку, коммутатор и регистр суммы, причем входы чисел устройства соединены с информационными входами соответствующих входных регистров группы, выходы которых соединены с соответствующими информационными входами узла сортировки, синхронизирующие входы входных регистров группы соединены с первым выходом распределителя импульсов, второй выход которого соединен с управляющим входом коммутатора, третий выход распределителя импульсов соединен с синхронизирующим входом регистра суммы, выход которого соединен с первым информационным входом первой группы информационных входов коммутатора и является выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности вычисления выражения У - IX i- -Xl-{-.. (), в него дополнительно введены т регистров сдвига, где т - разрядность чисел, и блок вычисления квадратного корня из суммы квадратов двух чисел, причем первый и второй информационные входы второй группы информационных входов коммутатора соединены с выходами меньших чисел узла сортировки соответственно, выход i разряда (г 1, т) старшего числа узла сортировки (/ п-2) соединен с входом /-ГО разряда информационного входа г-го регистра сдвига, выход старших разрядов которых соединен с вторым информационным входом первой группы информационных входов коммутатора, вход сдвига регистров сдвига соединен с четвертым выходом распределителя импульсов, первый и второй выходы коммутатора соединены

соответственно с входами первого и второго чисел блока вычисления квадратного корня из суммы квадратов двух чисел, выход которого соединен с информационным входом

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления выражения @ | 1985 |

|

SU1260950A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1984 |

|

SU1238065A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для вычисления квадратного корня из суммы квадратов трех чисел | 1985 |

|

SU1262488A1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1129610A1 |

| Устройство для вычисления квадрата и квадратного корня | 1983 |

|

SU1120320A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1986 |

|

SU1327097A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1987 |

|

SU1425663A1 |

| Устройство для вычисления зависимости @ | 1983 |

|

SU1145341A1 |

Изобретение относится к вычислительной технике и быть использовано в специализированных быстродействующих вычислителях. Целью изобретения является расширение функциональных возможностей за счет вычисления выражения У ..., ...|Х„|,.начиная с младших чисел. Устройство содержит распределитель 1 импульсов, узел 2 сортировки, коммутатор 3, блок 4 вычисления квадратного корня из суммы квадратов двух чисел, блок 5 регистров сдвига, регистр 6 суммы, группу входных регистров 7i, ..., 7п, выход 8 результата и входы 9i, ..., 9л чисел. Обработка чисел начинается с минимального числа, что позволяет получить большую точность вычислений. I ил. (б W с: ю 00 СП с

| Устройство для приближенного вычисления модуля комплексного числа | 1982 |

|

SU1070544A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции @ | 1984 |

|

SU1228100A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня из суммы квадратов чисел | 1984 |

|

SU1196854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-03-27—Подача