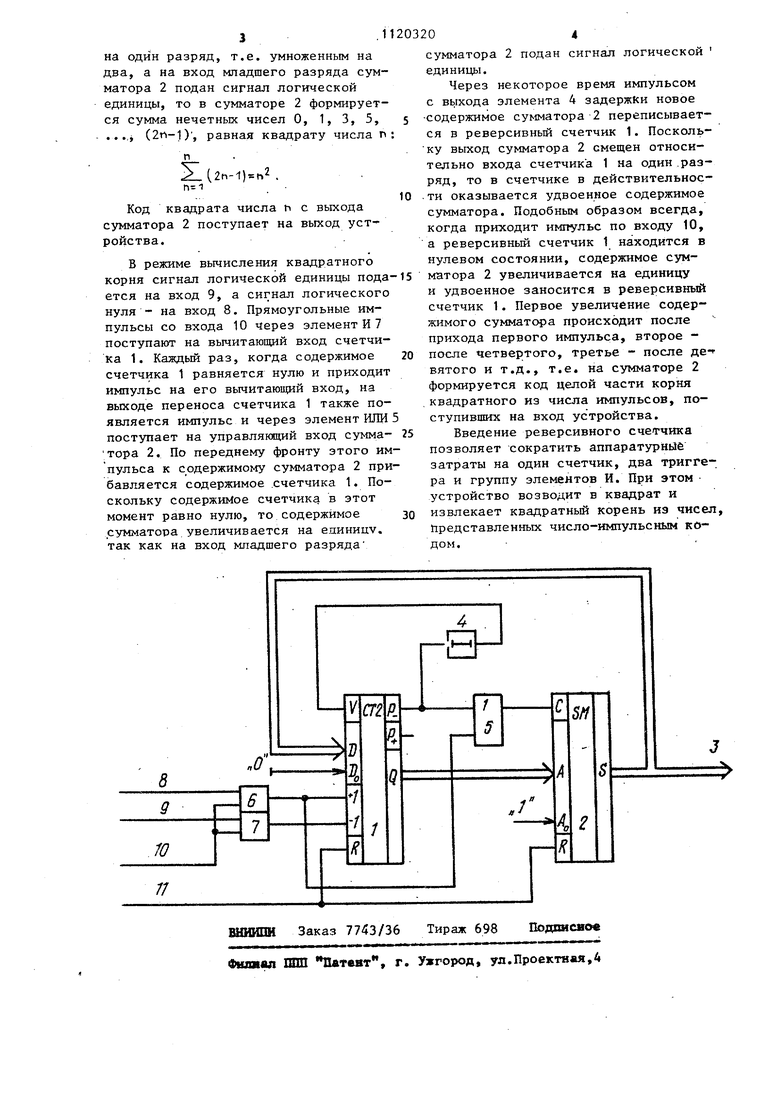

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных и функциональных устройствах, цифровых измерительных приборах для обработки информации, представленной число-импульсным кодом. Известно устройство для вычисления квадрата, содержащее два злемента И, два триггера, счетчик и накапливающий сумматор flj. - Однако данное устройство не . может извлекать квадратный корень. Наиболее близким к изобретению по технической сущности является устройство для возведения в квадрат и извлечение квадратного корня, содержащее два счетчика, накапливающий сумматор, группу элементов И, два элемента И, два триггера, элемент ИЛИ и элемент задержки, выходы первого счетчика соединены с первыми входами элементов И группы, выходы которых соединены с разрядными входами накапливающего сумматора, выход переполнения которого соединен с первым входомэлемента ИЛИ, выход которого соединен с тактовым входом первого триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом второго триггера, первым выходом второго элемента И, счетным входом второго счетчика и через элемент задержки с вторыми входами элементов И группы 2, Недостатком известного устройства является его сложность. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройство д,пя вычисления квадрата и квадратного корня, содержащее накапливающий сумматор, элемент JUffl, элемент за,цержки и два элемента И, введен реверсивный счет чик, разрядные выходы которого соединены со сдвигом на один разряд в сторону старших разрядов с разрядны ми входами накапливающего сумматора младший разряд которого соединен с входом логической единицы устройств выходы результата накапливанщего су матора соединены со сдвигом на один разряд в сторону старших разрядов с разрядными входами реверсивного сче чика и являются выходами результата устройства, вход мпадшего разряда которого соедин ;н с входо,-) пог 1ческого нуля устройства, вход приема информации накапливающего с,уммат(5ра соединен с выходом элемента ILO-I, первый вход которого соединен с выходом первого элемента И и суммирующим входом реверсивного счетчика,, вычитающий вход которого соединен с выходом второго элемента И, первый вход которого соединен с первь м входом второго элемента и и информационным входом устройствз-j первый и второй входы задания режима которого соединены соотВетственно с вторыми входами первого и второго элемен:тов И,, выход отрицательного переполнения реверсивного счетчика соединен с вторьм входом ;элемента ИЛИ и через элемент згщержкН со своим входом разрешения приема кйда, входы усгановки нуля реверсивного счетчика и накапливающего сумматора соединены с входом сброса устройства. На чертеже приведена блок-схема предлагаемого устройства Устройство содержит реверскгньш счетчик 1, накапливающий сумматор 2, выход 3, эпегтент 4 задержки, элемент ИЛИ 5, элементы И 6 и 7 первый 8 и второй 9 управляющие входы, информационный вход 10 и вход 11 сброса. Устройство работает следую1дим образомПеред началом работы счетчик 1 и сумматор 2 устаназлкваются в нулеsoe состояние сигналом, приходящим по .входу 11 сброса.Устанавливается режим работы устройства В режиме вычисления квадрата на вход 9 подается сигнагг логического нуля, а на вход 8 - сигнал логической единицы. Входные прямоугольные импульсы, представля).адие число-импульсный код входного числа, с входа 10 через от крытый элемент И 6 поступают на йумг ирующий вход счетчика 1 и через элемент ИГОЯ 5 на вход cyt iaTopa 2. По переднему фронту прямоугольных импульсов к coдepжимo ry сумматора 2 прибавляется содержимое счетчика 1., а по зa :fнe:; y фронту содержимое счетчика t увеличивается: на единицу. После прихода по входу 10h прямоугольньп г 1ульсов- содержимое счетчика 1 увеличивается до ве.1ичины п . Поскольку со.цержимое счетчика 1 попадает на ззход с т-п 1аторе. 2 смещгнным на один разряд, т.е. умноженным на два, а на вход младшего разряда сумматора 2 подан сигнал логической единицы, то в сумматоре 2 формируется сумма нечетных чисел О, 1, 3, 5, .. .,j () равная квадрату числа г п 5l(2h-1) h2 Код квадрата числа п с выхода сумматора 2 поступает на выход уст ройства. В режиме вычисления квадратного корня сигнал логической единицы пода ется на вход 9, а сигнал логического нуля - на вход 8. Прямоугольные импульсы со входа 10 через элемент И 7 поступают на вычитающий вход счетчика 1. Каждый раз, когда содержимое счетчика 1 равняется нулю и приходит импульс на его вычитающий вход, на выходе переноса счетчика 1 также появляется импульс и через элемент ИЛИ поступает на управляющий вход сумматора 2. По переднему фронту этого им пульса к содержимому сумматора 2 при бавляется содержимое .счетчика 1. Поскольку содержимое счетчика в этот момент равно нулю, то содержимое сумматора увеличивается на единицу. так как на вход младшего разряда .1 04 сумматора 2 подан сигнал логической единицы. Через некоторое время импульсом с выхода элемента 4 задержки новое -содержимое сумматора 2 переписывается в реверсивный счетчик 1. Поскольку выход сумматора 2 смещен относительно входа счетчика 1 на один .разряд, то в счетчике в действительности оказывается удвоенное содержимое сумматора. Подобным образом всегда, когда приходит импульс по входу 10, а реверсивный счетчик 1 находится в нулевом состоянии, содержимое сумматора 2 увеличивается на единицу и удвоенное заносится в реверсивный счетчик 1. Первое увеличение содержимого сумматора происходит после прихода первого импульса, второе после четвертого, третье - после дет вятого и т.д., т.е. на сумматоре 2 формируется код целой части корня квадратного из числа импульсов, поступивших на вход устройства. Введение реверсивного счетчика позволяет сократить аппаратурное затраты на один счетчик, два триггера и группу элементов И. При этом устройство возводит в квадрат и извлекает квадратный корень иэ чисел, Представленных число-импульсным кодом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадрата и квадратного корня | 1987 |

|

SU1550512A1 |

| Устройство для вычисления квадрата и квадратного корня | 1986 |

|

SU1386991A2 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1113799A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для вычисления квадратногоКОРНя | 1979 |

|

SU809172A1 |

| Устройство для возведения в квадрат М-разрядных двоичных чисел | 1986 |

|

SU1399733A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТА И КВАДРАТНОГО КОРНЯ, содержащее накапливающий сумматор, элемент ИЛИ, элемент задержки и два элемента И, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит реверсивный счетчик, разрядные выходы которого соединены со сдвигом на один разряд в сторону старщих разрядов с разрядными входами накапливающего сумматора, младший разряд которого соединен с входом логической единицы устройства, выходы результата накапливающего сумматора соединены со с сдвигом на один разряд в сторону старших разрядов с разрядными входами реверсивного счетчика и являются выходами результата устройства, вход младшего разряда которого соединен с входом логического нуля устройства, вход приема информации накапливающего сумматора соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом первого элемента И и суммирующим входом реверсивного счетчика, вычитаклций вход которого соединен с вькодом второго элемента И, первый вход которого соединен с первым входом второго элемента И и информационным входом устройства, первый и второй входы задания режима которого соединены соответст(Л венно с вторыми входами первого и второго элементов И, выход отрицательного переполнения реверсивного счетчика соединен с вторым входом элемента ИЛИ и через элемент задержки с своим входом разрешения приема кода, входы установки нуля реверсивного счетчика и накапливающего сумматора соединены с входом сброса устройства.

.0

«г

-9

8

/ ff

Sff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления квадрата число-импульсного кода | 1980 |

|

SU881740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мельников А.А | |||

| и др | |||

| Обработка частотных -и временных импульсных сигналов | |||

| М., Энергия, 1976, с.89 | |||

Авторы

Даты

1984-10-23—Публикация

1983-06-24—Подача