Изобретение относится к вычислительной технике и может быть использовано в технике микроЭВМ при сопряжении 8-разрядного микропроцессора с 16-разрядными абонентами.

Цель изобретения - повышение быстродействия.

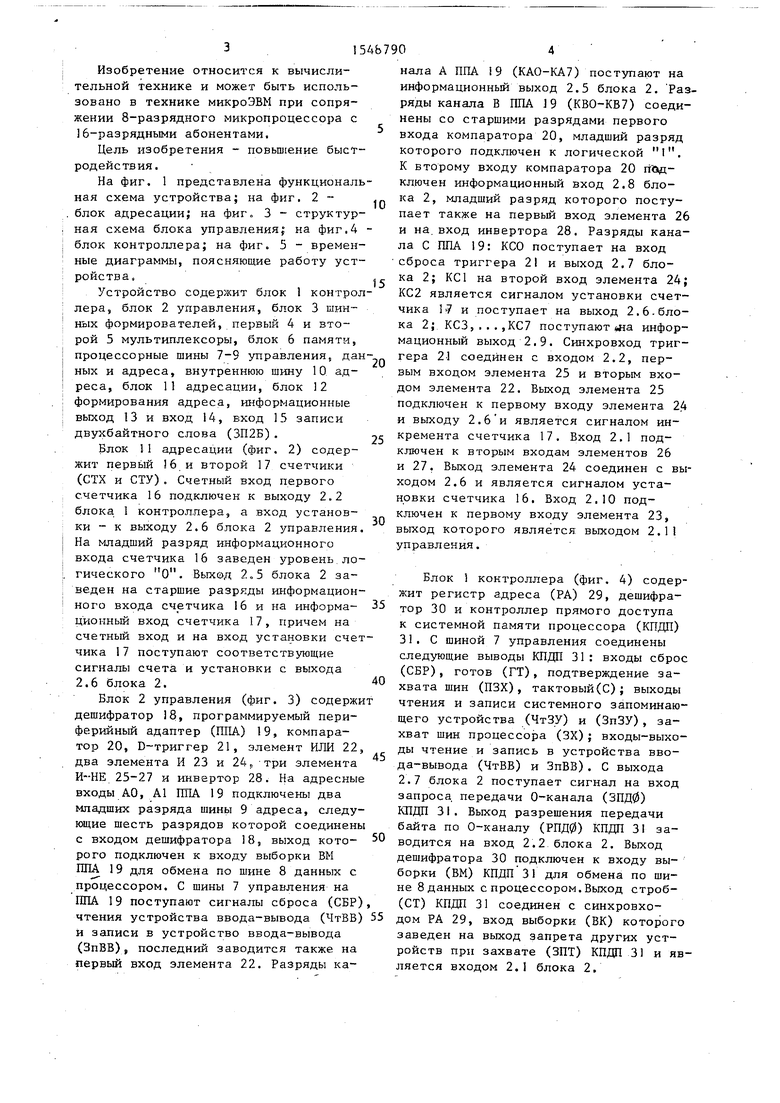

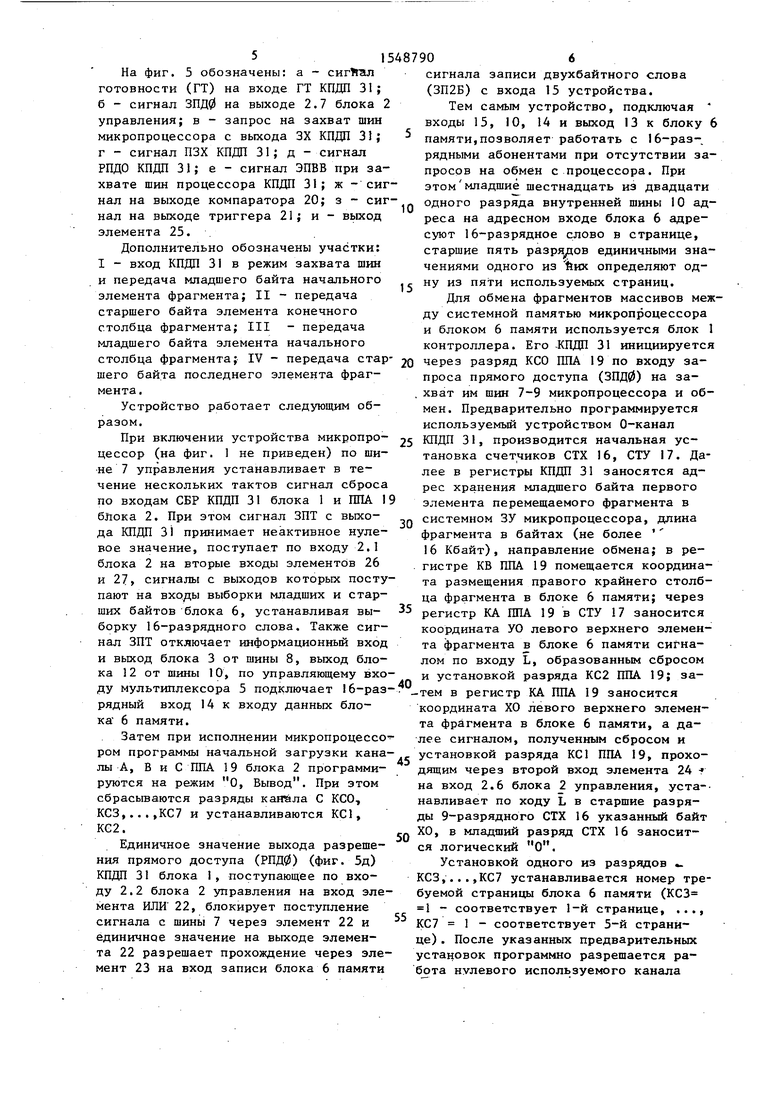

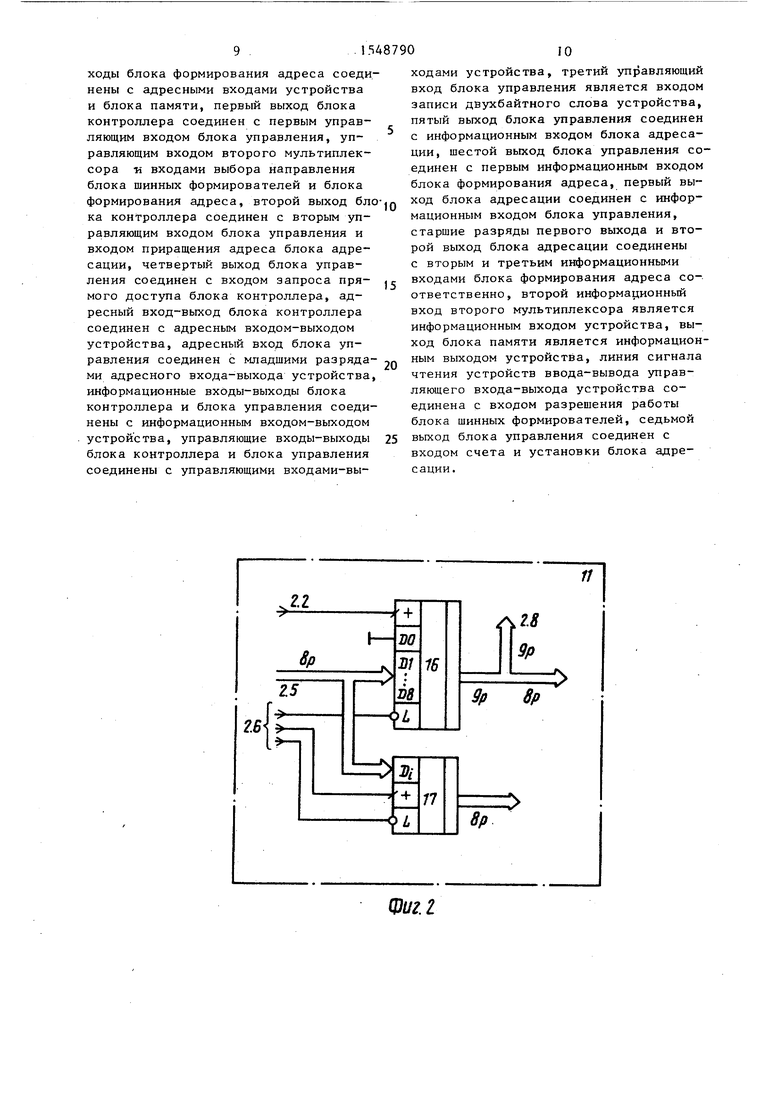

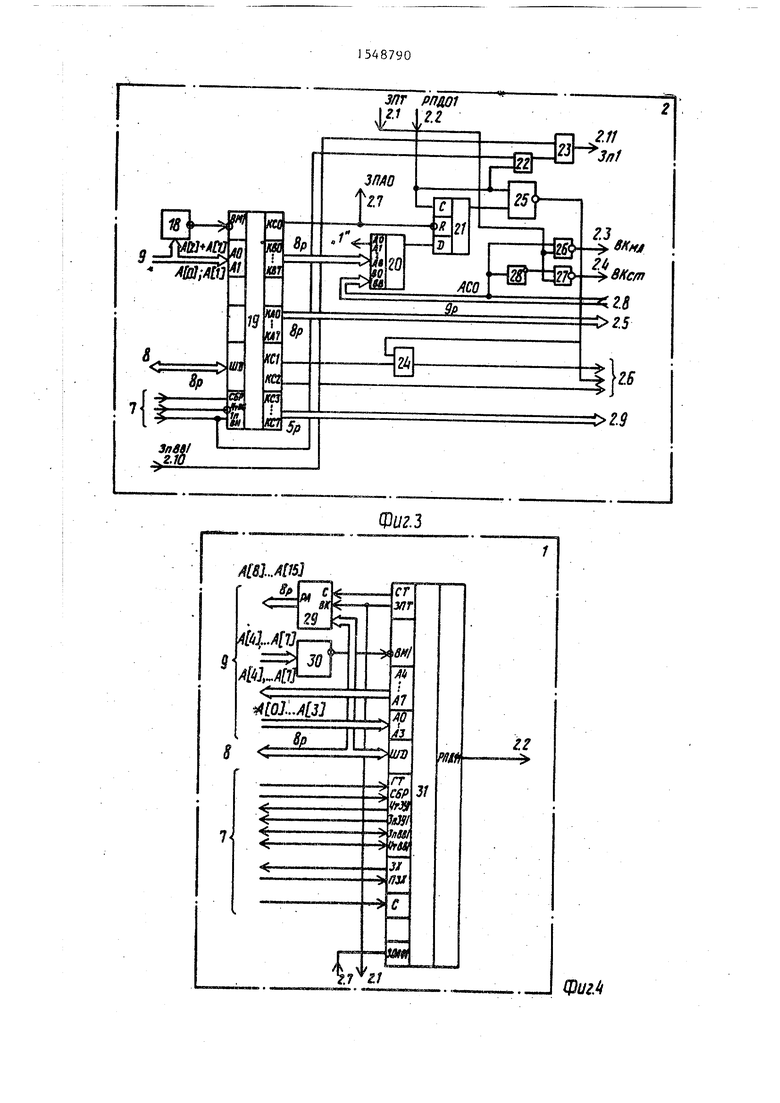

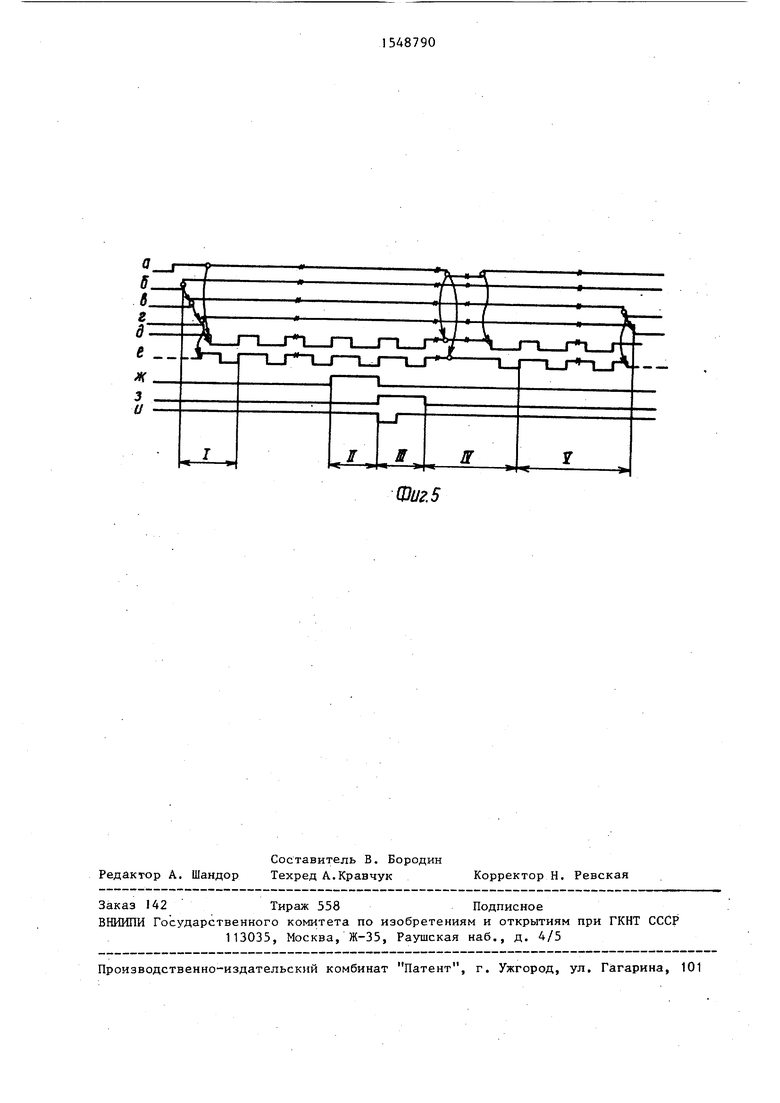

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - , блок адресации} на фиг. 3 - структурная схема блока управления; на фиг.4 - блок контроллера; на фиг. 5 - временные диаграммы, поясняющие работу устройства.|г

Устройство содержит блок 1 контроллера, блок 2 управления, блок 3 шинных формирователей, первый 4 и второй 5 мультиплексоры, блок 6 памяти, процессорные шины 7-9 управления, данных и адреса, внутреннюю шину 10 адреса, блок И адресации, блок 12 формирования адреса, информационные выход 13 и вход 14, вход 15 записи двухбайтного слова (ЗП2Б).

Блок 11 адресации (фиг. 2) содержит первый 16 и второй 17 счетчики (СТХ и СТУ). Счетный вход первого счетчика 16 подключен к выходу 2,2 блока 1 контроллера, а вход установки - к выходу 2.6 блока 2 управления. На младший разряд информационного входа счетчика 16 заведен уровень логического О. Выход 2.5 блока 2 заведен на старшие разряды информационнала А ППА 19 (КАО-КА7) поступают на информационньй выход 2.5 блока 2. Ра ряды канала В ППА J9 (КВО-КВ7) соеди нены со старшими разрядами первого входа компаратора 20, младший разряд которого подключен к логической 1м К второму входу компаратора 20 подключен информационный вход 2.8 блока 2, младший разряд которого поступает также на первый вход элемента 2 и на вход инвертора 28. Разряды кана ла С ППА 19: КСО поступает на вход сброса триггера 21 и выход 2.7 блока 2; КС1 на второй вход элемента 24 КС2 является сигналом установки счет чика Ь7 и поступает на выход 2.6.бло ка 2; КСЗ,...,КС7 поступают на инфор мационный выход 2.9. Синхровход триг гера 21 соединен с входом 2.2, первым входом элемента 25 и вторым входом элемента 22. Выход элемента 25 подключен к первому входу элемента 2 и выходу 2.6 и является сигналом инкремента счетчика 17. Вход 2.1 подключен к вторым входам элементов 26 и 27. Выход элемента 24 соединен с в ходом 2.6 и является сигналом установки счетчика 16. Вход 2.10 подключен к первому входу элемента 23, выход которого является выходом 2.11 управления.

25

30

Блок 1 контроллера (фиг. 4) соде жит регистр адреса (РА) 29, дешифра

ного входа счетчика 16 и на информа- 35 ТОр зо и контроллер прямого доступа

45

циопный вход счетчика 17, причем на счетный вход и на вход установки счетчика 17 поступают соответствующие сигналы счета и установки с выхода 2.6 блока 2.40

Блок 2 управления (фиг. 3) содержит дешифратор 18, программируемый периферийный адаптер (ППА) 19, компаратор 20, D-триггер 21, элемент ИЛИ 22, два элемента И 23 и 24„ три элемента И--НЕ 25-27 и инвертор 28. На адресные входы АО, А1 ППА 19 подключены два младших разряда шины 9 адреса, следующие шесть разрядов которой соединены с входом дешифратора 18, выход которого подключен к входу выборки ВМ ППА 19 для обмена по шине 8 данных с процессором. С шины 7 управления на ППА 19 поступают сигналы сброса (СБР),

50

к системной памяти процессора (КПДП 31. С шиной 7 управления соединены следующие выводы КПДП 31: входы сбр (СБР), готов (ГТ), подтверждение за хвата шин (ПЗХ), тактовый(С); выходы чтения и записи системного запоминаю щего устройства (ЧтЗУ) и (ЗпЗУ), захват шин процессора (ЗХ); входы-выхо ды чтение и запись в устройства ввода-вывода (ЧтВВ) и ЗпВВ). С выхода 2.7 блока 2 поступает сигнал на вход запроса передачи 0-канала (ЗПД0) КПДП 3I. Выход разрешения передачи байта по 0-каналу (РПД0) КПДП 31 заводится на вход 2.2 блока 2. Выход дешифратора 30 подключен к входу выборки (ВМ) КПДП 31 для обмена по шине 8 данных с процессором.Выход строб- (СТ) КПДП 31 соединен с синхровхочтения устройства ввода-вывода (ЧтВВ) 55 дом РА 29, вход выборки (ВК) которого

,|г

Ь7904

нала А ППА 19 (КАО-КА7) поступают на информационньй выход 2.5 блока 2. Разряды канала В ППА J9 (КВО-КВ7) соединены со старшими разрядами первого входа компаратора 20, младший разряд которого подключен к логической 1м. К второму входу компаратора 20 подключен информационный вход 2.8 блока 2, младший разряд которого поступает также на первый вход элемента 26 и на вход инвертора 28. Разряды канала С ППА 19: КСО поступает на вход сброса триггера 21 и выход 2.7 блока 2; КС1 на второй вход элемента 24; КС2 является сигналом установки счетчика Ь7 и поступает на выход 2.6.блока 2; КСЗ,...,КС7 поступают на информационный выход 2.9. Синхровход триггера 21 соединен с входом 2.2, первым входом элемента 25 и вторым входом элемента 22. Выход элемента 25 подключен к первому входу элемента 24 и выходу 2.6 и является сигналом инкремента счетчика 17. Вход 2.1 подключен к вторым входам элементов 26 и 27. Выход элемента 24 соединен с выходом 2.6 и является сигналом установки счетчика 16. Вход 2.10 подключен к первому входу элемента 23, выход которого является выходом 2.11 управления.

25

30

Блок 1 контроллера (фиг. 4) содержит регистр адреса (РА) 29, дешифраТОр зо и контроллер прямого доступа

5

0

0

к системной памяти процессора (КПДП) 31. С шиной 7 управления соединены следующие выводы КПДП 31: входы сброс (СБР), готов (ГТ), подтверждение захвата шин (ПЗХ), тактовый(С); выходы чтения и записи системного запоминающего устройства (ЧтЗУ) и (ЗпЗУ), захват шин процессора (ЗХ); входы-выходы чтение и запись в устройства ввода-вывода (ЧтВВ) и ЗпВВ). С выхода 2.7 блока 2 поступает сигнал на вход запроса передачи 0-канала (ЗПД0) КПДП 3I. Выход разрешения передачи байта по 0-каналу (РПД0) КПДП 31 заводится на вход 2.2 блока 2. Выход дешифратора 30 подключен к входу выборки (ВМ) КПДП 31 для обмена по шине 8 данных с процессором.Выход строб- (СТ) КПДП 31 соединен с синхровхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| Устройство для ввода информации | 1987 |

|

SU1531082A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

Изобретение относится к вычислительной технике и может быть использовано в технике микроЭВМ при сопряжении 8-разрядного микропроцессора с 16-разрядными абонентами. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 контролера, блок 2 управления, блок 3 шинных формирователей, мультиплексоры 4 и 5, блок 6 памяти, блок 11 адресации и блок 12 формирования адреса. Доступ 8-разрядного микропроцессора к устройству осуществляется по шинам 7, 8 и 9. Устройство позволяет обмениваться информацией системной памяти микропроцессора с блоком 6 памяти. За один цикл подготовки блока 1 контроллера возможна передача до 16 Кбайт информации между системной памятью микропроцессора и блоком 6 памяти. 5 ил.

и записи в устройство ввода-вывода (ЗпВВ), последний заводится также на первый вход элемента 22. Разряды казаведен на выход запрета других устройств при захвате (ЗПТ) КПДП 31 и является входом 2.1 блока 2.

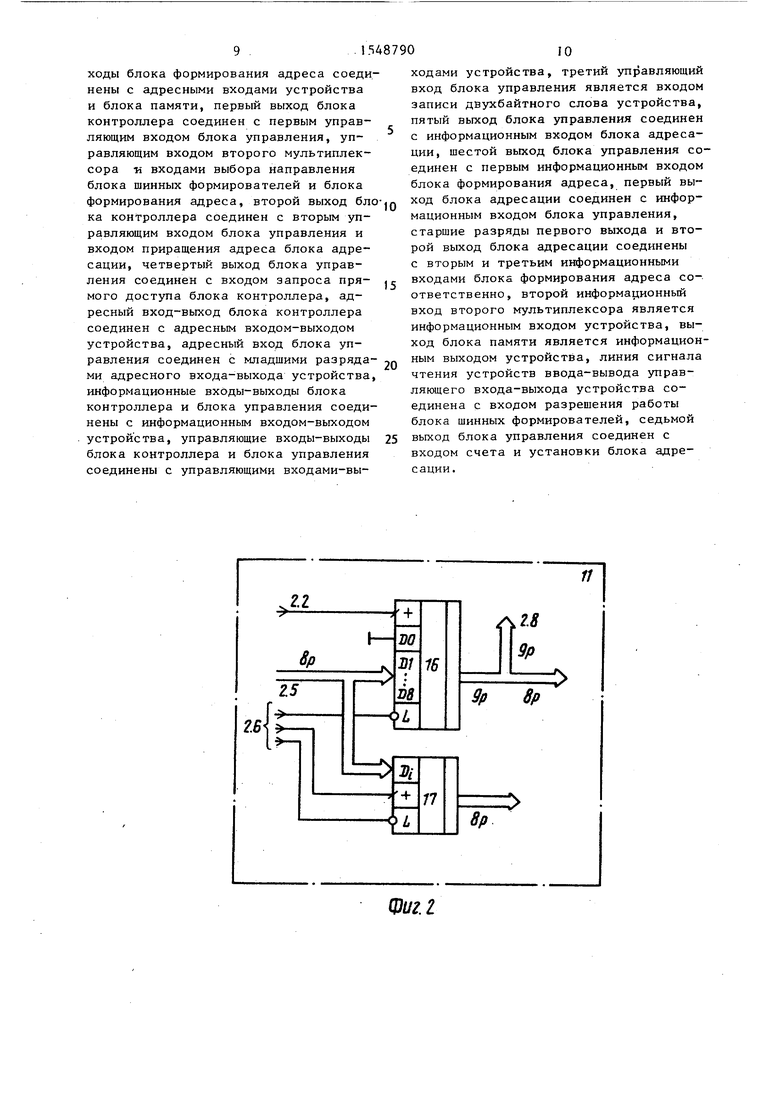

На фиг. 5 обозначены: а - сигнал готовности (ГТ) на входе ГТ КПДП 31; б - сигнал ЗПД0 на выходе 2.7 блока 2 управления; в - запрос на захват шин микропроцессора с выхода ЗХ КПДП 31; г - сигнал ПЗХ КПДП 31; д - сигнал РПДО КПДП 31; е - сигнал ЭПВВ при захвате шин процессора КПДП 31; ж - сигнал на выходе компаратора 20; з - сигнал на выходе триггера 21; и - выход элемента 25.

Дополнительно обозначены участки: I - вход КПДП 31 в режим захвата шин и передача младшего байта начального элемента фрагмента; II - передача старшего байта элемента конечного столбца фрагмента; III - передача младшего байта элемента начального столбца фрагмента; IV - передача старшего байта последнего элемента фрагмента .

Устройство работает следующим образом.

При включении устройства микропроцессор (на фиг. 1 не приведен) по шине 7 управления устанавливает в течение нескольких тактов сигнал сброса по входам СВР КПДП 31 блока 1 и ППА 19 блока 2. При этом сигнал ЗПТ с выхода КПДП 31 принимает неактивное нулевое значение, поступает по входу 2.1 блока 2 на вторые входы элементов 26 и 27, сигналы с выходов которых поступают на входы выборки младших и старших байтов блока 6, устанавливая выборку 16-разрядного слова. Также сигнал ЗПТ отключает информационный вход и выход блока 3 от шины 8, выход бло10

15

20

сигнала записи двухбайтного слова (ЗП2Б) с входа 15 устройства.

Тем самым устройство, подключая входы 15, 10, 14 и выход 13 к блоку памяти,позволяет работать с 16-раз- рядными абонентами при отсутствии за просов на обмен с процессора. При этом младшие шестнадцать из двадцати одного разряда внутренней шины 10 адреса на адресном входе блока 6 адресуют 16-разрядное слово в странице, старшие пять разрядов единичными значениями одного из них определяют одну из пяти используемых страниц.

Для обмена фрагментов массивов меж ду системной памятью микропроцессора и блоком 6 памяти используется блок контроллера. Его КПДП 31 инициируется через разряд КСО ППА 19 по входу запроса прямого доступа (ЗПД0) на захват им шин 7-9 микропроцессора и обмен. Предварительно программируется используемый устройством 0-канал

25 КПДП 31, производится начальная установка счетчиков СТХ 16, СТУ 17. Далее в регистры КПДП 31 заносятся адрес хранения младшего байта первого элемента перемещаемого фрагмента в системном ЗУ микропроцессора, длина фрагмента в байтах (не более 16 Кбайт), направление обмена; в регистре KB ППА 19 помещается координата размещения правого крайнего столбца фрагмента в блоке 6 памяти; через

35 регистр КА ППА 19 в СТУ 17 заносится координата УО левого верхнего элемента фрагмента в блоке 6 памяти сигналом по входу L, образованным сбросом и установкой разряда КС2 ППА 19; за30

ка 12 от шины 10, по управляющему вхо- „ „„ .,,

ду мультиплексора 5 подключает 16-раз-40 тем в регистр КА ППА 19 заносится рядный вход 14 к входу данных бло- координата ХО левого верхнего элемен- ка- 6 памяти.

Затем при исполнении микропроцессором программы начальной загрузки каналы А, В и С ППА 19 блока 2 программи45

та фрагмента в блоке 6 памяти, а далее сигналом, полученным сбросом и установкой разряда КС1 ППА 19, проходящим через второй вход элемента 24 - на вход 2.6 блока 2 управления, устанавливает по ходу L в старшие разряды 9-разрядного СТХ 16 указанный байт ХО, в младший разряд СТХ 16 заносится логический О.

руются на режим О, Вывод. При этом сбрасываются разряды канала С КСО, КСЗ,...,КС7 и устанавливаются КС1, КС2.

Единичное значение выхода разрешения прямого доступа (РПД0) (фиг. 5д) КПДП 31 блока 1, поступающее по входу 2.2 блока 2 управления на вход элемента ИЛИ 22, блокирует поступление сигнала с шины 7 через элемент 22 и единичное значение на выходе элемента 22 разрешает прохождение через элемент 23 на вход записи блока 6 памяти

0

5

0

сигнала записи двухбайтного слова (ЗП2Б) с входа 15 устройства.

Тем самым устройство, подключая входы 15, 10, 14 и выход 13 к блоку 6 памяти,позволяет работать с 16-раз- рядными абонентами при отсутствии запросов на обмен с процессора. При этом младшие шестнадцать из двадцати одного разряда внутренней шины 10 адреса на адресном входе блока 6 адресуют 16-разрядное слово в странице, старшие пять разрядов единичными значениями одного из них определяют одну из пяти используемых страниц.

Для обмена фрагментов массивов между системной памятью микропроцессора и блоком 6 памяти используется блок 1 контроллера. Его КПДП 31 инициируется через разряд КСО ППА 19 по входу запроса прямого доступа (ЗПД0) на захват им шин 7-9 микропроцессора и обмен. Предварительно программируется используемый устройством 0-канал

5 КПДП 31, производится начальная установка счетчиков СТХ 16, СТУ 17. Далее в регистры КПДП 31 заносятся адрес хранения младшего байта первого элемента перемещаемого фрагмента в системном ЗУ микропроцессора, длина фрагмента в байтах (не более 16 Кбайт), направление обмена; в регистре KB ППА 19 помещается координата размещения правого крайнего столбца фрагмента в блоке 6 памяти; через

5 регистр КА ППА 19 в СТУ 17 заносится координата УО левого верхнего элемента фрагмента в блоке 6 памяти сигналом по входу L, образованным сбросом и установкой разряда КС2 ППА 19; за0

„ „„ .,,

в регистр КА ППА 19 заносится координата ХО левого верхнего элемен-

тем в регистр КА ППА 19 заносится координата ХО левого верхнего элемен-

та фрагмента в блоке 6 памяти, а далее сигналом, полученным сбросом и установкой разряда КС1 ППА 19, прохо

дящим через второй вход элемента 24 - на вход 2.6 блока 2 управления, устанавливает по ходу L в старшие разряды 9-разрядного СТХ 16 указанный байт ХО, в младший разряд СТХ 16 заносится логический О.

Установкой одного из разрядов .. КСЗ,...,КС7 устанавливается номер требуемой страницы блока 6 памяти (КСЗ 1 - соответствует 1-й странице, ..., КС7 1 - соответствует 5-й странице) . После указанных предварительных установок программно разрешается работа нулевого используемого канала

КПДП 31 и инициируется захват КПДП 31- шин процессора установкой разряда КСО ППА 19, который по выходу 2.7 / блока 2 поступает на вход ЗПДО КПДП 31. Разряд КСО единичным значением разрешает также по входу сброса работу триггера 21 (фиг. 56, участок I).

15487908

(фиг. 5ж, участок II). Этот сигнал задерживается триггером 21 на один цикл обмена (фиг. 5э, участок III) и формирует на выходе элемента 24 сигнал загрузки счетчика 16 и на выходе элемента 25 сигнал инкремента счетчика 17 (фиг. 5и, участок III). Тем самый перед выдачей сигналов записи с КПДП 31

Получив ЗПДО, КПДП 31 выдает микро-10 на счетчиках 16, 17 устанавливается

30

Процессору запрос на сигнал ЗХ захвата шин (фиг. 5в, участок I), получив в ответ сигнал ПЗХ (фиг. 5 г, участок I), захватывает шины при условии уровня 1 на своем входе готовности (14м (фиг. 5а, участок 1)и начинает побайтный обмен. При этом выставляется сиг- |нал (ЗПТ) , который подключает выход РА 29 к старшим восьми разрядам шины 9, расширяя выдаваемый КПДП 31 рп мультиплексируемый адрес, по входу 2.1 разрешает формирование на элементах 26 и 27 сигналов выборки младшего и старшего байтов элементов, хранящихся в блоке 6 памяти. При этом сигнал 25 с выхода 2.3 управляет подключением соответствующего байта выхода блока 6 памяти к входу блока 3 через мультиплексор 4. Сигнал ЗПТ КПДП 31 подключает информационный вход-выход бло- |ка 3 к шине 8 данных, к шине 10 через |блок 15 16 младших адресов, формируе- мых блоком адресации, и пять старших адресов, формируемых на КСЗ,...,КС7 блока 2 управления. Направление передачи на выход с информационного входа- выхода блока 3 определяется установкой сигнала ЧтВВ с КПДП 31. Причем в случае записи фрагмента в блок 6 КПДП 31 выдает сигналы ЧтЗУ, ЗПВВ (фиг. 5е), в случае чтения фрагмента из блока 6 памяти - ЗпЗУ, ЧтВВ. По форме сигналы ЗПВВ, ЗПЗУ идентичны. Передача каждого байта подтверждается сигналом РПДО (фиг. 5д).

Расположение эчементов перемещаемого фрагмента в выбранной странице блока 6 памяти определяется по горизонтали старшими восемью разрядами 9-раэрядного СТХ 16, по вертикали - восемью разрядами СТУ 17 в блоке П. Выбор байта элемента определяется младшим разрядом СТХ 16 (AGO 0 - соответствует младшему байту элемента). Инкрементация счетчика 16 осуществляется по сигналу РПДО (фиг. 5д) . Учас- 5- ток адресации старшего байта конечного столбца фрагмента индицируется уровнем 1 на выходе компаратора 20

35

40

45

50

адрес начального элемента следующей строки. По окончании обмена КПДП 31 снимает сигнал захвата шин процессор и предоставляет их ему (фиг. Зв, г, участок V). Вход ГТ КПДП 31 используется для дополнительной его синхро низации с системной памятью процессо ра. При нулевом значении сигнала ГТ на входе КПДП 31 он блокирует переда чу элементов (фиг. 5, участок IV).

Таким образом, введение блоков ад ресации и формирования адреса дает возможность передачи прямоугольных фрагментов (не более 16 Кбайт) за од цикл подготовки КПДП 3, значительно повышает быстродействие устройства.

Формула изобретения

Запоминающее устройство с произвольной выборкой, содержащее блок па мяти, два мультиплексора, блок шинны формирователей и блок управления, ин формационный вход-выход блока шинных формирователей является информационным входом-выходом устройства, первы выход блока управления соединен с уп равляющим входом первого мультиплексора и входом выборки младшего байта блока памяти, второй выход блока управления соединен с входом выборки старшего байта блока памяти, выход первого мультиплексора соединен с ин формационным входом блока шинных фор мирователей, разряды младшего и стар шего байтов выхода блока памяти соед нены с первым и вторым информационны ми входами первого мультиплексора со ответственно, третий выход блока управления соединен с входом записи бл ка памяти, отличающееся тем, что, с целью повышения быстродей ствия, в него введены блок контроллер блок адресации и блок формирования ад реса, выход второго мультиплексора со единен с информационным входом блока памяти, выход блока шинных формирователей соединен с первым информационным входом второго мультиплексора, вы

на счетчиках 16, 17 устанавливается

0

п 5

-

5

0

5

0

адрес начального элемента следующей строки. По окончании обмена КПДП 31 снимает сигнал захвата шин процессора и предоставляет их ему (фиг. Зв, г, участок V). Вход ГТ КПДП 31 используется для дополнительной его синхронизации с системной памятью процессора. При нулевом значении сигнала ГТ на входе КПДП 31 он блокирует передачу элементов (фиг. 5, участок IV).

Таким образом, введение блоков адресации и формирования адреса дает возможность передачи прямоугольных фрагментов (не более 16 Кбайт) за один цикл подготовки КПДП 3, значительно повышает быстродействие устройства.

Формула изобретения

Запоминающее устройство с произвольной выборкой, содержащее блок памяти, два мультиплексора, блок шинных формирователей и блок управления, информационный вход-выход блока шинных формирователей является информационным входом-выходом устройства, первый выход блока управления соединен с управляющим входом первого мультиплексора и входом выборки младшего байта блока памяти, второй выход блока управления соединен с входом выборки старшего байта блока памяти, выход первого мультиплексора соединен с информационным входом блока шинных формирователей, разряды младшего и старшего байтов выхода блока памяти соединены с первым и вторым информационными входами первого мультиплексора соответственно, третий выход блока управления соединен с входом записи блока памяти, отличающееся тем, что, с целью повышения быстродействия, в него введены блок контроллера, блок адресации и блок формирования адреса, выход второго мультиплексора соединен с информационным входом блока памяти, выход блока шинных формирователей соединен с первым информационным входом второго мультиплексора, выходы блока формирования адреса соединены с адресными входами устройства и блока памяти, первый выход блока контроллера соединен с первым управляющим входом блока управления, управляющим входом второго мультиплексора -и входами выбора направления блока шинных формирователей и блока формирования адреса, второй выход блока контроллера соединен с вторым управляющим входом блока управления и входом приращения адреса блока адресации, четвертый выход блока управления соединен с входом запроса прямого доступа блока контроллера, адресный вход-выход блока контроллера соединен с адресным входом-выходом устройства, адресный вход блока управления соединен с младшими разрядами адресного входа-выхода устройства, информационные входы-выходы блока контроллера и блока управления соединены с информационным входом-выходом устройства, управляющие входы-выходы блока контроллера и блока управления соединены с управляющими входами-вы2.Б

5

0

5

ходами устройства, третий управляющий вход блока управления является входом записи двухбайтного слова устройства, пятый выход блока управления соединен с информационным входом блока адресации, шестой выход блока управления соединен с первым информационным входом блока формирования адреса, первый выход блока адресации соединен с информационным входом блока управления, старшие разряды первого выхода и второй выход блока адресации соединены с вторым и третьим информационными входами блока формирования адреса соответственно, второй информационный вход второго мультиплексора является информационным входом устройства, выход блока памяти является информационным выходом устройства, линия сигнала чтения устройств ввода-вывода управляющего входа-выхода устройства соединена с входом разрешения работы блока шинных формирователей, седьмой выход блока управления соединен с входом счета и установки блока адресации.

Фиг.1

м / k/ w i/ v

у I у I Ivy у V N }

vqtniwst -. It

Cx

,

I

.

Ш Ы

s

I

, 4

Q

c: f

OJ

-o

CO vC

о

е

ж

з

и

1

S

Фиг, 5

| Хвощ С.Т, и др | |||

| Микропроцессоры и микроЭВМ в системах автоматического управления | |||

| - Л.: Машиностроение, 1987, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Полупроводниковые запоминающие устройства и их применение./Под ред | |||

| А.Ю | |||

| Гордонова | |||

| - М.: Радио и связь, 1981, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Запоминающее устройство с произвольной выборкой | 1986 |

|

SU1345202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-07—Публикация

1988-06-28—Подача