Изобретение относится к вычислительной технике и может быть использовано для формирования псевдослучайных тестов в системах контроля и диагностики дискретньгх блоков.

Цель изобретения - увеличение полноты формируемого теста.

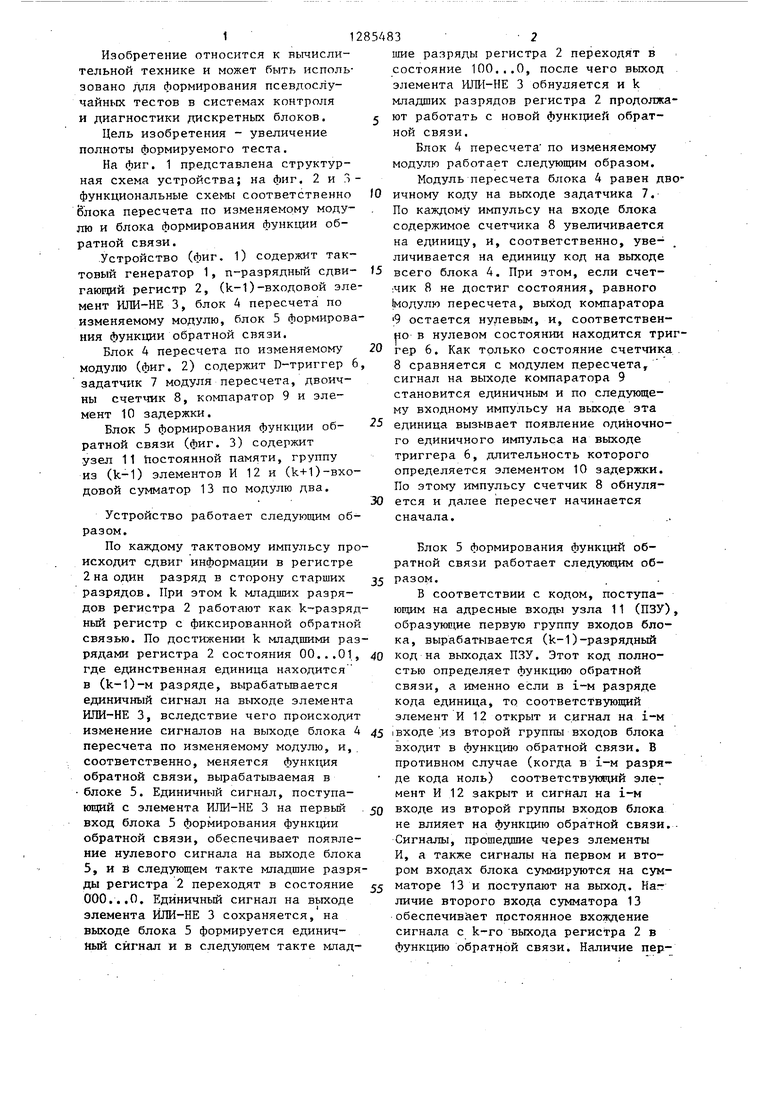

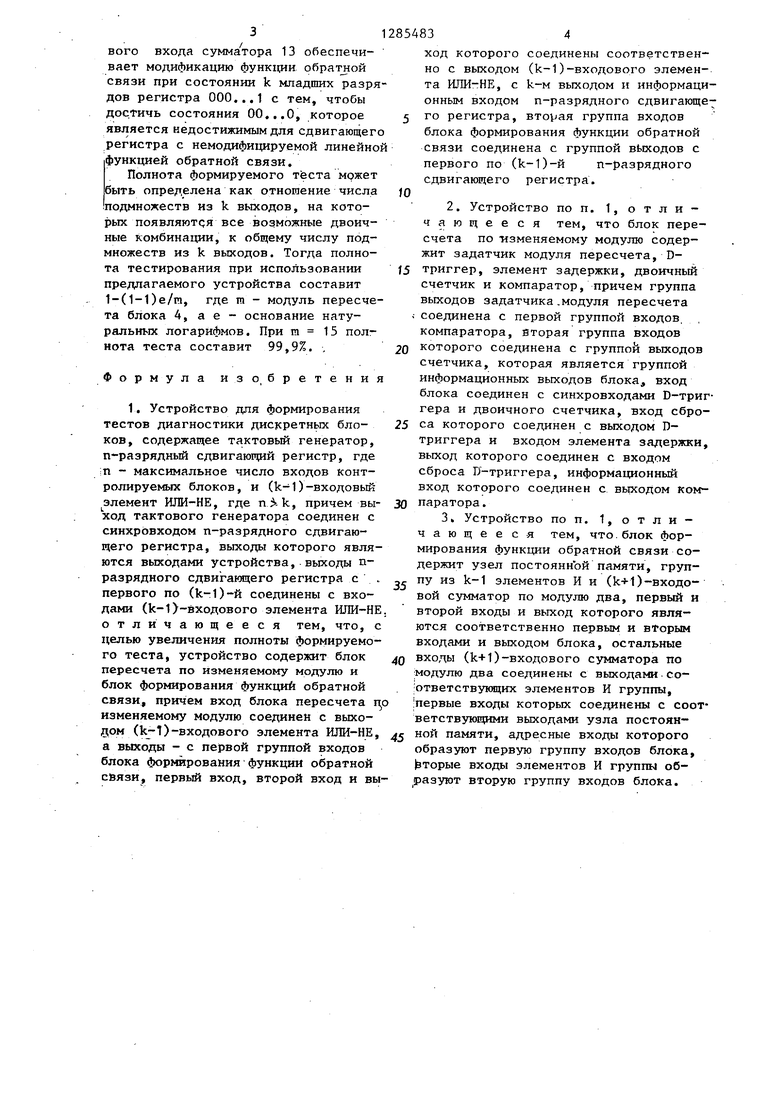

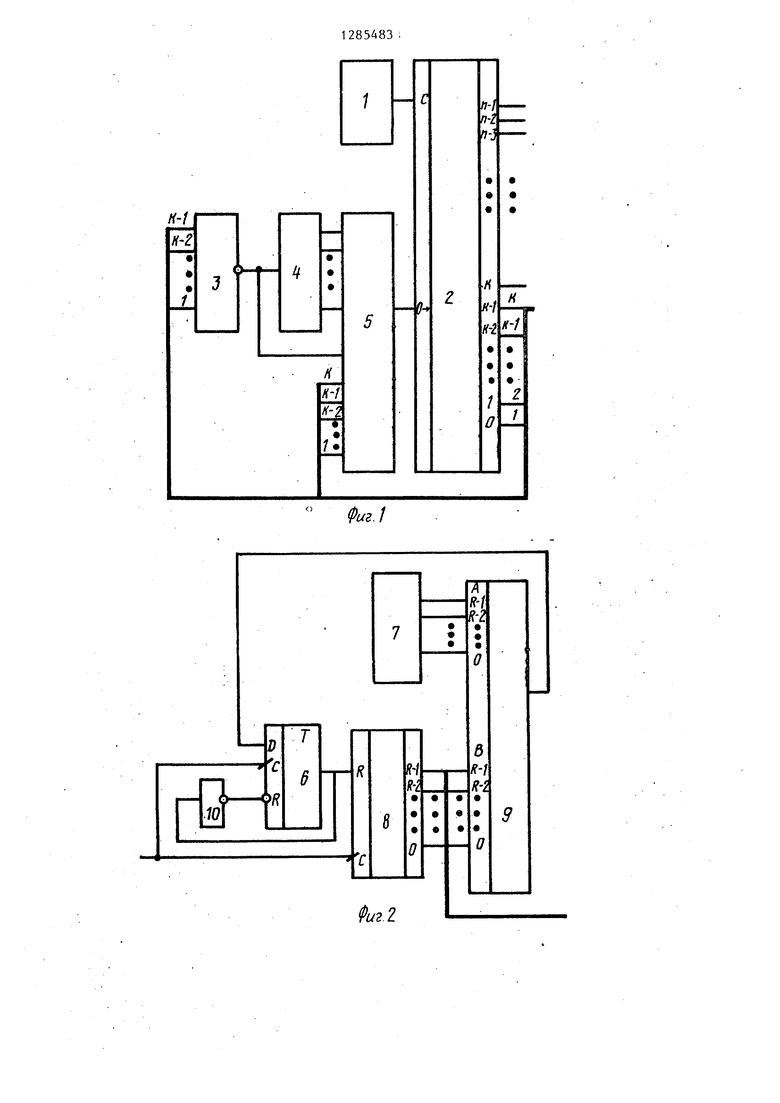

На фиг. 1 представлена структурная схема устройства; на фиг. 2 и 3 - функциональные схемы соответственно Влока пересчета по изменяемому моду- лю и блока формирования функции обратной связи.

Устройство (фиг. 1) содержит тактовый генератор 1, п-разрядный сдви- гающий регистр 2, (К-1)-входовой элемент ИЛИ-НЕ 3, блок А пересчета по изменяемому модулю, блок 5 формирования функции обратной связи.

Блок 4 пересчета по изменяемому модулю (фиг. 2) содержит D-триггер 6 задатчик 7 модуля пересчета, двоичны счетчик 8, компаратор 9 и зле- мент 10 задержки.

Блок 5 формирования функции об- ратной связи (фиг. 3) содержит узел 11 Постоянной памяти, группу из (k-1) элементов И 12 и (k+1)-BXO- довой сумматор 13 по модулю два.

Устройство работает следующим образом.

По каждому тактовому импульсу происходит сдвиг информации в регистре 2 на один разряд в сторону старших разрядов. При этом k младших разрядов регистра 2 работают как k-разряд ный регистр с фиксированной обратной связью. По достижении k младшими разрядами регистра 2 состояния 00...01, где единственная единица находится в (k-l)-M разряде, вырабатьтается единичный сигнал на выходе элемента ИЛИ-НЕ 3, вследствие чего происходит изменение сигналов на выходе блока 4 пересчета по изменяемому модулю, и,. соответственно, меняется функция обратной связи, вырабатываемая в блоке 5. Единичный сигнал, поступающий с элемента ИЛИ-НЕ 3 на первый вход блока 5 формирования функпряи обратной связи, обеспечивает появление нулевого сигнала на выходе блока 5, и в следующем такте младшие разряды регистра 2 переходят в состояние 000...О. Единичньш сигнал на выходе элемента ЙЛИ-НЕ 3 сохраняется, на выходе блока 5 формируется единичный сигнал и в следующем такте младшие разряды регистра 2 переходят в состояние 100...О, после чего выход элемента ИЛИ-НЕ 3 обнуляется и k младших разрядов регистра 2 продолжают работать с новой функцией обратной связи.

Блок 4 пересчета по изменяемому модулю работает следующим образом.

Модуль пересчета блока 4 равен двичному коду на выходе задатчика 7. По каждому импульсу на входе блока содержимое счетчика 8 увеличивается на единицу, и, соответственно, увеличивается на единицу код на выходе всего блока 4. При этом, если счетчик 8 не достиг состояния, равного (модулю пересчета, выход компаратора 9 остается нулевым, и, соответственно в нулевом состоянии находится тригер 6. Как только состояние счетчика 8 сравняется с модулем пересчета, сигнал на выходе компаратора 9 становится единичным и по следующему входному импульсу на выходе эта единица вызывает появление одиночного единичного импульса на выходе триггера 6, длительность которого определяется элементом 10 задерзкки. По этому импульсу счетчик 8 обнуляется и далее пересчет начинается сначала.

Блок 5 формирования функций обратной связи работает следующим образом.

В соответствии с кодом, поступающим на адресные входы узла 11 (ПЗУ) образукнцие первую группу входов блока, вырабатывается (k-1)-разрядный код на выходах ПЗУ. Этот код полностью определяет функцию обратной связи, а именно если в i-м разряде кода единица то соответствующий элемент И 12 открыт и сигнал на i-м I входе из второй группы входов блока входит в функцию обратной связи. В противном случае (когда в i-м разряде кода ноль) соответствукящй элву мент И 12 закрыт и сигнал на i-м входе из второй группы входов блока не влияет на функцию обратной связи, Сигналы, прошедшие через элементы И, а также сигналы на первом и втором входах блока суммируются на сумматоре 13 и поступают на выход. Наличие второго входа сумматора 13 обеспечивает постоянное вхождение сигнала с k-ro выхода регистра 2 в функцию обратной связи. Наличие пер31

вого входа сумматора 13 обеспечивает модификацию функции обрат юй связи при состоянии k младших разрядов регистра 000...1 с тем, чтобы достичь состояния 00...О, которое является недостижимым для сдвигающего регистра с немодифицируемой линейной функцией обратной связи.

Полнота формируемого теста может быть определена как отношение числа

подмножеств из k выходов, на которых появляются все возможные двоичные комбинации, к общему числу подмножеств из k вьпсодов. Тогда полнота тестирования при использовании предлагаемого устройства составит 1-(1-1)е/та, где m - модуль пересчета блока 4, а е - основание натуральных логарифмов. При та 15 полнота теста составит 99,9%. ,

Формула изобретения

1. Устройство для формирования тестов диагностики дискретньк блоков, содержащее тактовый генератор, п -разрядньй сдвигающий регистр, где ;п - максимальное число входов контролируемых блоков, и (k-1)-входовый элемент ИЛИ-НЕ, где пЗ-k, причем вы- ход тактового генератора соединен с синхровходом п-разрядного сдвигающего регистра, выходы которого являются выходами устройства, выходы п- разрядного сдвигающего регистра с . первого по (k-1)-и соединены с входами (k-1)-вxoдoвoгo элемента ИЛИ-НЕ отличающееся тем, что, с целью увеличения полноты формируемого теста, устройство содержит блок пересчета по изменяемому модулю и блок формирования функ1Д1Й обратной связи, причем вход блока пересчета г изменяемому модулю соединен с выхо

дом (и-1)-входового элемента ИЛИ-НЕ, ной памяти, адресные входы которого а выходы - с первой группой входов образуют первую группу входов блока, блока формирования функции обратной связи, первый вход, второй вход и вы торые входы элементов И группы об- разуют вторую группу входов блока.

0

5

0

5

0

ход которого соединены соответственно с выходом (k-1)-входового элемента ИЛИ-НЕ, с k-M выходом и информационным входом п-разрядного сдвигающе-;- го регистра, вторая группа входов блока формирования функции обратной связи соединена с группой вЬкодов с первого по (k-1)-и п-разрядного сдвигающего регистра.

2. Устройство по п. 1, отличающееся тем, что блок пересчета по -изменяемому модулю содержит задатчик модуля пересчета, D- триггер, элемент задержки, двоичный счетчик и компаратор, причем группа выходов задатчика.модуля пересчета соединена с первой группой входов, компаратора, вторая группа входов которого соединена с группой выходов счетчика, которая является группой информационных выходов блока, вход блока соединен с синхровходами D-триг- гера и двоичного счетчика, вход сброса которого соединен с выходом D- триггера и входом элемента задержки, выход которого соединен с входом сброса П-триггера, информационный вход которого соединен с вьрсодом компаратора.

3. Устройство по п. 1, отличающее с я тем, что.блок формирования функции обратной связи содержит узел постоянной памяти, груп- г пу из k-1 элементов И и ()-вxoдo- вой сумматор по модулю два, первый и второй входы и выход которого являются соответственно первьм и вторым входами и выходом блока, остальные входы (k+1)-вxoдoвoгo сумматора по модулю два соединены с выходамисо- ответствующих элементов И группы, первые входы которых соединены с соответствующими выходами узла постоян0

ной памяти, адресные входы которого образуют первую группу входов блока,

торые входы элементов И группы об- разуют вторую группу входов блока.

f( к-

К-2

Н

f{

//

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство для умножения чисел по модулю | 2017 |

|

RU2653263C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 2018 |

|

RU2696223C1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Вероятностное суммирующее устройство | 1975 |

|

SU737948A1 |

| Декодирующее устройство | 1990 |

|

SU1783626A1 |

Изобретение относится к вычислительной технике и может быть не- . пользовано для формирования псевдослучайных тестов в системах контроля и диагностики дискретных блоков. Целью изобретения является убеличе- ние полноты формируемого теста путем повьшения полноты покрытия k подмно:жеств входов п-входовой контролируемой схемы тривиальными тестами. Уст-. ройство содержит тактовый генератор, п-разрядный сдвигающий регистр, i (k-1)-входовый элемент ИШ-НЕ, блок пересчета по изменяемому модулю, блок формирования функции обратной связи. Блок пересчета по изменяемому модулю содержит D-триггер, задатчик модуля пересчета, двоичный счетчик, компаратор и элемент задержки. Блок формирования функции обратной связи содержит узел постоянной памяти, группу из (k-1) элементов И и (k+1)- входовый сумматор по модулю два,За счет того, что.в процессе формирования псевдослучайных тестов в устройстве осуществляется изменение связей входов сумматора по модулю два с выходами сдвигающего регистра, обеспечивается повышенная полнота формируемого теста, которая определяется как отношение числа подмножеств из k выходов, на которых появляются все возможные двоичные .комбинации, к общему числу подмножеств из k выходов. 2 з.п. ф-лы, 3 ил. с s (/) С

О

Редактор Е. Папп

Составитель с.jTap4HXHHt

Техред А.Кравчук Корректор И. Муска

Заказ 7526/51 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля логических блоков | 1979 |

|

SU792256A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| IEEE Transaction on computers, V | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Ускоритель для воздушных тормозов при экстренном торможении | 1921 |

|

SU190A1 |

Авторы

Даты

1987-01-23—Публикация

1985-06-28—Подача