1 - 12 Изобретение относится к вычислительной технике и может быть использовано для построения многопороговых запоминающих устройств.

Цель изобретения - увеличение по- лезной информационной емкости устрой- ства.

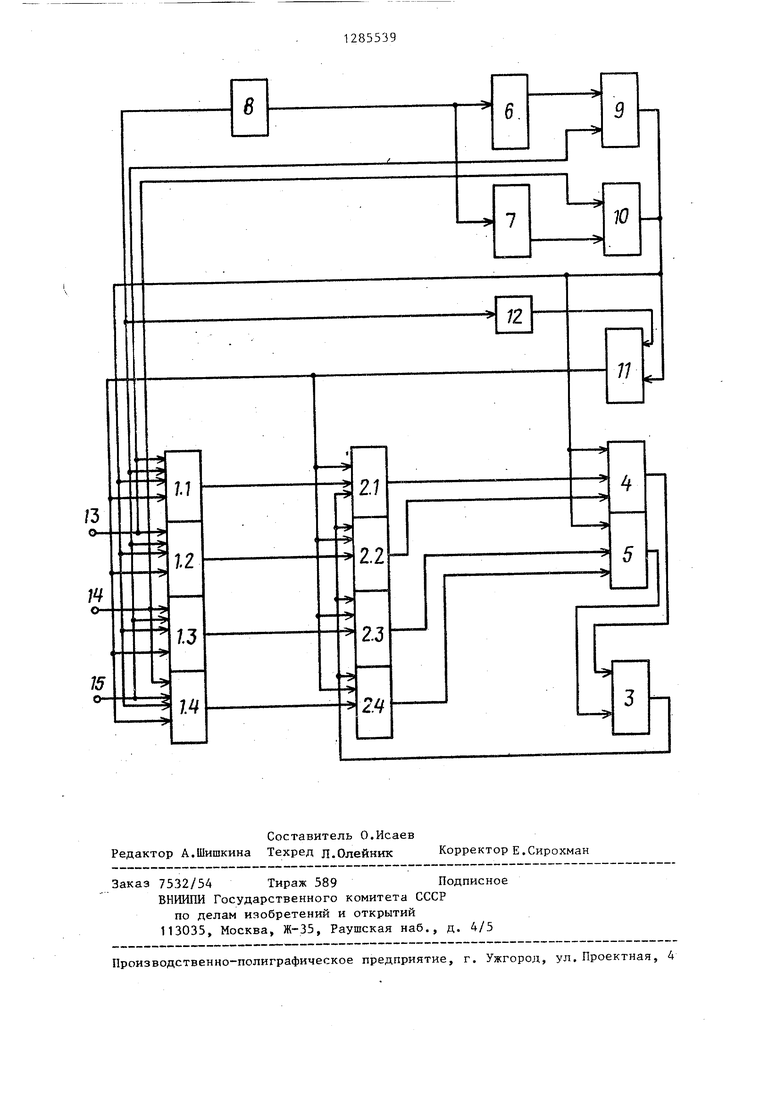

На чертеже приведена схема запоминающего устройства.

Устройство содержит адресные коммутаторы 1.1-1.4, блоки 2.1-2.4 памяти, сумматор 3, первый 4 и второй 5 коммутаторы операндов, регистр 6 первого и регистр 7 второго дескрипторов, первый дешифратор 8, первый 9 и второй 10 коммутаторы дескрипторов, второй дешифратор 11, триггер 12 управления записью, адресные входы чтения 13 и 14 и записи 15 устройства. Регистр 6 служит для хранения первого дескриптора (Д1), регистр 7 - для хранения второго дескриптора (Д2). Триггер управления записью (ТУ) со счетным входом - в каждом такте записи значение сигнала на его выходе изменяется на противоположное. Дескрипторы Д1 и Д2 имеют следующий смь1сл (для каждого адреса ЗУ дескрипторы указывают): О - информация находится в блоке 2.1; Д1 1 информация находится в блоке 2.2; Д2 О - информация находится в блоке 2.3; 1 - информация находится в блоке 2.4.

Дешифратор 11 формирует сигналы, управляющие записью по правилу, пред ставленному в таблице.

5

5

0

5

5

5

0

5

392

Устройство работает следующим образом.

В каждом такте по входам 13-15 одновременно выдаются два адреса чтения и адрес записи. По адресам чтения производится выборка двух дескрипторов Д1 и Д2 на выходах коммутаторов 9 и 10, определяющих размещение информации в запоминающих блоках. Эти дескрипторы воздействуют на управляющие входы коммутаторов 1.1-1.4, где обеспечивают передачу адресов чтения на соответствующие з-апоминаю- щие блоки, и на управляюпще входы коммутаторов 4 и 5, где обеспечивают наличие считанной по первому адресу информации на выходе коммутатора 4, а информации, считанной по второму адресу - на выходе коммутатора 5. Одновременно значение дескрипторов Д1, Д2 и сигнал с выхода-триггера управления записью поступают на вход дешифратора 11. Управляющий сигнал с выхода дешифратора 11 поступает на управляющие входы коммутаторов 1.1-1.4, где определяет на какой из запоминающих блоков передается адрес записи и на управляющие входы запоминающих блоков, где определяет на. какой блок должна быть принята записываемая информация. Очевидно, что структура устройства исключает конфликтные обращения к блокам 2.1-2.4 памяти. Результаты предьщущей операции записываются только в один из запоминающих блоков, не занятых чтением.

Пример . Пусть первому адресу чтения соответствует дескриптор Д1 10, второму Д2 1. Полагаем, что в данном такте сигнал на выходе триггера управления записью ТУ О, Дескрипторы указывают, что первый операнд находится в блоке 2.1, а второй - в блоке 2.4, На выходе дешифратора 11 формируется управляющий сигнал, определяющий, что запись должна быть произведена в запоминающий блок 2,2. Де скриптор Д1 обеспечивает прохождение первого адреса чтения через коммутатор 1,1 на блок 2.1, а информации, считанной по данному адресу в блоке 2.1, через коммутатор 4 на первый вход сумматора. Дескриптор Д2 обеспечивает прохождение второго адреса чтения через коммутатор 1.4 на блок 2,4, а информации, считанной по этому адресу в блоке 2.4, чеJ12

грез коммутатор 5 на второй вход сум- |матора. Одновременно с этим управляющий сигнал с. выхода дешифратора 11 обеспечивает прохождение адреса записи через коммутатор 1.2 на блок 2,2 и прием результата предыдущей операции с выхода сумматора на запоминающий блок 2.2 для записи.

В следующем такте состояние дескрипторов может остаться без измене- ния, но обязательно изменяется значение сигнала на выходе триггера управления записью. В этом случае новые адреса чтения принимаются: первьй - в блок 2.1, второй - в блок 2.4. Oneранды, считанные по новым адресам, через коммутаторы 4 и 5 передаются на входы сумматора. Поскольку состояние триггера управления изменилось:

ТУ 1, то адрес записи результата операции, выполненной в предыдущем такте, принимается в запоминающий блок 2.3.

Таким образом в каждом такте обес-„ входами первого дешифратора, выходы

печивается одновременное обращение по. трем адресам: первому и второму адресам чтения и адресу записи. В каждом такте запись результатов пре- дьщущей операций происходит лишь в один из незанятых чтением запоминающих блоков.

Формула изобретения

I

Запоминающее устройство, содержащее блоки памяти, адресные входы которых подключены к выходам соответствующих адресных коммутаторов, информационные входы соединены с бы30

35

.40

которого подключены к входам регистров дескрипторов, о тличающе- е с я тем, что, с целью увеличения полезной информационной емкости устройства, в него введены триггер уп- рабйения записью и второй дешифратор причем счетный вход триггера управления записью подключен к одному из адресных входов записи устройства, а выход соединен с первым входом второго дешифратора, второй и третий входы которого подключены к выходам коммутаторов первого и второго дес- крипторов, а выходы соединены с входами записи и другими управляющими входами соответствукнцих блоков памяти и адресных коммутаторов.

ходами сумматора, входы которого под ключены к выходам первого и второго

5

0

коммутаторов операндов, информационные входы которых соединены с выходами соответствующих блоков памяти, а управляющие входы подключены к одним управляющим входам адресных коммутаторов и выходам коммутаторов первого и второго дескрипторов, входы первой группы которых соединены с выходами соответствующих регистров дескрипторов, входы второй группы коммутатора первого дескриптора соединены с информационными входами первой группы одних адресных коммутаторов и являются одними адресными входами чтения устройства, входы вторсй, группы коммутатора второго дескриптора подключены к информационным входам первой группы других адресных коммутаторов и являются другими адресными входами чтения устройства, информационные входы второй группы адресных коммутаторов являются адресными входами записи устройства и соединены с

30

35

40

которого подключены к входам регистров дескрипторов, о тличающе- е с я тем, что, с целью увеличения полезной информационной емкости устройства, в него введены триггер уп- рабйения записью и второй дешифратор, причем счетный вход триггера управления записью подключен к одному из адресных входов записи устройства, а выход соединен с первым входом второго дешифратора, второй и третий входы которого подключены к выходам коммутаторов первого и второго дес- крипторов, а выходы соединены с входами записи и другими управляющими входами соответствукнцих блоков памяти и адресных коммутаторов.

Составитель О.Исаев Редактор А.Шишкина Техред Л.Олейник Корректор Е.Сирохман

....« «и ,. .,..-. ..- «.....«, .«.., и..« ,..,„. ,., ,,,,

Заказ 7532/54 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Запоминающее устройство | 1985 |

|

SU1317479A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Резервированное запоминающее устройство | 1989 |

|

SU1751819A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения многопороговых запоминающих устройств. Целью изобретения является увеличение полезной информационной емкости устройства. Устройство содержит блоки памяти, адресные коммутаторы, сумматор, коммутаторы операндов, коммутаторы и регистры дескрипторов, первый я второй дешифраторы, триггер управления записью. Б каждом такте работы устройства обеспечивается одновременное бесконфликтное обращение по трем адресам: первому и второму адресам чтения и адресу записи. В каждом такте запись результатов предыдущей операции происходит лишь в один-из незанятых чтением блоков памяти. 1 табл. 1 ил. (Л tsD 00 сл ел со со

| Мультипроцессорные системы и параллельные вычисления | |||

| Под ред | |||

| Ф.Энслоу.-М.: Мир, 1976, с | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-04-03—Подача