112855902

Изобретение относится к автомати- Входы ячеек первого столбца 1-i

ке и вычислительной технике и может.j , 2,. . ., -I) соединены с вход- быть использовано для построения раз-

личных устройств переработки диск-ными информационными шинами 2. Входы

ретной информации.5ячейки 2-1 соединены с входной инМногопороговый логический элементформационной шиной 2 и выходом элеменреализован на основе пар элементов Ита ИЛИ ячейки 1-1. Входы ячейки

и ИЛИ, расположенных в виде прямо- 2 соединены с входной информаци- угольной матриц з1. Варианты отличают-

ся организацией связей в зависимое- О онной шиной 2 и выходом элемента И ти от соотношений числа входов поро- . ,(2 i). входы ячейки К-1

РОВ .

Цель изобретения - повьш1ение быс- (К 4,6,...,п) соединены с выходом тродействия многопорогового элемента. элемента ИЛИ ячейки (К-2)-1 и выхо- На фиг. 1 и 2 приведены схемы пред- дом элемента ИЧИ ячейки (К-1)-1, вхолагаемого порогового элемента для к- соединены с выходом

п 8; на фиг. 3 и 4 - то же, для

п 7. элемента И ячейки (К-1) - (т - 1) и

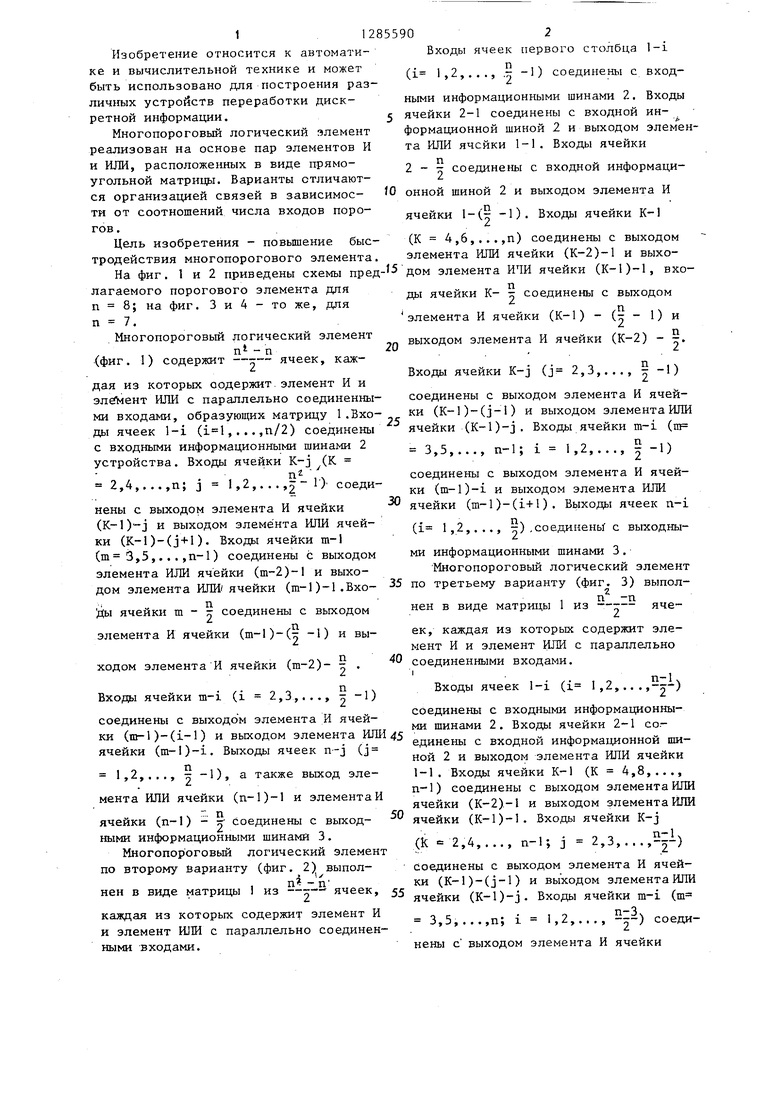

Многопороговый логический элемент выходом элемента И ячейки (К-2) - . ,. п -

(фиг. 1) содержит ячеек, кажВходы ячейки K-j (j 2,3,..., - -1) дая из которых содержит.элемент И и

ИЛИ с параллельно соединенны-соединены с выходом элемента И ячей- ми входами, образующих матрицу 1.Вхо-ки (K-l)-(j-l) и выходом элементаИЛИ ды ячеек 1-i (,...,п/2) соединеныячейки (К-1)-j. Входы ячейки m-i (ш с входными информационными шинами --1) устройства. Входы ячейки K-j(К 2 . , „ 1 соединены с выходом элемента И ячей- 2,4,...,п; J - 1,2,...,|-1 соеди- (m-l)-i и выходом элементаИЛИ

иены с выходом элемента И ячейки ячейки (т-1)-(+). Выходы ячеек n-i

(K-l)j и выходом элемента Ш1И ячей-(i 1,2,..., ).соединены с выходныки (K-l)-(j+l). Входы ячейки т-1

(т 3,5,...,п-1) соединены с выходомми информационными шинами 3.

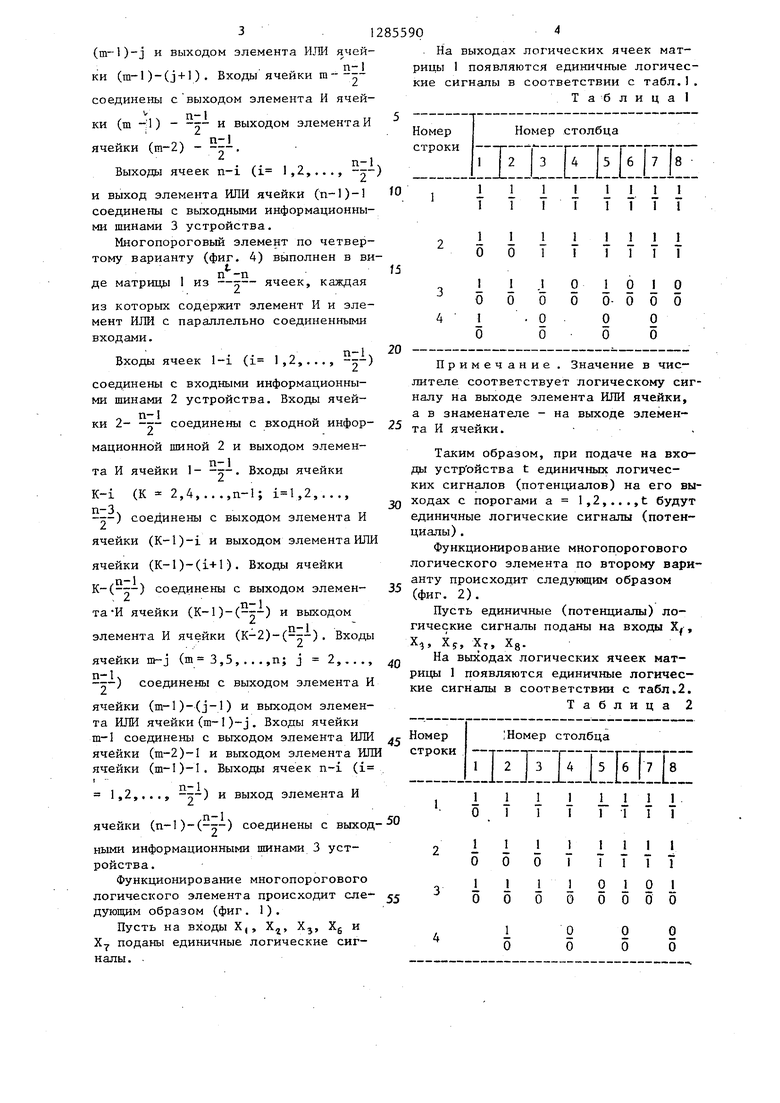

элемента ИЛИ ячейки (т-2)-1 и выхо-Многопороговый логический элемент

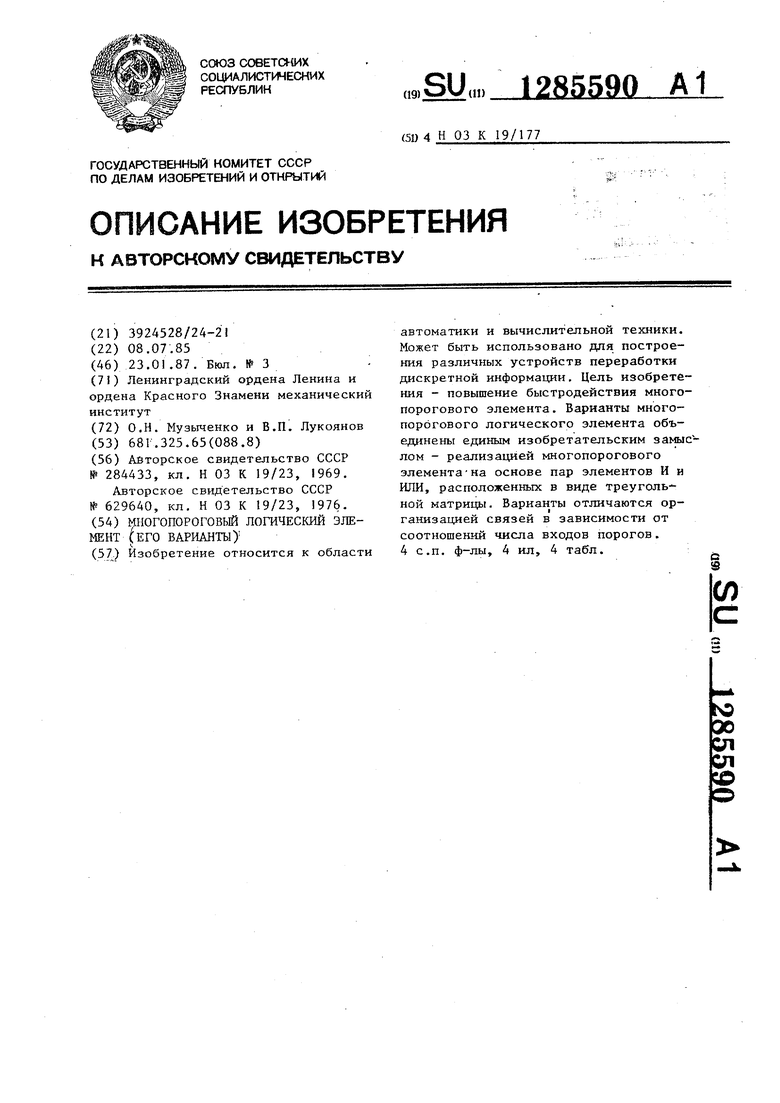

дом элемента ИЛИ ячейки (m-l)-l.Bxo- 5 по третьему варианту (фиг 3) выполды ячейки m - I соединены с выходом «ен в виде матрицы 1 из ----- ячеэлемента И ячейки (т-1)-(| -1) и вы- к, каждая из которых содержит элемент И и элемент ИЛИ с параллельно ходом элемента-И ячейки (т-2)- | . соединенными входами.

./от п ,, Входы ячеек 1-i (i I,2,...,-г-) Входы ячейки m-i (i 2,3,. .., -1) 2

„ „соединены с входными информационны- соединены с выходом элемента И ячеи-от, oi

.,,,.,,„„„ми шинами 2. Входы ячейки 2-1 соки (m-l)-(i-l) и выходом элемента ИЛИ 45- ,

,.,... ,. единены с входной инфopмau oннoи шиячеики (m-I)-i. Выходы ячеек n-j ( -.

НОИ 2 и выходом элемента ИЛИ ячейки

1,2,..., -1), а также выход эле- 1-1. Входы ячейки (К 4,8,...,

„„„ „ / , ,„ п-1) соединены с выходом элементаИЛИ

мента ИЛИ ячейки (n-l)-l и элемента И „ ,:Т „, ,„„,

ячейки (К-2).-1 и выходом элементаИЛИ

ячейки (п-1) - соединены с выход- ячейки (К-1)-1. Входы ячейки K-j

ными информационными шинами 3. о / i то п-К у (,4,...,n-l;i 2,3,..., -:г-)

Многопороговьш логический элемент

по второму варианту (фиг. 2) выпол- соединены с выходом элемента И ячей, ки (K-l)-(i-l) и выходом элементаИЛИ нен в виде матрицы 1 из --:-- ячеек, 55 - /т/- i -г, - /

2 - - ячейки (K-l)-j. Входы ячейки m-i (m

каждая из которых содержит элемент И „ .. . , „ п-Зч

rimi 3,5,...,,2,..., ---) соедии элемент ШШ с параллельно соединен- .2

ными входами.нены с выходом элемента И ячейки

(m-l)-j и выходом элемента ИЛИ ячейки (m-l)-(j + l). Входы ячейки m----- соединены с выходом элемента И ячейки (т Hi) - и выходом элемента И

, „ч п-1 ячейки (т-/; -

it «

Выходы ячеек n-i (i 1,2,..,, 2

и выход элемента ИЛИ ячейки (п-1)- соедине ш с выходными информационными шинами 3 устройства.

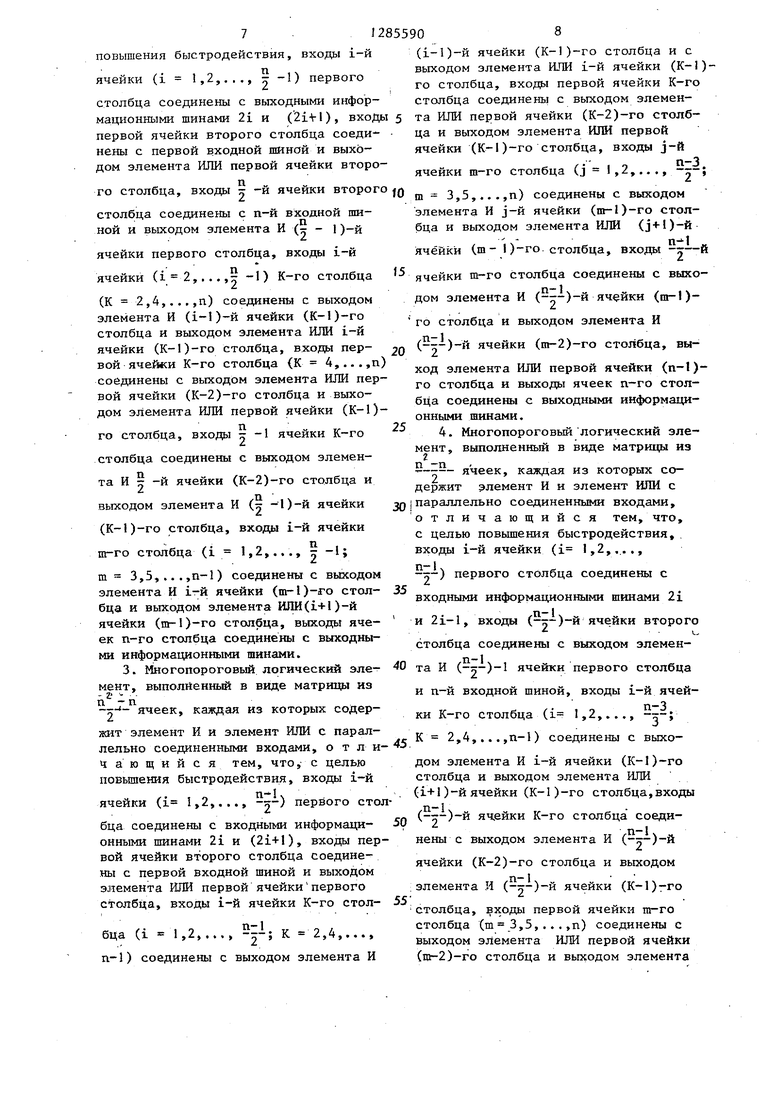

Многопороговый элемент по четвертому варианту (фиг. 4) выполнен в виде матрицы I из

п -.п

ячеек, каждая

из которых содержит элемент И и элемент ИЛИ с параллельно соединенными входами.

Входы ячеек 1-i (i 1,2,..., )

соединены с входными информационными шинами 2 устройства. Входы ячей- п-1

20

ки 22 соединены с входной инфор- 25 та И ячейки.

мационной шиной 2 и выходом элемен- п-1

Примечание . Значение в числителе соответствует логическому сиг налу на выходе элемента ИЛИ ячейки, а в знаменателе - на выходе элемента И ячейки 1- ячейки

K-i (К - 2,4,...,п-1; ,2,...,

п-З. .TI

---) соединены с выходом элемента И

ячейки (K-l)-i и выходом элемента ИЛИ

ячейки (K-l)-(i+l). Входы ячейки .п-1

Таким образом, при подаче на входы устройства t единичных логических сигналов (потенциалов) на его вы 30 ходах с порогами а l,2,...,t будут единичные логические сигналы (потенциалы) .

Функционирование многопорогового логического элемента по второму вари-. ,ч I..... анту происходит следуняцим образом

К-(-Г-) соединены с выходом элемен- 35 /, о 21,фиг. L) ,

та-И ячейки (К-)-(---) и выходом Пусть единичные (потенциалы) логические сигналы поданы на входы Х,

.п-1

элемента И ячейки (К--2)-(---) . Входы ячейки m-j (,5,...,n; j 2,,.., соединены с выходом элемента И

1

7

Хс

) 2

40

На выходах логических ячеек матрицы 1 появляются единичные логические сигналы в соответствии с табл.2.

ячейки (m-l)-(j-l) и выходом элемента ИЛИ ячейки (т-1 )-j . Входы ячейки т-1 соединены с выходом элемента ИЛИ ячейки (m-2)-I и выходом элемента ИЛИ ячейки (m-l)-I. Выходы ячеек n-i (i

1,2,..., ) и выход элемента И

ячейки (п-1)-() соединены с выходными информационными шинами 3 устройства.

Функционирование многопорогового логического элемента происходит еле- образом (фиг. 1).

Пусть на входы X,, Х, Х,, Xg и Х поданы единичные логические сигналы. .

2855904

На выходах логических ячеек матрицы 1 появляются единичные логические сигналы в соответствии с табл.1 .

Т а б л и ц а 1

та И ячейки.

Примечание . Значение в числителе соответствует логическому сигналу на выходе элемента ИЛИ ячейки, а в знаменателе - на выходе элеменТаким образом, при подаче на входы устройства t единичных логических сигналов (потенциалов) на его вы- ходах с порогами а l,2,...,t будут единичные логические сигналы (потенциалы) .

Функционирование многопорогового логического элемента по второму вари 1

7

Хс

омер строки

На выходах логических ячеек матрицы 1 появляются единичные логические сигналы в соответствии с табл.2.

Таблица 2

, Номер столбца

П-ТЕИ ШЗЕЕ

5Ч

Таким образом, при подаче на входы устройства t единичных логических сигналов на его выходах с порогами а l,2,,..,t будут единичные (потенциалы) логические сигналы.

Функционирование многопорогового логического элемента по третьему варианту происходит следующим образом, (фиг. 3).

Пусть единичные логические сигна лы поданы на входы X,, Х, Х, Х,

XT.

На выходах логических ячеек матрицы 1 появляются единичные логические сигналы в соответствии с табл. 3.

Таблиц аЗ

Номерстроки

Номер столбца

ШИШ

j о

1 1

т Т

Таким образом, при подаче на вхо- ды устройства t единичных логических сигналов на его выходах с порогами а l,2,...,t будут единичные логические сигналы.

Функционирование многопорогового логического элемента по четвертому варианту происходит следующим образом (фиг. 4).

Пусть на входы Х, Х, Х поданы единичные логические сигналы.

На выходах логических ячеек матрицы 1 появляются единичные логические сигналы в соответствии с табл.4.

Таблица4

i i 1 I 1 О .0 Г О 1 Т Т

5590 6

Таким образом, при подаче на входы устройства t единичных логических сигналов на его выходах с порогами а l,2,...,t будут единичные логи- 5 ческие сигналы.

Следовательно, предлагаемый многопороговый логический элемент обладает более регулярной структурой и большим быстродействием.

Ш

Формула изобретения

1. Многопороговый логический элемент, выполненный в виде матрицы из

t5 п -п

-J- ячеек, каждая из которых содержит элемент И и элемент ИЛИ с параллельно соединенными входами, о т л и- чающийся тем, что, с целью повътения быстродействия, входы i-й

20

Пч

чейки (i 1,2,..., ) первого столбца соединены с входными информационными шинами () и 21, входы j-й чейки К-го столбца (К 2,4,...,п;

j 1,2,..,, соединены с выхоом элемента И j-й ячейки (K-l)-ro столбца и выходом элемента ИЛИ (j+1)- ячейки (K-l)-ro столбца, входы i-й

ячейки (1 2,..., -1) т-го столбца)

m 3,5,..., п-1 (соединены с выходом элемента И (1-1)-й ячейки/iir-l)-ro

столбца и выходом элемента ИЛИ i-й ячейки (m-l)-ro столбца, входы первой ячейки ш-го столбца соединены с выходом элемента ИЛИ первой ячейки (т-2)- го столбца и выходом элемента ИЛИ

первой ячейки (m-l)-ro столбца, входы

п „ „

-и ячейки пг-го столбца соединены с

выходом элемента И й ячейки(т-2)го столбца и выходом элемента И -

( -1)-й ячейки (m-l)-ro столбца, выходы ячеек п-го столбца, а выход элемента ИЛИ первой ячейки (п-1)- го столбца и выход элемента И -й ячейки (п-1)-го столбца соединены с выходными информационными шинами.

2. Многопороговый логический элемент, выполненный в виде матрицы из

п -п

-2- ячеек, каждая из которых содержит элемент И и элемент ИЛИ с параллельно соединенными входами, о т л и- чающийся тем, что, с целью

7J2855908

повышения быстродействия, входы i-й (1-1)-й ячейки (K-l)-ro столбца и с

п ,чвыходом элемента ИЛИ i-й ячейки (К-1)ячейки (х 1,2,,.., :г -1) первого „ „ „

2; го столбца, входа первой ячейки К-го

столбца соединены с выходными инфор-столбца соединень с выходом элемен- мационными шинами 21 и (2i-Vl), входы 5та ИЛИ первой ячейки (К-2)-го столб- первой ячейки второго столбца соеди- ца и выходом элемента ИЛИ первой нены с первой входной шиной и выхо-ячейки (К-I)-го столбца, входы j-й дом элемента ИЛИ первой ячейки второ- „ столбца (j 1,2,.... го столбца, входы | -и ячейки второго ,о 3,5,...,п) соединены с выходом столбца соединены с входной ши-элемента И j-й ячейки (т-1)г о стопной и выходом элемента И (2 - i )йбца и выходом элемента ИЛИ (j+0-й

ячейки первого столбца, входы i-й ячейки (т - I)-го столбца, входы -г--и ячейки (i 2,...,- -1) К-го столбца ячейки т-го столбца соединены с выхо- (К 2,4,...,п) соединены с выходом дом элемента И (---)-и ячейки (т-1)элемента И (i-1 )-й ячейки (K-l)-ro . столбца и вьпсодом элемента И

столбца и выходом элемента ИЛИ i-и.

ячейки (K-l)-ro столбца, входы пер- 20 (2 ячейки (т-2)-го столбца, вы- вой ячейки К-го столбца (К 4,...,п) элемента ИЛИ первой ячейки (п-1)- соединены с выходом элемента ИЛИ пер- столбца и выходы ячеек п-го стол- вой ячейки (К-2)-го столбцами выхо- соединены с выходными информаци- дом элемента ИЛИ первой ячейки (К-1)-„нными шинами.

го столбца, входа -1 ячейки К-го 5 Многопороговый логический элемент, выполненный в виде матрицы из столбца соединены с выходом элемен- г

„ п „ „ /т/- 1 -о-- ячеек, каждая из которых со- та И :г -и ячейки (К-2)-го столбца и 2,,«mi

2держит элемент И и элемент ИЛИ с

выходом элемента И ( -1)-й ячейки jпараллельно соединеннь№ш входами,

,,, ..„ „отличающийся тем, что,

(К-П-го столбца, входы i-и ячейки,„

с целью повышения быстродействия,.

т-го столбца (i 1,2,..., 5 входы i-й ячейки (i 1,2,...,

I

m 3,5,...,п-1) соединены с выходом j) первого столбца соединены с

элемента И i-й ячейки (m-l)-го стол- 35,.

..„„/. .V „ входными информационными шинами 2i бца и выходом элемента ИЛИ(1+1)-й

ячейки (m-l)-ro столбца, выходы яче- и 2i-l, входы )-и ячейки второго

ек п-го столбца соединены с выходны- ,- .столбца соединены с выходом элеменми информационными шинами..

3. Многопороговый логический эле- та И ()-1 ячейки первого столбца

мент, выполненный в виде матришл из - „ „ . „ - -г --f V JJ входной шиной, входы 1-й ячей.JJ

-- ячеек, каждая из которых соДер- у. столбца (i 1,2,...,

жит элемент И и элемент ИЛИ с парал- ... о / ,4

АС К. - -ijA, ... ,п-1) соединены с выхо- лельно соединенными входами, о т л. к- чающийся тем, что, с целью дом элемента И i-й ячейки (К-1)-го повышения быстродействия, входы i-й столбца и выходом элемента ИЛИ

f , п п-1ч , . (i+1 )-й ячейки (К-1 )-го столбца,входы ячейки (i 1,2,..., -Х-) первого стол- .. f

-, tn (-)й ячейки К-го столбца соедибца соединены с входными информаци- iy 2-л

онными шинами 2i и (2i+l), входы пер- нены с выходом элемента И (-)-й

вой ячейки второго столбца соедине- - /ir ON

ячейки (К-2)-го столбца и выходом ны с первой входной шиной и выходом .

элемента РШИ первой ячейки первого ;элемента И ()-й ячейки (K-l)-ro

столбца, входы i-й ячейки К-го стол- 55

. столбца, входы первой ячейки т-го

бца (i 1 2 ... - К 2 4 ... столбца (т 3,5, . . . ,п) соединены с

2 выходом элемента ИЛИ первой ячейки п-1) соединены с выходом элемента И (т-2)-го столбца и выходом элемента

или первой ячейки (in-l)-ro столбца, входы j-й ячейки т-го столбца (j

2,3,..., г-) соединены с вуходом

элемента И (j-l)-й ячейки (m-l)-ro столбца и выходом элемента ИЛИ j-й

28.5590 р

ячейки (m-I)-ro столбца, выходы ячеек л-го столбца и выход элемента И

(-2--)-й ячейки (n-l)-ro столбца соединены с выходными информагщонными шинами.

. Фиг.г

Составитель О. Скворцов Редактор Н. Тупица Техред Л.ОлейникКорректор С. Шекмар

---.-.-.-..- --.-------- ----- ----------

Заказ 7535/57 Тираж 899 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов (его варианты) | 1980 |

|

SU1005307A1 |

| Однородная вычислительная структура для @ разложения матриц | 1984 |

|

SU1249531A1 |

| Устройство для сортировки двоичных чисел | 1989 |

|

SU1647562A1 |

| Оптимальный фильтр | 1987 |

|

SU1509934A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для сжатия векторов | 1987 |

|

SU1425704A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Преобразователь кодов | 1980 |

|

SU869030A1 |

Изобретение относится к области автоматики и вычислительной техники. Может быть использовано для построения различных устройств переработки дискретной информации. Цель изобретения - повышение быстродействия многопорогового элемента. Варианты много- порогового логического элемента объединены единым изобретательским замыслом - реализацией многопорогового элемента-на основе пар элементов И и ИЛИ, расположенных в виде треуголь- ной матрицы. Варианты отличаются организацией связей в зависимости от соотношений числа входов порогов. 4 с.п. ф-лы, 4 ил, 4 табл. с @

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ | 0 |

|

SU284433A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мажоритарный элемент | 1977 |

|

SU629640A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-07-08—Подача