Изобретение относится к технике передачи дискретной информации и может использоваться для синхронизации передатчика с рассредоточенными приемниками.

Цель изобретения повышение помехоустойчивости.

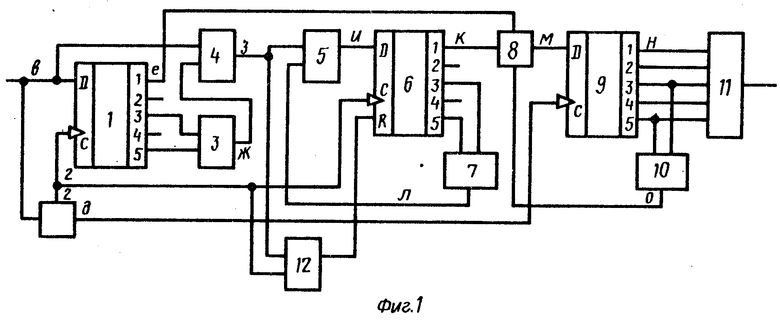

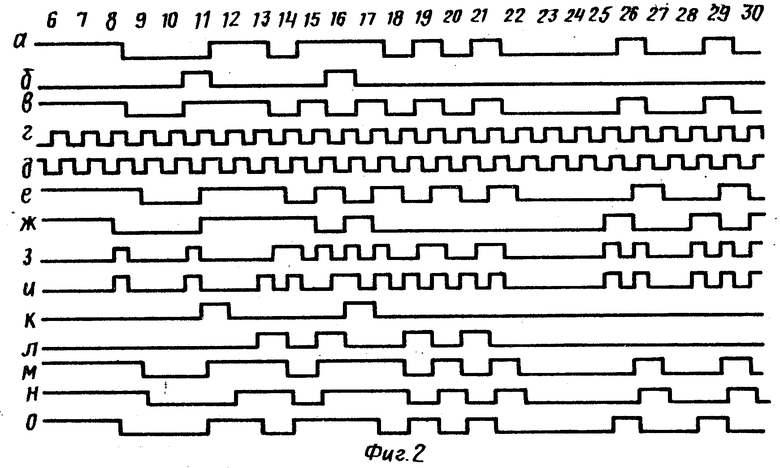

На фиг. 1 представлена структурная электрическая схема устройства для синхронизации передатчика с рассредоточенными приемниками; на фиг.2 временные диаграммы, поясняющие его работу.

Устройство для синхронизации передатчика дискретных сигналов с рассредоточенными приемниками содержит первый регистр 1 сдвига, блок 2 выделения тактовой частоты, первый формирователь 3 сигналов обратной связи, первый сумматор 4 по модулю два, второй сумматор 5 по модулю два, коммутатор 6, второй регистр 7 сдвига, второй формирователь 8 сигналов обратной связи, третий регистр 9 сдвига, третий формирователь 10 сигналов обратной связи, дешифратор 11 адреса, формирователь 12 сигналов обнуления.

Устройство работает следующим образом.

В передатчике генератор синхропоследовательности, выполненный в виде регистра с замкнутой обратной связью, через формирователь сигналов обратной связи (на чертеже не показан), вырабатывает кольцевую кодовую последовательность (см. фиг.2а) которая поступает в линию связи и используется для синхронизации передатчика и рассредоточенных приемников. На фиг.2б приведены ошибки, приводящие к искажениям сигнала, а на фиг.2в искаженная последовательность, поступающая на вход устройства; на фиг.2г и 2д приведены тактовые сигналы, формируемые блоком 2 на первом и втором выходах. Незначительный фазовый сдвиг между ними необходим для исключения в устройстве состязаний. На фиг. 2е, 2ж и 2з приведены диаграммы сигналов соответственно на первом выходе первого регистра 1, выходе первого формирователя 3 ("ожидаемый сигнал") и первого сумматора 4. В исходном состоянии третий регистр 9 обнулен. Тогда на выходе третьего формирователя 10 (см.фиг.2л) присутствует нулевой сигнал и на первый вход третьего регистра 9 (см.фиг.2и) поступает сигнал с выхода первого сумматора 4 (см.фиг.7з) как и в известном устройстве осуществляется фиксация первой ошибки (см.фиг.2к). Если бы обратная связь через третий формирователь 10 была разорвана, на первом выходе третьего регистра 9 присутствовали бы сигналы "ложной тревоги". Однако третий формирователь 10, включенный аналогично первому формирователю 3, на своем выходе (см.фиг.2л) формирует единичные сигналы на тех тактах, где на выходе первого сумматора 4 в момент записи в третий регистр 9 присутствуют сигналы "ложной тревоги".

Второй сумматор 5 при наличии единиц на выходе третьего формирователя 10 инвертирует сигналы с выхода первого сумматора 4; третий регистр 9 сигналов "ложной тревоги" не фиксирует. Это происходит потому, что третий регистр 9 с третьим формирователе 10 и вторым сумматором 5 позволяют учесть "последействием" помехи и избежать формирования сигналов "ложной тревоги" и ошибка (см. фиг. 2к) фиксируется только на том такте, где она присутствует (см.фиг.2б).

В нашем случае вторая ошибка приходит на пятом такте после первой (см. фиг.2б), когда "ожидаемый" сигнал на выходе первого формирователя 3 искажен, совпадает с искаженным входом и, следовательно, на выходе первого сумматора 4 присутствует "0" (ошибка якобы отсутствует). Однако на выходе третьего формирователя 10 в этот момент присутствует единичный сигнал (память о фиксации первой ошибки), и на первом входе третьего регистра 9 появляется сигнал логической единицы, фиксирующийся на время очередного такта третьим регистром 9 (см.фиг.2к).

Таким образом, при нахождении третьего регистра 9 при включении аппаратуры в нулевом состоянии на первом его выходе происходит выявление всех без исключения ошибок, искажающих синхросигнал. Если исходное состояние третьего регистра 9 не нулевое, а на вход устройства поступает неискаженный сигнал, на выход первого сумматора 4 в момент переключения третьего регистра 9 присутствуют нулевые сигналы; на первый вход третьего регистра 9 поступает сигнал с выхода третьего формирователя 10, т.е. обратная связь замыкается и третий регистр 9 переходит в автономный режим работы подобно генератору кода на передаче. На первом выходе третьего регистра 9 в этом случае появляется последовательность, аналогичная приведенной на фиг.2а, и воспринимаемая коммутатором 6 как поток ошибок (сигналы "ложной тревоги").

При возможных внутренних сбоях устройства синхронизации (в частности, третьего регистра 9) необходимо вновь обнулить его при отсутствии помех. Это возможно, если формирователь 12, кроме импульса исходной установки третьего регистра 9, будет формировать периодические короткие импульсы, в нормальном режиме не оказывающие влияния на работу устройства, но в случае внутренних сбоев осуществляющие обнуление третьего регистра 9 и восстановление нормальной работы схемы.

При выявлении ошибок единичный сигнал с выхода третьего регистра 9 (см. фиг.2к) переключает коммутатор 6, подключающий выход второго формирователя 8 (см.фиг.2б) к первому входу второго регистра 7 (см.фиг.2м). Второй регистр 7 переходит в автономный режим работы, осуществляя регенерацию синхросигнала при воздействии помех. Сигнал на выходе второго регистра 7 (см.фиг.2н) в точности соответствует при этом исходному, генерируемому на передающей стороне (см. фиг. 2а), взятому с незначительным сдвигом, не превышающим одного такта. Дешифратор 11 избирает тот объект, на адрес которого он настроен.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПЕРЕДАТЧИКА ДИСКРЕТНЫХ СИГНАЛОВ С РАССРЕДОТОЧЕННЫМИ ПРИЕМНИКАМИ | 1983 |

|

SU1126185A1 |

| Устройство фазирования по циклам | 1988 |

|

SU1601773A1 |

| Устройство для передачи и приема дескретных сообщений | 1990 |

|

SU1786669A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Преобразователь перемещения в код | 1984 |

|

SU1166309A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1256159A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1981 |

|

SU1840033A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

1. УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПЕРЕДАТЧИКА ДИСКРЕТНЫХ СИГНАЛОВ С РАССРЕДОТОЧЕННЫМИ ПРИЕМНИКАМИ, содержащее первый и второй регистры сдвига, блок выделения тактовой частоты, первый и второй формирователи сигналов обратной связи, первый сумматор по модулю два, коммутатор и дешифратор адреса, причем вход устройства соединен с входом блока выделения тактовой частоты, первым входом первого регистра сдвига и первым входом первого сумматора по модулю два, второй вход которого соединен с выходом первого формирователя сигналов обратной связи, первый и второй входы которого подключены к соответствующим выходам первого регистра сдвига, первый и второй входы коммутатора соединены соответственно с первым выходом первого регистра сдвига и выходом второго формирователя сигналов обратной связи, входы которого соединены с соответствующими выходами второго регистра сдвига, первый вход которого подключен к выходу коммутатора, а выходы соединены с входами дешифратора адреса, выход которого является выходом устройства, первый и второй выходы блока выделения тактовой частоты соединен с вторыми входами соответственно первого и второго регистров сдвига, отличающееся тем, что, с целью повышения помехоустойчивости, введены третий регистр сдвига, третий формирователь сигналов обратной связи и второй сумматор по модулю два, причем первый вход второго сумматора по модулю два соединен с выходом первого сумматора по модулю два, второй вход второго сумматора по модулю два соединен с выходом третьего формирователя сигналов обратной связи, входы которого подключены к соответствующим выходам третьего регистра сдвига, первый и второй входы которого подключены соответственно к выходу второго сумматора по модулю два и первому выходу блока выделения тактовой частоты, а первый выход - к третьему входу коммутатора.

2. Устройство по п.1, отличающееся тем, что в него дополнительно введен формирователь сигналов обнуления, причем первый вход и выход формирователя сигналов обнуления подключен соответственно к выходу первого сумматора по модулю два и к третьему входу третьего регистра сдвига, а второй вход формирователя сигналов обнуления соединен с первым выходом блока выделения тактовой частоты.

| Патент США N 3445815, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПЕРЕДАТЧИКА ДИСКРЕТНЫХ СИГНАЛОВ С РАССРЕДОТОЧЕННЫМИ ПРИЕМНИКАМИ | 1983 |

|

SU1126185A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1996-04-27—Публикация

1985-04-08—Подача