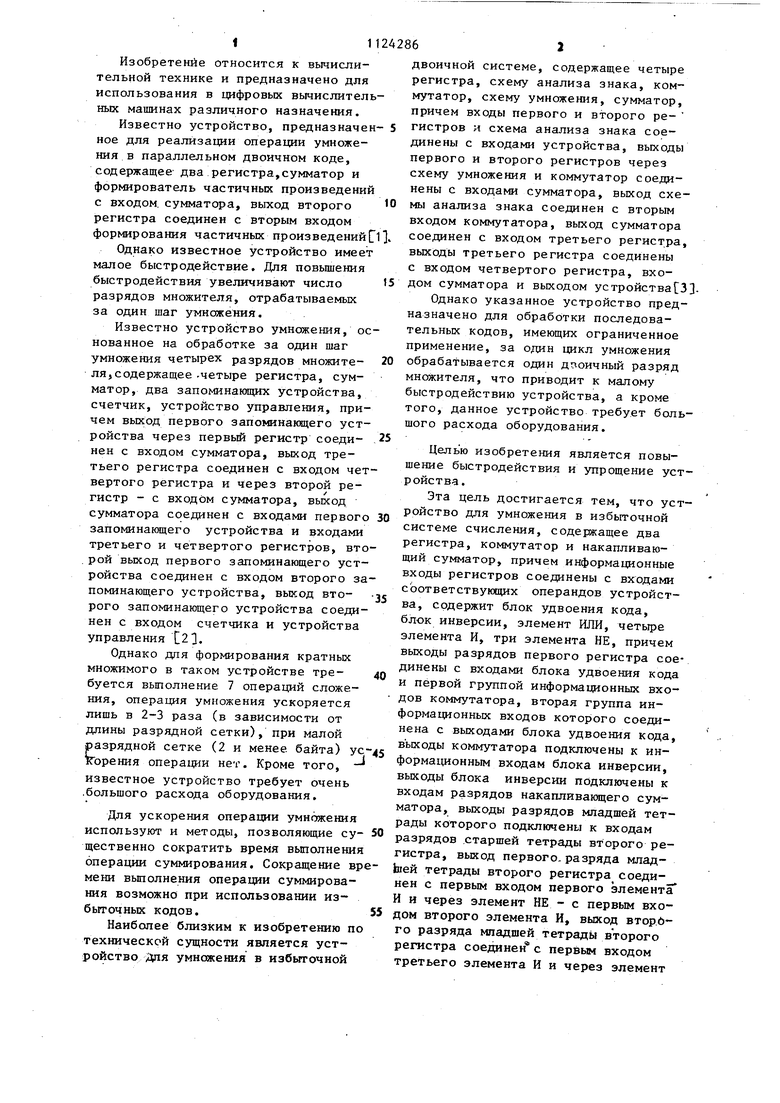

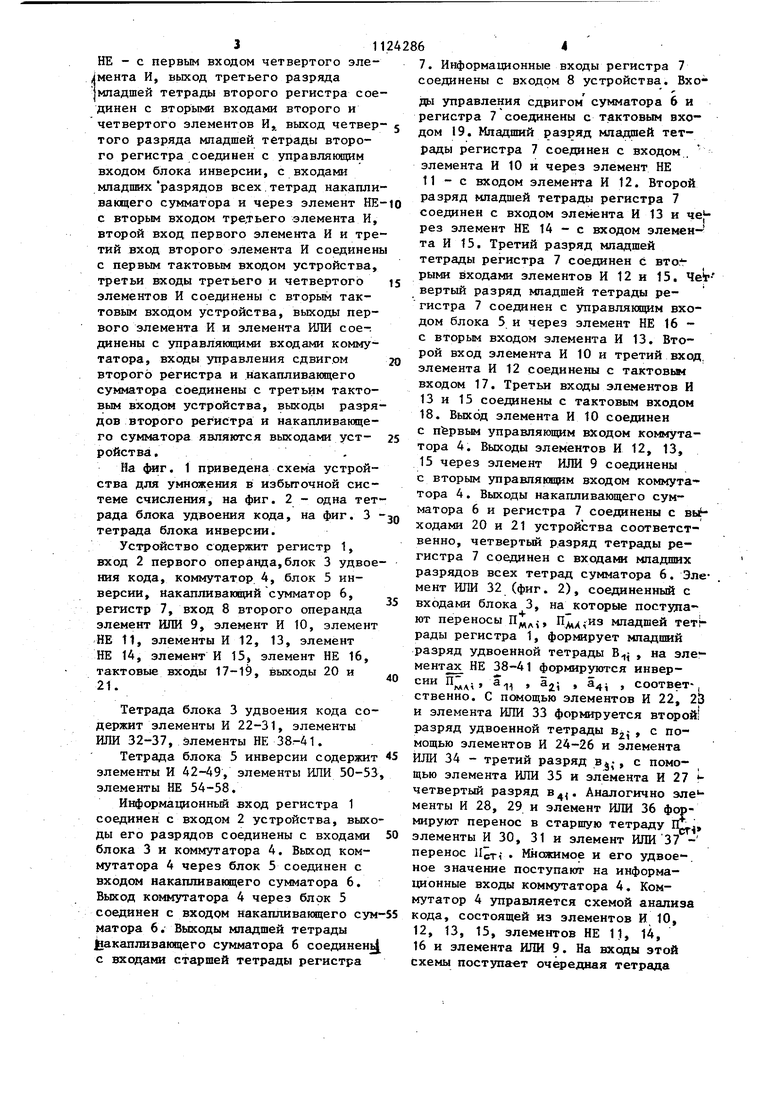

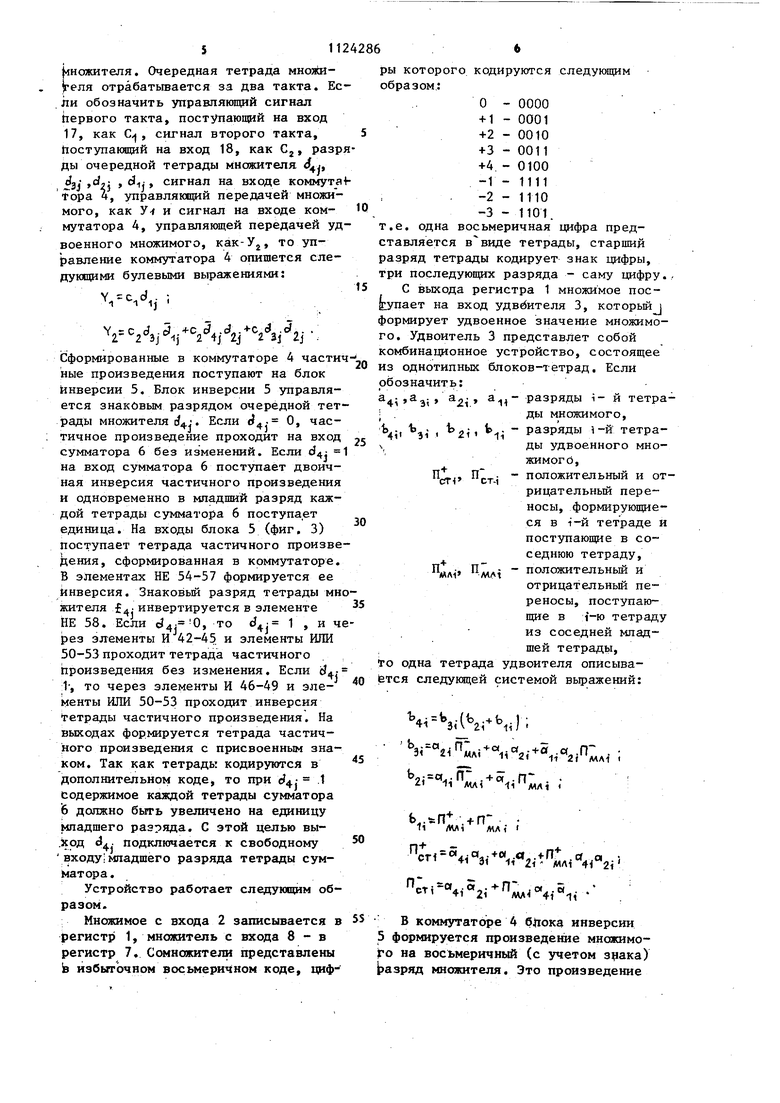

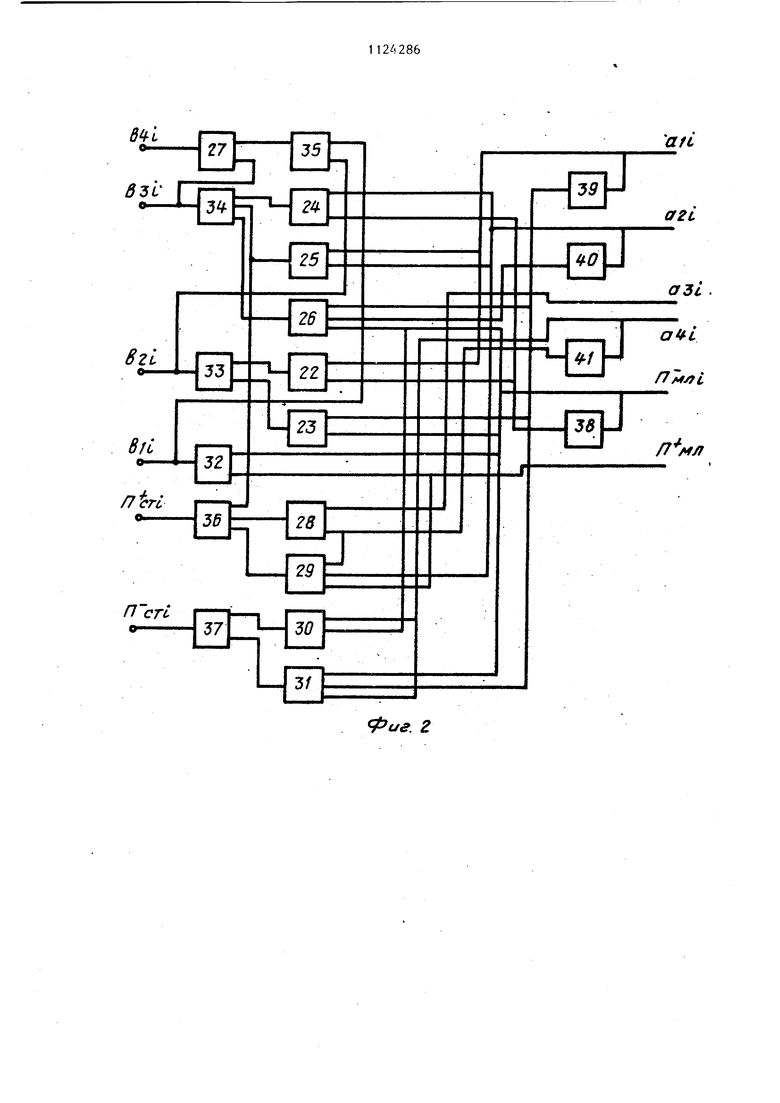

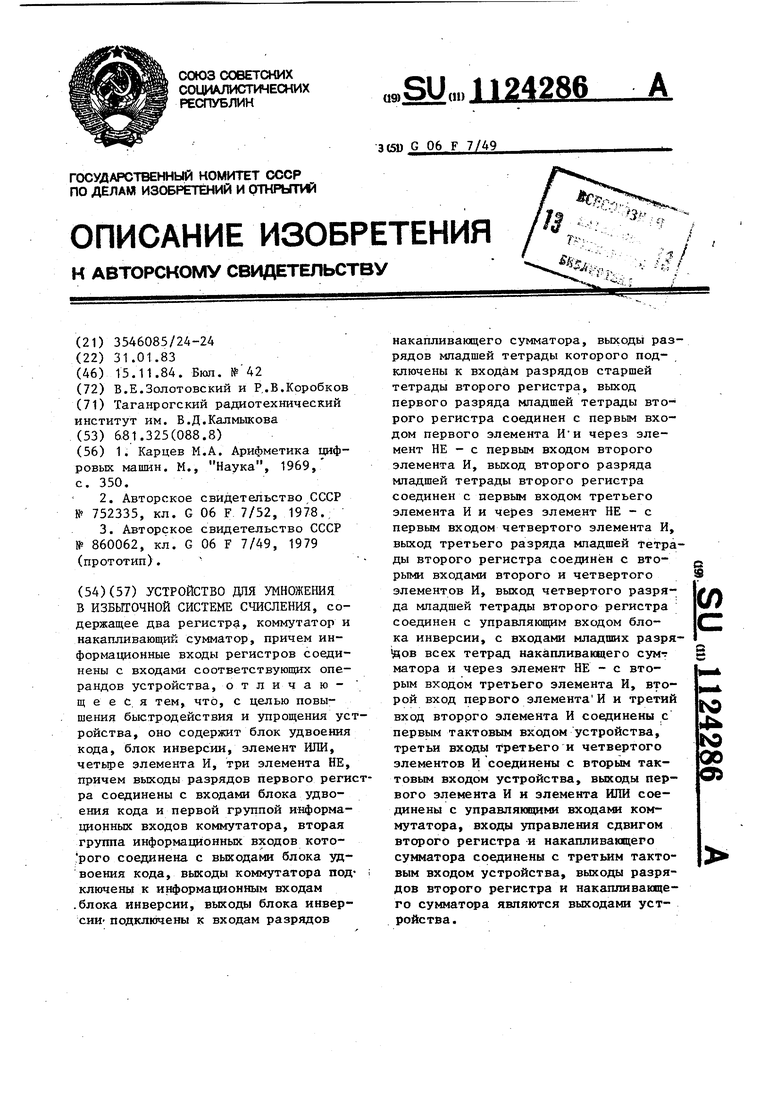

Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислитель ных машинах различного назначения. Известно устройство, предназначен ное для реализации операции умножения в параллельном двоичном коде, содержащее два регистра,сумматор и формирователь частичных произведений с входом, сумматора, выход второго регистра соединен с вторым входом формирования частичных произведений Однако известное устройство имеет малое быстродействие. Для повьшения быстродействия увеличивают число разрядов множителя, отрабатываемых за один шаг умножения. Известно устройство умножения, ос нованное на обработке за один шаг умножения четырех разрядов множителя, содержащее -четыре регистра, сумматор, два запоминающих устройства, счетчик, устройство управления, причем выход первого запоминающего устройства через первый регистр соединен с входом сумматора, выход третьего регистра соединен с входом чет вертого регистра и через второй регистр - с входом сумматора, выход сумматора соединен с входами первого запоминающего устройства и входами третьего и четвертого регистров, вто . рой выход первого запоминающего устройства соединен с входом второго за поминающего устройства, выход второго запоминающего устройства соединен с входом счетчика и устройства управления С21. Однако для формирования кратных множимого в таком устройстве требуется выполнение 7 операций сложения, операция умножения ускоряется лишь в 2-3 раза (в зависимости от длины разрядной сетки), при малой разрядной сетке (2 и менее байта) ус корения операции нет. Кроме того, известное устройство требует очень .большого расхода оборудования. Для ускорения операции умножения используют и методы, позволяющие су щественно сократить время выполнени операции суммирования. Сокращение вр мени выполнения операции суммирования возможно при использовании избыточных кодов. Наиболее близким к изобретению п технической сущности является устройство Дпя умножения в избыточной 1 62 двоичной системе, содержащее четыре регистра, схему анализа знака, коммутатор, схему умножения, сумматор, причем входы первого и второго регистров и схема анализа знака соединены с входами устройства, выходы первого и второго регистров через схему умножения и коммутатор соединены с входами сумматора, выход схемы анализа знака соединен с вторым входом коммутатора, выход сумматора соединен с входом третьего регистра, выходы третьего регистра соединены с входом четвертого регистра, входом сумматора и выходом ус тройства 3. Однако указанное устройство предназначено для обработки последовательньк кодов, имеющих ограниченное применение, за один цикл умножения обрабатывается один дт оичный разряд быстродействию устройства, а кроме того, данное устройство требует большого расхода оборудования. Целью изобретения является повышение быстродействия и упрощение устройства. Эта цель достигается тем, что устройство для умножения в избыточной системе счисления, содержащее два регистра, коммутатор и накапливающий сумматор, причем информационные входы регистров соединены с входами соответствукщих операндов устройства, содержит блок удвоения кода, блок инверсии, элемент РШИ, четыре элемента И, три элемента НЕ, причем выходы разрядов первого регистра соединены с входами блока удвоения кода и первой группой информационных входов коммутатора, вторая группа информационных входов которого соединена с выходами блока удвоения кода. f « коммутатора подключены к информационным входам блока инверсии, выходы блока инверсии подключены к входам разрядов накапливающего сумматора, выходы разрядов младшей тетрады которого подключены к входам разрядов .старшей тетрады второго регистра, выход первого., разряда младЬей тетрады второго регистра соединен с первым входом первого элемента И и через элемент НЕ - с первым входом второго элемента И, выход вторбго разряда младшей тетрады второго регистра соединен с первым входом третьего элемента И и через элемент НЕ - с первым входом четвертого элеyJMeHTa И, выход третьего разряда младшей тетрады второго регистра сое динен с вторыми входами второго и четвертого элементов И, выход четвер того разряда младшей тетрады второго регистра соединен с управлякшщм входом блока инверсии, с входами младшихразрядов всех тетрад накапли вающего сумматора и через элемент НЕ с вторым входом тре,тьего элемента И, второй вход первого элемента И и тре тий вход второго элемента И соединен с первым тактовым входом устройства, третьи входы третьего и четвертого элементов И соединены с вторым тактовым входом устройства, выходы первого элемента И и элемента ИЛИ сое-, динены с управляющими входами коммутатора, входы управления сдвигом второго регистра и накапливающего сумматора соединены с третьим тактовым входом устройства, выходы разря дов второго регистра и накапливамщего сумматора являются выходами устройства, . На «tffltr. 1 приведена схема устройства для умножения в избыточной системе счисления, на фиг. 2 - одна тет рада блока удвоения кода, на фиг. 3 тетрада блока инверсии. Устройство содержит регистр 1, вход 2 первого операнда,блок 3 удвое ния кода, коммутатор 4, блок 5 инверсии, накапливающий сумматор 6, регистр 7, вход 8 второго операнда элемент ИЛИ 9, элемент И 10, элемент НЕ 11, элементы И 12, 13, элемент НЕ 14, элемент И 15, элемент НЕ 16, тактовые входы 17-19, выходы 20 и 21. Тетрада блока 3 удвоения кода содержит элементы И 22-31, элементы ИЛИ 32-37, элементы НЕ 38-41. Тетрада блока 5 инверсии содержит элементы И 42-49, элементы ИЛИ 50-53 элементы НЕ 54-58. Информационный вход регистра 1 соединен с входом 2 устройства, выхо ды его разрядов соединены с входами блока 3 и коммутатора 4. Выход коммутатора 4 через блок 5 соединен с входом накапливающего сумматора 6. Выход коммзггатора 4 через блок 5 соединен с входом накашшвакяцего сум матора 6. Выходы младшей тетрады яакапливающего сумматора 6 соединен с входами старшей тетрады регистра 7. Информационные входы регистра 7 соединены с входом 8 устройства. Входы управления сдригом сумматора 6 и регистра 7 соединены с тактовым вхо дом 19. Младший разряд младшей тетрады регистра 7 соединен с входом . элемента И 10 и через элемент НЕ 11 - с входом элемента И 12. Второй разряд младшей тетрады регистра 7 соединен с входом элемента И 13 и че рез элемент НЕ 14 - с входом элемен та И 15. Третий разряд младшей тетрады регистра 7 соединен с вто, рыми входами элементов И 12 и 15, вертый разряд младшей тетрады регистра 7 соединен с управлякхцим входом блока 5 и через элемент НЕ 16 с вторым входом элемента И 13. Второй вход элемента И 10 и третий вход, элемента И 12 соединены с тактовьм входом 17. Третьи входы элементов И 13 и 15 соединены с тактовым входом 18. Выход элемента И 10 соединен с nfepBbM управляющим входом коммутатора 4. Выходы элементов И 12, 13, 15через элемент ИЖ 9 соединены с вторым управпякщим входом коммутатора 4. Выходы накапливающего сумматора 6 и регистра 7 соединены с вь ходами 20 и 21 устройства соответственно, четвертый разряд тетрады регистра 7 соединен с входами младших разрядов всех тетрад сумматора 6. Элемент ИЛИ 32 (фиг. 2), соединенный с входами блока 3, на которые поступают переносы П, младшей тетЦ рады регистра 1, формирует младший разряд удвоенной тетрады В , на элементу НЕ 38-41 формируются инвер 2i 4i соответ-, ственно. С псмощью элементов И 22, 23 и элемента ИЛИ 33 формируется второй разряд удвоенной тетрады в. , с помощью элементов И 24-26 и элемента ИЛИ 34 - третий разряд , с помощью элемента ИЛИ 35 и элемента И 27 четвертый разряд в. Аналогично элементы И 28, 29 и элемент ИЛИ 36 формируют перенос в старшую тетраду П элементы И 30, 31 и элемент ИЛИ37 перенос Иёп Множимое и его удвое-. ное значение поступают на информационные входы коммутатора 4. Коммутатор 4 управляется схемой анализа кода, состоящей из элементов И 10, 12, 13, 15, элементов НЕ 11, 14, 16и элемента ИЛИ 9. На входы этой схемы поступает очередная тетрада йножителя. Очередная тетрада множи еля отрабатьшается за два такта. Если обозначить управляющий сигнал Ьервого такта, поступающий на вход 17, как С, сигнал второго такта,5 |1оступакщий на вход 18, как Cj, разряды очередной тетрады множителя tJj; ,d,; , d-tj, сигнал на входе KOMMyTaf тора ч, управлягащй передачей множимого, как У и сигнал на входе ком- Ю мутатора 4, управляющей передачей удвоенного множимого, как-У, то управление коммутатора 4 опишется следующими булевыми выражениями: i .jV4/ 2V2i-: сформированные в коммутаторе 4 частич-... ные произведения поступают на блок инверсии 5, Блок инверсии 5 управляется знаковым разрядом очередной тетрады множителя dt.: Если тичное произведение проходит на вход js сумматора 6 без изменений. Если 1 на вход сумматора 6 поступает двоичная инверсия частичного произведения и одновременно в младший разряд каждой тетрады сумматора 6 поступает единица. На входы блока 5 (фиг. 3) поступает тетрада частичного произведения, сформированная в коммутаторе. В элементах НЕ 54-57 формируется ее инверсия. Знаковьш разряд тетрады множителя .инвертируется в элементе НЕ 58. Если . то 1 , и через элементы И 42-45. и элементы ЮТИ 50-53 проходит тетрада частичного Произведения без изменения. Если (, то через элементы И 46-49 и эле- менты Ш1И 50-53 проходит инверсия тетрады частичного произведения. На выходах формируется тетрада частичного произведения с присвоенным знаком. Так как тетрады кодируются в дополнительном коде, то при , 1 содержимое каждой тетрады сумматора 6 должно быть увеличено на единицу младшего разряда. С этой целью вы.ход подключается к свободному входу: младшего разряда тетрады сумматора. Устройство работает следуюпщм образом. Множимое с входа 2 записывается в регистр 1, множитель с входа 8 - в регистр 7. Сомножители представлены 1в избыточном восьмеричном коде, цифрыоб т. ст ра тр Еу фо го ко из об 4 I 4 , То ет 5 го Ьа которого кодируются следующим азом: О - 0000 +1-0001 +2 - 0010 +3 - 0011 +4 - 0100 -1 - 1111 -2 - 1110 -3 - 1101. . одна восьмеричная 1щфра предвляется тетрады, старший ряд тетрады кодирует знак цифры, последующих разряда - саму цифру., С выхода регистра 1 множимое посает на вход удвйителя 3, которьй мирует удвоенное значение множимоУдвоитель 3 представлет собой бинационное устройство, состоящее однотипных блоков-тетрад. Если значить: 2i. и Разряды л- и тетрады множимого, 31 2ti ii разряды i-й- тетрады удвоенного множимого, П, IT. - положительнь1й и отрицательный переносы, формируюш 1еся в i-й тетраде и поступающие в соседнюю тетраду, MAi положительньш и отрицательньй переносы, поступающие в 1-ю тетраду из соседней младшей тетрады, одна тетрада удвоителя описывая следукщей системой вьфажений: ,-(-b.|; .-«,, 2г%п;;д,-«,,п;.; Ь-.П +П 1l MAi MAi .,.c,a.S стГ«4,-«2ГП;; д,«4,-5,. V / В коммутаторе 4 инверсии ормируется произведеше множимона восьмеричный (с учетом ) ряд множителя. Это произведение 711 поступает на вход сумматора 7, работающего в избыточньк кодак, и суммируется в нем с ранее накопленной суммой. По завершении отработки тетрады множителя на вход 19 поступает сигнал сдвига, содержимое сумматора 6и регистра 7 сдвигается на одну тетраду ,в сторону младших разрядов Умножение завершается после отработки последней тетрады, множителя. Старшие тетрады произведения из сумматора 6 поступают на выход 20 . устройства. Младшие тетрады из регистра 7 поступают на вькод 21 устройства. В отличие от прототипа данное уст ройство по всхпяет обрабатывать параллел ные жрды, используемые практи чески повсеместно. Для представления числа 2 в прототипе требуется п избыточных двоичных разрядов. Опера ция умножения занимает 2п тактов. В предлагаемом устройстве для пред ставления чисел такого же диапазона потребуется К тетрад, где К находи ся из вьфаже«ия , 2 , Ьткуда Отработка одной тетрады требует три такта и время умножения составяет (n + D тактов. Следовательно, вр§ 4Я умножения сокращается примерно в 2 раза Сравним прототип с данным, устройством по расходу оборудования. Прототип содержит четыре регистра, причем два из них (для сомножителей) предназначены для приема двоичного избыточного кода, т.е. представляют собой по два ДВОИЧШ11Х регистра и два для результата (эквивалентные обычным двоичным регистрам). В результате все регистры триггербв. Данное,устройство для построения регистров сомножителей требует триггеров (при равном диапазоне изменения чисел). В результате экономия составляет (- триггера. .Коьв утаторы и сумматоры прототипа и данного устройства примерно эквивалентны. Схема анализа знака .прототипа примерно эквивалентна четырем элементам И, трем элементам НЕ и одному элементу ИЛИ. Схема умножения прототипа примерно эквивалентна блоку инверсии прилагаемого устройства. В результате данное устройство оказывается экономичнее прототипа почти на 30%.

Bff-l

J5

27

взс

f4

3

afi

ffZL

25

26

ZL

33

22

о-

тгр

n-crl

30

37

Ч

5/

. г

(

dff

П

50

ffb

вГ

4t4(

52

4

a/

o

uF

54t

j-IslJ

5

cf

57

fAt

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ В ИЗБЫТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ, содержащее два регистра, коммутатор и накапливающий сумматор, причем информационные входы регистров соединены с входами соответствующих операндов устройства, отличающ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит блок удвоения кода, блок инверсии, элемент ИЛИ, четыре элемента И, три элемента НЕ, причем выходы разрядов первого регистра соединены с входами блока удвоения кода и первой группой информационных входов коммутатора, вторая группа информационных входов которого соединена с выходами блока удвоения кода, выходы коммутатора под- ; ключены к информационным входам .блока инверсии, выходы блока инверсии- подключены к входам разрядов накапливающего сумматора, выходы разрядов младшей тетрады которого подключены к входам разрядов старшей тетрады второго регистра, выход первого разряда младшей тетрады второго регистра соединен с первым входом первого элемента Ии через элемент НЕ - с первым входом второго элемента И, выход второго разряда младшей тетрады второго регистра соединен с первым входом третьего элемента И и через элемент НЕ - с первым входом четвертого элемента И, выход третьего разряда младшей тетрады второго регистра соединён с вторыми входами второго и четвертого элементов И, выход четвертого разря(Л да младшей тетрады второго регистра соединен с управляющим входом блока инверсии, с входами младших разря floB всех тетрад накапливающего сум- матора и через элемент НЕ - с вторым входом третьего элемента И, второй вход первого элементаИ и третий вход вторрго элемента И соединены с первым тактовым входом устройства, третьи входы третьего и четвертого элементов И соединены с вторым тактовым входом устройства, выходы первого элемента И и элемента ИЛИ соединены с управлякшщми входами коммутатора, входы управления сдвигом второго регистра и накапливающего сумматора соединены с третьим тактовым входом устройства, выходы разрядов второго регистра и накапливающего сумматора являются выходами устройства.

-, 45 ;

Pue. 3

58

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Способ приготовления консистентных мазей | 1912 |

|

SU350A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-01-31—Подача