11287148

Изобретение относится к вычислительной технике и может быть использовано при выполнении операций сложения и вычитания чисел со знаками.

Цель изобретения - уменьшение ал- j

С.. , п(,,„у, vc,,,,n,(, „V,

С,С,,,|, По„-, Л С,„„,П,(;„„У ,

паратурных затрат.

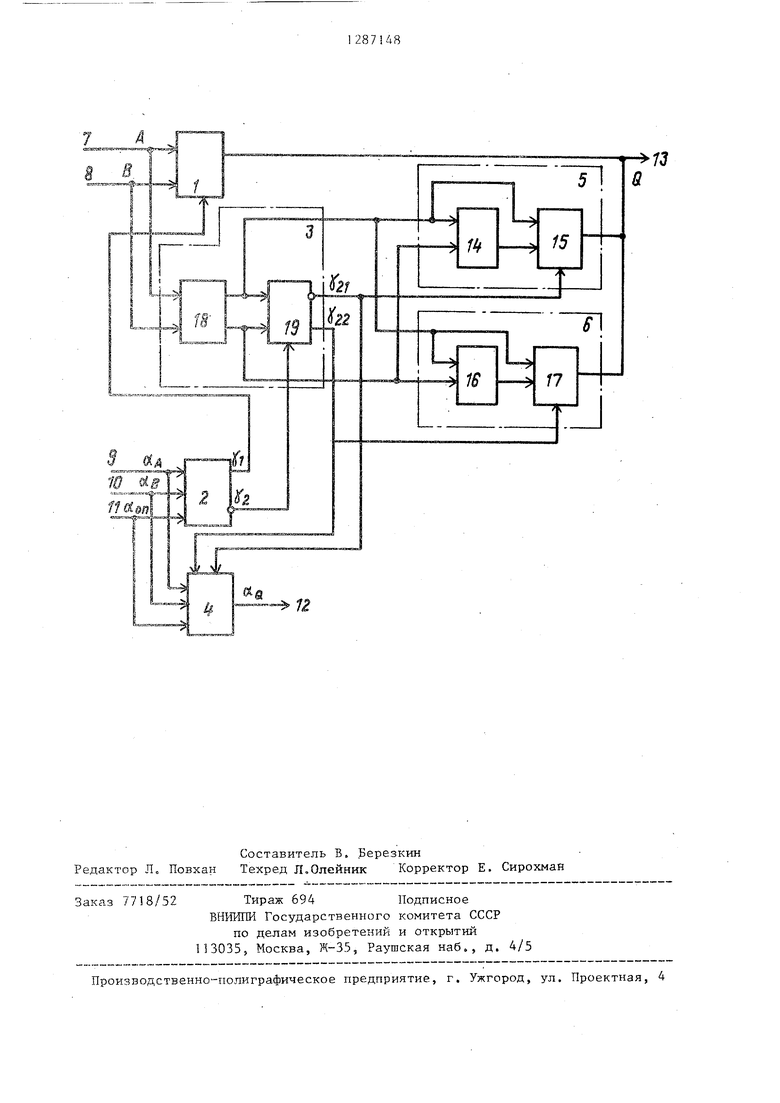

На чертеже показана функциональная схема устройства для сложения

и вычитания с .

Устройство содержит сумматор 1, Ш « ; -j-e значекие i-oro разряда г, . / полной суммы; блок 2 анализа знаков реализующий .„oin . -п на прямом и инверсном выходах значе- ния )- Сложение и - Вычита- - С,- .. - j-.e значение i-oro разряда ние соответственно), блок 3 сравне- полусуммы ния (реализующий значение сигналов п

Т - Ч в и f - А -i в COOT- 4(-т) - значение сигнала пере- ве ственно), блок 4 определения зна- из(1-1)-ого разряда в 1-й раз- ка результата, блок 5 формирования РЯД s

прямой разности, блок 6 формирования Полусумма 1-ого разряда реализует- обратной разности, входы 7 и 8 пер- 20 ся по выражениям вого и второго операндов (А, В), входы 9 и 10 знаков первого и второго операндов ( 5,), вход 11 знака операции (о), выход 12 знака

(о(.), информационный выход 13 (значения Q). Блок 5 содержит узел 14 формирования разрядных эаемов при прямом вычитании и полувычитатель 15.

(2)

Coi,, 0, V а,, Ъ,;Уа,. b.Va Ъ, jC,,-,,i2 аоьЪ,( V а. Ъ„.Уа. ,Va,,b,i C.i,i|a а„,Ъ,, а, Чi V a,b,V а.

Сз;,. Ъ„ V а,;Ъ,,Уа.,Ъ„

Блок 6.содержит узел 16 формированиягде а. - j-e значение i-oro разряда

разрядных заемов при обратном вычи- первого операнда;

тании и полувычитатель 17, Блок 3Ъ - j-e значение 1-ого разряда

содержит узел 18 формирования пораз-второго операнда.

рядных разностей и заемов и узел 19Обозначим через П ( П, , ,

формирования заема из старшего раз-. (-i) значение сигнапа переноса в

ряда.35 младший (нулевой) разряд. Так как

Рассматривают работу устройствазначение П равно нулю, то П,, 1

для количества разрядов п 4 с при-Ги П, . 0. С учетом этого одновременением кода 1 из 4,менное распространение сигналов переСумматор 1 в каждом разряде реализует следующие переключательные функции:

оо оо,1Г2 За,13

ol 01,1/2 Ji,i|5 oo,il2 31,1(1 io,i/5

,1 l 0- f2 oi,,,, ,ll2 31,1/2 i0.

,14 SSjIz Ou,ily 33,1/2 52,, ,1/2 i5,ll5 31-1(. l2

ir Г С С

ii,iia ,1(2

Пю nio,f/2

11,,il2 10,112

t2.l 5 ,,1(,l(7-31,,1/l

13 n,j,,jVCjj i|in,,,,|2Cj5,,,jn,,,jVC,,2C, ,,1/,

С., с„,,„ п„(,,, y,v с,„„, п,. Y,

с,. C,,,,n(,,,Y,V С„,,„ П,,,,

(1)

С.. , п(,,„у, vc,,,,n,(, „V,

С,С,,,|, По„-, Л С,„„,П,(;„„У ,

ет-

(2)

40

носа в сумматоре 1, реализуется в соответствии со следующими переключательными функциями:

3 12871484

П,,|, - ,k-e значение сигнала по- полнения. луперен оса из 1-го в (1+1)-й разряд. Полуперенос из 1-ого в (1 + 1)-й

Сигнал П {П, П,51 можно ис- разряд формируется в . соответствии с пользовать в качестве признака пере- выражениями

П „ a--b-va b.va.b.va.b-va Ъ ja Ъ

Ot. О)01 1101 -Zl11 01ti 01

п.,.b,-va.b-.Va.b.va b va.b.va, b,

Iijf/iH 3121 2)2l 3i31 1i3t 21 3i 3i

Для получения окончательной разности А-В блок 5 в каждом разряде реализует следующие переключательные функции:

,,, (,-,) y.,M,Mi-)D,, о;;,,„г..,/в;,,,

с;,,,), 1(,-1,, D;,,,,,r/j.,if,,

Dj, о;„,/2 -о(,.,;,/. ь /2 i(i-i)5

Полуразность (разрядная разность) i-ого разряда реаттизуется узлом 18 по вьфажениям

D ., а . b V а . b . V а . Ь„ - Va .Ь,.

01|ll201 0111 (11 11 31 31

15

D .

. , - сд, . b,- / а b V а t . v а . Ь,:

11,1/201 3 )1 fiл -V

а .

1(6)

D а . Ь„. V а . b va . b . /а . b .

91, ч 0131 1i

1 1

V l, - а, Ч, . Ъ, Обозначим через ,,) (.,j

Jr TTOTt/tiiT. .Г чтт .л .

21 01, JZ ui-1) Z.I 20

где D j - j-e значение i-ого разрядаG , значение сигнала заема в младокончательной разности А-В; j птй (нулевой) разряд. Так как значе О, 1, 2, 3; i 0, 1, 2, 3;ние G .J равно нулю, то G (.,) I и

DJ; ,|,j.- j-e значение i-oro разря- i {-i) учетом этого одновременда полуразности А-В;25 ое распространение сигналов заема

G|((,.,)- k-e значение сигнала зае- для разности А-В и формирование сиг.ма из (1-1)-ого разряда в 1-й разрядналов сравнения операндов по модулю

дпя разности А-В;реализуется узлами 14 и 19 в соответk О, 1.ствии с выражениями

I

00 00,11 ой,1|а

GO, 0,, i,0,,1IZ,00,1/S

ог ,-,,,,,,,,.,,, (7)

2, G;, G;,,,,,,,G;,,,,i,vD;3,,,D;,,,,G;,,,,

Vtto oN /2 -00,./ ,iia D;,,.,,,D;,,, D;.., j.

fo,i/a

1, °«,f/ °0,,,te °io,f/2

(2 (2,f/2 .l// .Т/С Ot,f/2 10,1/2

.2 « G. 3,i|3l aV o3,,feGi7,.,.,)aV

Iii I

0.3, ,)/7 0 1,1/2 .m y ,

где G. ,j - k-e значение сигн.ала по- Полузаем из i-ого в (1+1 )-й раз- лузаема {поразрядного заема) из 1-ого ряд формируется узлом 18 в соответст- в (1+Т)-й разряд для разности А-В;

ВИИ с выражениями:

М12 .- oi i oi Va. b. va. b, va. b,, V , M-,i« 01 , V a,b,,va. b, Va,, b,. Va,. b.va,, b,.

(a)

(4)

Полуразность (разрядная разность) i-ого разряда реаттизуется узлом 18 по вьфажениям

D ., а . b V а . b . V а . Ь„ - Va .Ь,.

01|ll201 0111 (11 11 31 31

D .

. , - сд, . b,- / а b V а t . v а . Ь,:

11,1/201 3 )1 fiл -V

а .

1(6)

D а . Ь„. V а . b va . b . /а . b .

91, ч 0131 1i

V l, - а, Ч, . Ъ, Обозначим через ,,) (.,j

Jr TTOTt/tiiT. .Г чтт .л .

20

даG , значение сигнала заема в мл

птй (нулевой) разряд. Так как знач

(a)

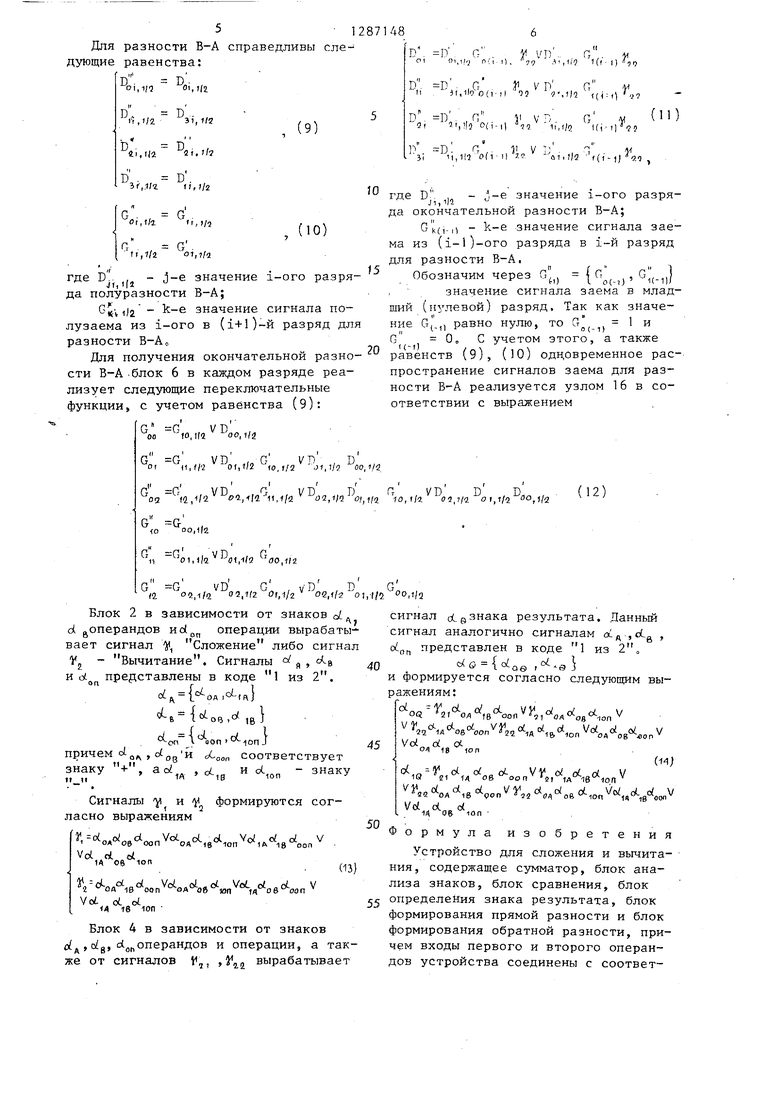

5 1287148

разности В-А справедливы слеравенства:

If)

oi,i(Q (, 1/г

rt , /2

,.

(9)

Г,- П

4l,r(2 2ь /г

3f,.i;i (i,;/2

Р

,)/2

I

г

01,7/а

(10)

G k(j-ii - k-e значе ма из (i-i)-oro разря для разности В-А. Обозначим через G

значение сигна нулевой) разряд.

0

шии

ние G| .,) равно нулю, т G Оо С учетом э равенств (9), (Ю) од пространение сигналов ности В-А реализуется ответствии с выражени

где D.. - j-e значение i-oro разряда полуразности В-А;

,) - k-e значение сигнала по- лузаема из i-oro в (1+1)-й разряд для разности В-Ао

Для получения окончательной разности В-А .блок 6 в каждом разряде реализует следующие переключательные функции, с учетом равенства (9):

ri п 1/ Г| .

00 -to, 1(2 00,1/2

/I IIIIt

Р -рV Пг I/TIП

ог ii,f/ 2 Of,т/2 fo,t/2 00, V5,

if) t/f1ff

02 W,.f/a /,f/a ,f/i 05.7/1 ,M1

r -G- o D0(ifu

Mf

, 1,( 1,1/2 ,f(2

p п n n

(2. 02,lfa ,. 05,(/2 o, |/5 0,1/2

Блок 2 в зависимости от знаков of

ерандов операции вырабатысигнал , Сложение либо сигнал oL - Вычитание. Сигналы , Q представлены в коде 1 из 2.

й: ,

« -в { ,0 ,в}

с.оп V oon Of-ionJ ем ot ,с.,„ й

си си

и ра

у

o II .11

45

°а ad

соответствует

1А

oL

1В

и d..

- знаку

Сигналы У и V формируются согласно вьфажениям

П ,,..

Гс1оЛв° ооп оА° об ««,, ..

Блок 4 в зависимости от знаков ( , , сАд операндов и операции, а также от сигналов V,, ,J,i,j вырабатывает

D

VI).. G

oi.if j o(t. I), 79 Л ,ii5 1((.

Y I) So

D. . , G . Ji V D Гт V

ll3t,ll9 0(1- ll ,)) ((j: ( /25

n v V / G M ( 1)

2 5|,|3 0(i-|| ,5 - i;,,;2 |(j, ,| i,5

G1 V T ,V

j; ii,1l7 o(i-i| . ,02 /(,.,; -fci,

где D. 1 - J-e значение i-oro разряда окончательной разности В-А;

G k(j-ii - k-e значение сигнала зае- ма из (i-i)-oro разряда в i-й разряд для разности В-А. Обозначим через ( ос-,) (-ц)

значение сигнала заема в млад- нулевой) разряд. Так как значе

шии

ние G| .,) равно нулю, то G° 1 и G Оо С учетом этого, а также равенств (9), (Ю) одновременное распространение сигналов заема для разности В-А реализуется узлом 16 в соответствии с выражением

(12)

oLQ

сигнал оСв знака результата. Данный сигнал аналогично сигналам х„.,оС„ .

О

oj представлен в коде 1 из 2,.

в(ав ,-в

и формируется согласно следующим выражениям:

, n,.« ,e oonV},,.o;oe.onV

V ... о,,Ы,„„ Voi Ы„„Ы, V

.8,о.

(я;

ie ni iHoe oo.Vn,o,,ot,gO(,V

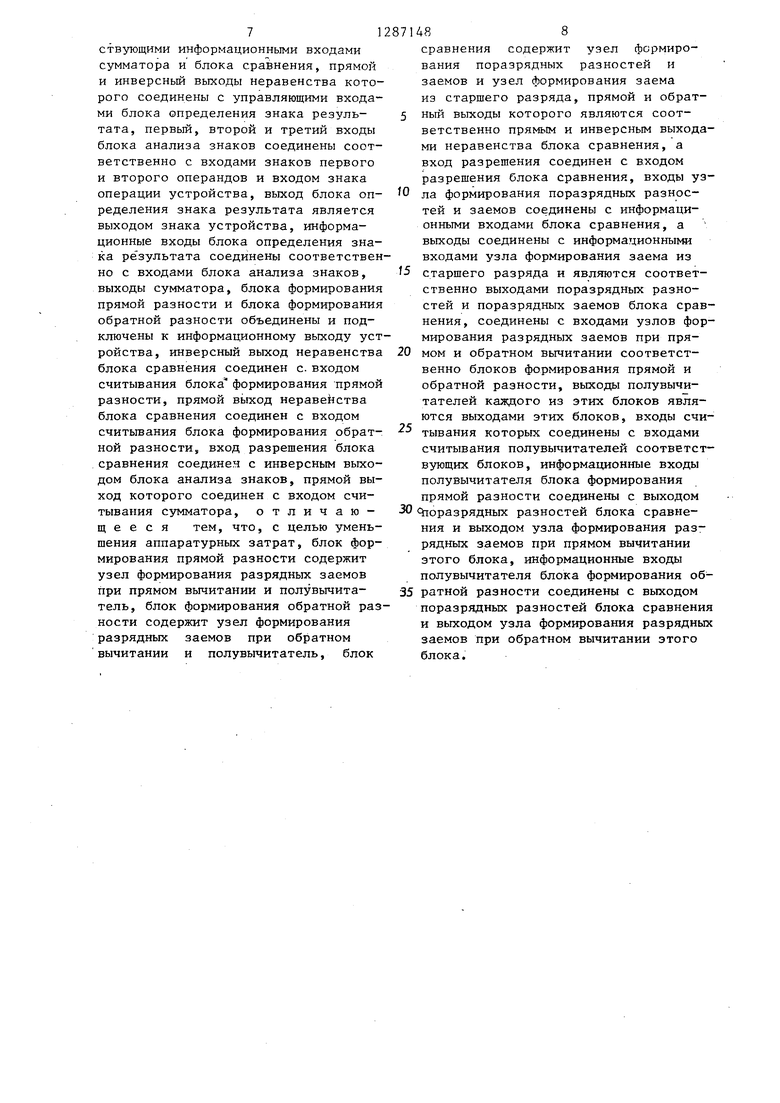

.. ОА у,, . 06 О.оп ,. .опФормула изобретения Устройство для сложения и вычитания , содержащее сумматор, блок анализа знаков, блок сравнения, блок определения знака результата, блок формирования прямой разности и блок формирования обратной разности, причем входы первого и второго операндов устройства соединены с соответ71

ствующими информационными входами сумматора и блока сравнения, прямой и инверсный выходы неравенства которого соединены с управляющими входами блока определения знака резуль- тата, первый, второй и третий входы блока анализа знаков соединены соответственно с входами знаков первого и второго операндов и входом знака операции устройства, выход блока оп- ределения знака результата является выходом знака устройства, информационные входы блока определения знака результата соединены соответственно с входами блока анализа знаков, выходы сумматора, блока формирования прямой разности и блока формирования обратной разности объединены и подключены к информационному выходу устройства, инверсный выход неравенства блока сравнения соединен с. входом считывания блока формирования прямой разности, прямой вьгход неравенства блока сравнения соединен с входом считывания блока формирования обрат- ной разности, вход разрешения блока сравнения соединен с инверсным выходом блока анализа знаков, прямой выход которого соединен с входом считывания сз мматора, отличаю- щ е е с я тем, что, с целью уменьшения аппаратурных затрат, блок формирования прямой разности содержит узел формирования разрядных заемов при прямом вычитании и полувьгчита- тель, блок формирования обратной разности содержит узел формирования разрядных заемов при обратном вычитании и полувычитатель, блок

488

сравнения содержит узел формирования поразрядных разностей и заемов и узел формирования заема из старшего разряда, прямой и обратный выходы которого являются соответственно прямым и инверсным выходами неравенства блока сравнения, а вход разрешения соединен с входом разрешения блока сравнения, входы узла формирования поразрядных разностей и заемов соединены с информационными входами блока сравнения, а выходы соединены с информационными входами узла формирования заема из старшего разряда и являются соответственно выходами поразрядных разностей и поразрядных заемов блока сравнения, соединены с входами узлов формирования разрядных заемов при прямом и обратном вычитании соответственно блоков формирования прямой и обратной разности, выходы полувычи- тателей каждого из этих блоков являются выходами этих блоков, входы считывания которых соединены с входами считывания полувычитателей соответствующих блоков, информационные входы полувычитателя блока формирования прямой разности соединены с выходом

поразрядных разностей блока сравнения и выходом узла формирования разрядных заемов при прямом вычитании зтого блока, информационные входы полувычитателя блока формирования обратной разности соединены с выходом поразрядных разностей блока сравнения и выходом узла формирования разрядных заемов при обратном вычитании этого блока.

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| ИТЕРАТИВНЫЙ СПОСОБ БЛОЧНОГО ШИФРОВАНИЯ | 1999 |

|

RU2172075C1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| Устройство для вычисления разностидВуХ -РАзРядНыХ чиСЕл | 1978 |

|

SU822182A2 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для формирования знака результата последовательного сложения | 1984 |

|

SU1193666A1 |

| Сумматор вычитатель | 1974 |

|

SU489105A1 |

| Матричное вычислительное устройство | 1984 |

|

SU1233141A1 |

Изобретение относится к вычислительной технике и может быть использовано при выполнении операций сложения и вычитания чисел со знаками. Целью изобретения является уменьшение аппаратурных затрат. Для достижения поставленной цели в устройстве, содержащем сумматор, блок анализа знаков, блок сравнения, блок определения знака результата, блок формирования прямой разности и блок формирования обратной разности, специальным образом вьтолнены блок сравнения, содержащий узел формирования поразрядных радиосетей и заемов и узел фор-, мирования заема из старшего разряда, и блоки формирования прямой и обратной разности, содержащие каждый по- лувычитатель и узел формирования разрядных заемов при соответственно прямом и обратном вычитании. 1 ил. (О (Л ГС 00 Nl 4;: 00

Составитель В, Березкин Редактор Л. Повхан Техред Л,Олейник Корректор Е. Сирохман

7718/52

Тираж 694 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1226443A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-19—Подача