Изобретение относится к вычислительной технике и может быть использовано в клавишных ЭВМ ив устройствах обработки информации.

Цель изобретения - упрощение устройства.

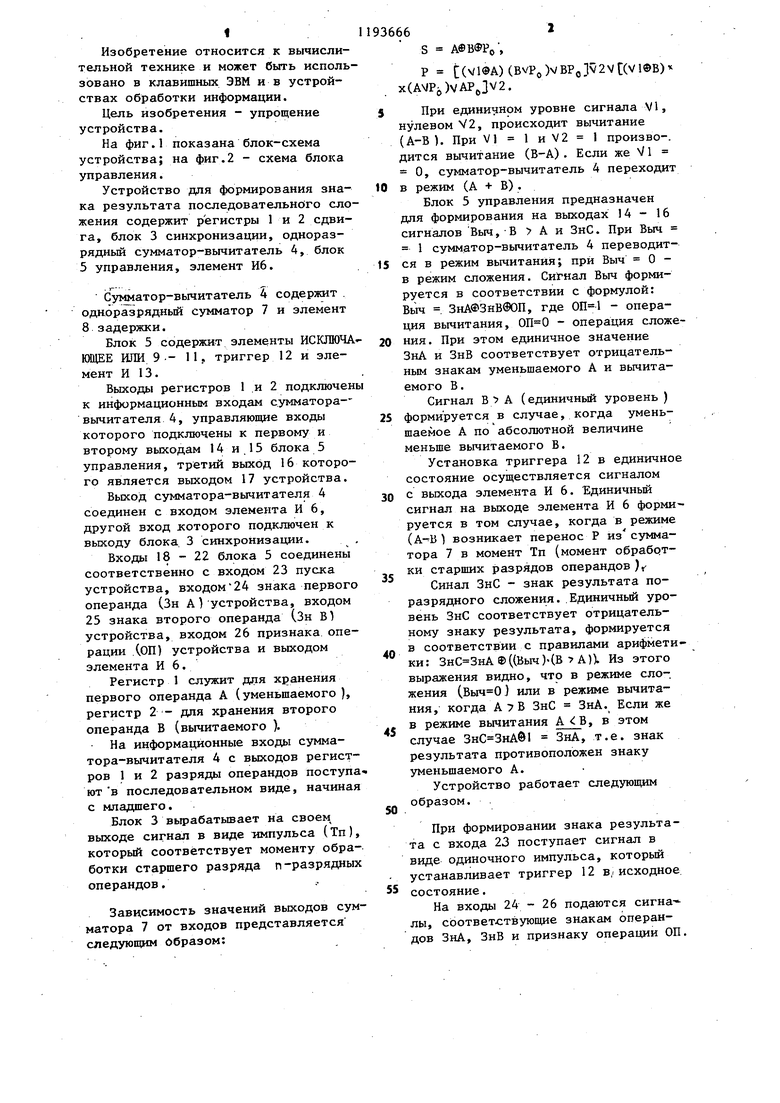

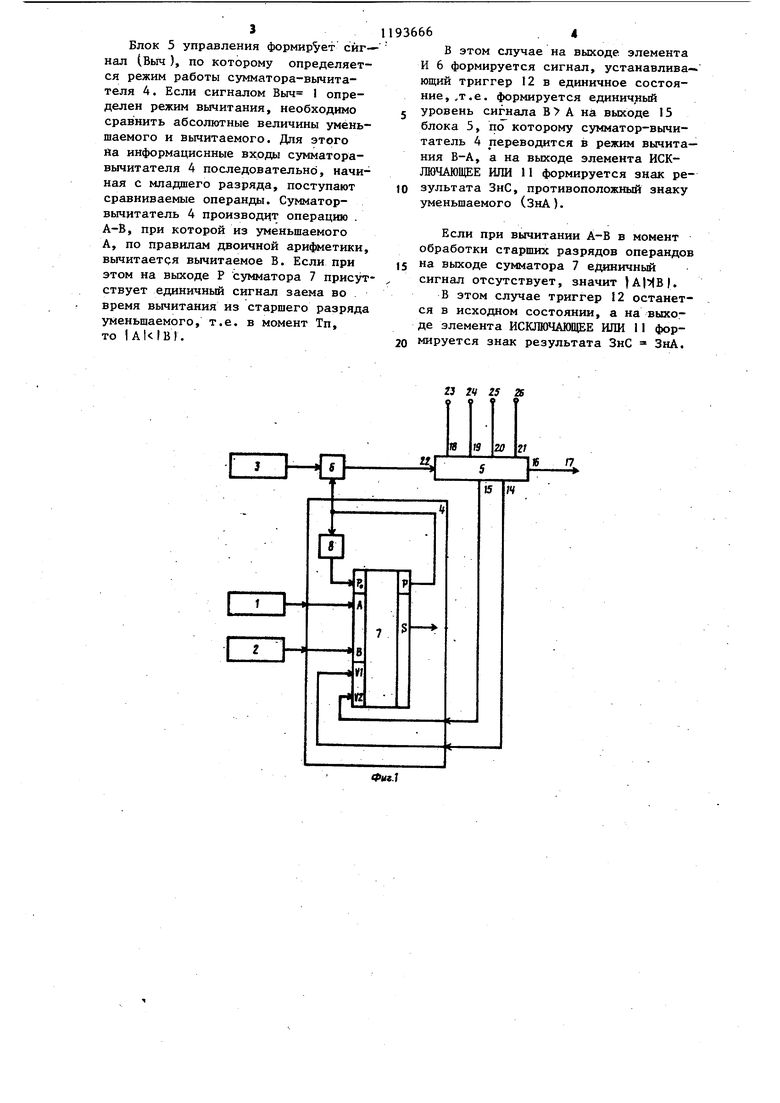

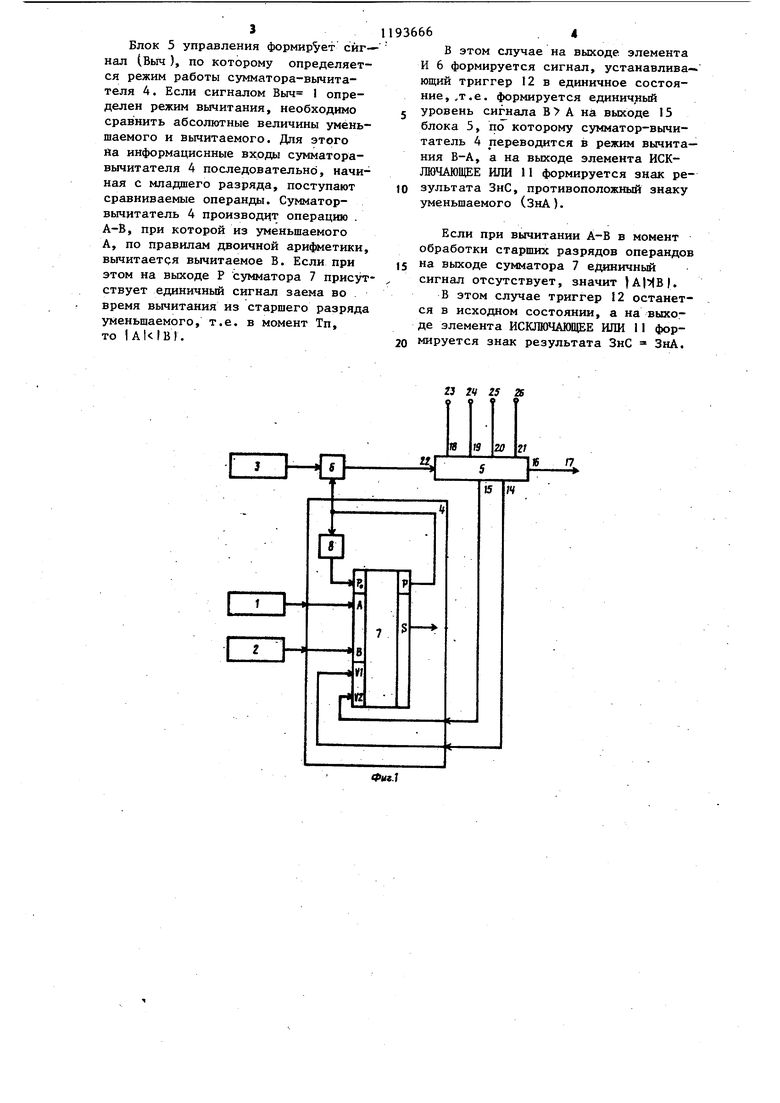

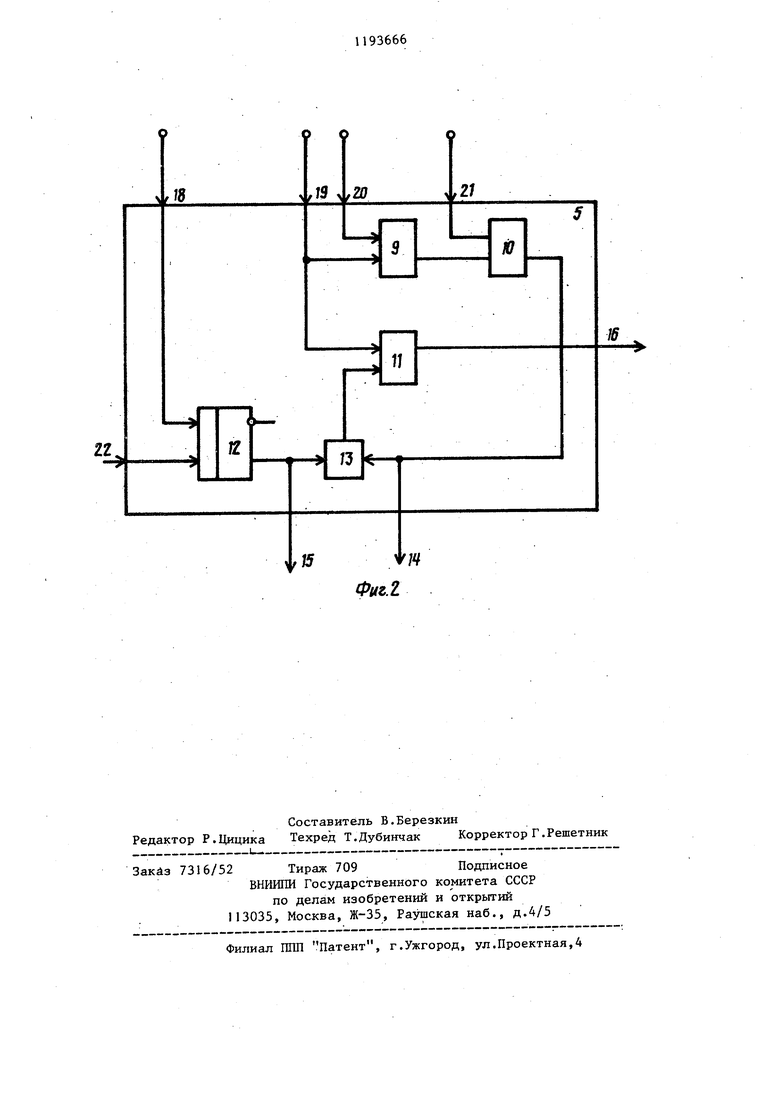

На фиг.1 показана блок-схема устройства; на фиг.2 - схема блока управления.

Устройство для формирования знака результата последовательного сложения содержит регистры 1 и 2 сдвига, блок 3 синхронизации, одноразрядный сумматор-вычитатель А, блок 5 управления, элемент И6.

Сумматор-вычитатель 4 содержит . одноразрядный сумматор 7 и элемент 8 задержки.

Блок 5 содержит элементы ИСКЛЮЧАЩЕЕ ИЛИ 9 .- 11, триггер 12 и элемент И 13.

Выходы регистров 1 .и 2 подключен к информационным входам сумматора- вычитателя 4, управляющие входы которого подключены к первому и второму выходам 14 и 15 блока 5 управления, третий выход 16 которого является выходом 17 устройства.

Выход сумматора-вычитателя 4 соединен с входом элемента И 6, другой вход которого подключен к выходу блока. 3 синхронизации.

Входы 18-22 блока 5 соединены соответственно с входом 23 пуска устройства, входом24 знака первого операнда (Зн А )устройства, входом 25 знака второго операнда (Зн В1 устройства, входом 26 признака операции ЛОП) устройства и выходом элемента И 6.

Регистр 1 служит для хранения первого операнда А (уменьшаемого ), регистр 2 - для хранения второго операнда В (вычитаемого ).

На ицформационные входы сумматора-вычитателя 4 с выходов регистров 1 и 2 разряды операндов поступа ютв последовательном виде, начиная с младшего.

Блок 3 вырабатьюает на своем, выходе сигнал в виде импульса (Тп), который соответствует моменту обработки старшего разряда п-разрядных операндов.

Зависимость значений выходов сумматора 7 от входов представляется следующим образом:

36662

S АФВФРо,

Р С(1®А) (Bvpg)(Vl®B)« x(A4/Pi)vAPjV2.

5 При единичном уровне сигнала VI, нулевом V2, происходит вычитание (А-Б ). При VI 1 и V2 ) произво-. дится вычитание (В-А). Если же V1 О, сумматор-вычитатель 4 переходит

0 в режим (А + В).

Блок 5 управления предназначен для формирования на выходах 14 - 16 сигналов Выч, В А и ЗнС. При Выч 1 сумматор-вычитатель 4 переводитt5 ся в режим вычитания; при Выч О в режим сложения. Выч формируется в соответствии с формулой: Выч ЗнАФЗнВФОП, где - операция вычитания, - операция сложения. При этом единичное значение ЗнА и ЗнБ соответствует отрицательным знакам уменьшаемого А и вычитаемого В.

Сигнал В 7 А (единичньй уровень )

5 формируется в случае, когда уменьшаемое А по абсолютной величине меньше вычитаемого В.

Установка триггера 12 в единичное состояние осуществляется сигналом

0 с выхода элемента И 6. Единичньй

сигнал на выходе элемента И 6 формируется в том случае, когда в режиме (А-В ) возникает перенос Р изсумматора 7 в момент Тп (момент обработки старших разрядов операндов)

Синал ЗнС - знак результата поразрядного сложения. Единичный уровень ЗнС соответствует отрицательному знаку результата, формируется

. в соответствии с правилами арифметики: ((Выч)ЧВ А)Х Из этого выражения видно, что в режиме ело-, жения ( или в режиме вычитания, когда А 7 В ЗнС ЗнА. Если же в режиме вычитания А В, в этом случае ЗнС ЗнА®1 ЗнА, т.е. знак результата противоположен знаку уменьшаемого А.

Устройство работает следующим образом. .

При формировании знака результата с входа 23 поступает сигнал в виде одиночного импульса, который устанавливает триггер 12 в/исходное. 5 состояние.

На входы 24 - 26 подаются сигна лы, сЬответствующие знакам операндов ЗнА, ЗнВ и признаку операции ОП.

Блок 5 управления формирует сигнал (Выч ), по которому определяется режим работы сумматора-вычитателя 4. Если сигналом Вьгч 1 определен режим вычитания, необходимо сравнить абсолютные величины уменьшаемого и вычитаемого. Для этого йа информационные входы сумматоравычитателя 4 последовательно, начиная с младшего разряда, поступают сравниваемые операнды. Сумматорвычитатель 4 производит операцию , А-В, при которой из уменьшаемого А, по правилам двоичной арифметики, вычитается вычитаемое В. Если при этом на выходе Р сумматора 7 присутствует единичный сигнал заема во время вычитания из старшего разряда уменьшаемого, т.е. в момент Тп, то lAklBI.

193666. 4

В этом случае на выходе элемента И 6 формируется сигнал, устанавливающий триггер 12 в единичное состояние, т.е. формируется единичный 5 уровень сигнала В А на выходе 15 блока 5, по которому сумматор-вычитатель 4 переводится в режим вычитания В-А, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 формируется знак результата ЗнС, противоположный знаку уменьшаемого (ЗнА).

Если при вычитании А-В в момент обработки старших разрядов операндов J5 на выходе сумматора 7 единичный сигнал отсутствует, значит ).

В этом случае триггер 12 останется в исходном состоянии, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ II формируется знак результата ЗнС ЗнА.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

. УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЗНАКА РЕЗУЛЬТАТА ПОСЛЕДОВАТЕЛЬНОГО СЛОЖЕНИЯ, содержащее одноразрядный сумматор-вычитатель, блок управления, блок синхронизации, первый и второй .регистры сдвига, элемент И, причем первый и второй выходы блока управ- ления подключены к управляющим входам одноразрядного сумматора-вычитателя, первый информационный вход которого подключен к выходу первого регистра сдвига, а выход блока синхронизации подключен к первому входу элемента И, отличающее с я тем, что, с целью упрощения устройства, второй информационный вход одноразрядного сумматоравычитателя подключен к выходу второго регистра сдвига, а выход перено-са - к второму входу элемента И, при этом блок управления содержит три элемента ИСКЛЮЧАКЩЕЕ ИЛИ, элемент И и триггер, нулевой вход которого соединен с первым входом блока управления, подключенным к входу пуска устройства, входы знаков первого и второго операндов устройства соединены соответственно с вто-рым и третьим входами блока управления, подключенными соответственно к первому и второму входам первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом второ го элемента ИСКЛЮЧАНЩЕЕ ИЛИ, второй вход которого .подключен к четвертому входу блока управления, соединенному с входом признака операции устройства, выход второго элемента (Л ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом блока управления и первым входом элемента И блока управления, второй вход которого подключен к прямому выходу триггера, а выход к первому входу третьего элемента ИСКЛЮЧАЮЩЕЕ ШШ, второй вход кото-, QD 00 Од рого соединен с первым входом первого элемента ИСКЛЮЧАРЦЕЕ ИЛИ, а выход - с третьим выходом блока О) : управления, подключенным к выходу Од устройства, выход элемента И соеди- нен с пятым входом блока управления, подключенным к единичному входу, триггера, прямой выход которого соединен с вторым выходом блока управления .

23 24 25 26

П

W

15

CZ3сю

О о

19

78

f f

-J

И

гз

иг

.21

Ю

Ч

i/e.Z

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-23—Подача