7ДЗ

гэ

4

00

00

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации.

Цель изобретения - расширение функционалыаис возможностей за счет формирова 1ия остатка по модулю К от входного кода.

19 и 20 синхронизации и обнуления и вьгходы 21. При этом 1--й выход делителя 9 (i - 1, Р-1), соединенный с входом i-ro элемента И 7, соответствует коэффициенту деления, равному весу по модулю К (1+1)-й группы информационных входов 10-,

Устройство для подсчета числа еди

Изобретение относится к вычис;- лительной технике. Его использование в системах передачи и обработки дискретной информации позволяет расшиш{т рить функциональные возможности устройства за счет формирования остатка по модулю К от входного кода. Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательность импульсов, триггер 3, счетчик 5 по модулю К, блоки 6 подсчета единиц по модулю К, элементы И 7 и элемент ШШ 8. 1. Благодаря введению элемента ЗАПРЕТ 4, элемента ИЛИ 8.2 и делителя 9 частоты в устройстве формируется остаток по .модулю К от входного кода и определяется чис - ло единиц последовательного по тому же модулю. 1 з.п. ф-лы, 2 ил. § (Л

На фиг,1 изображена функциоггальная Q ниц двоичного кода по модулю К работает следующим образом.

В режиме формирования остатка . входного кода по модулю К на управляющий вход 1 (вход 17 делителя 9)

15 подан нулевой логический сигнал, на входы 10 подан входной код. По мере поступления тактовых импульсов с выхода генератора 1 на тактовый вход преоб,разователя 2 он на т-м информа20 ционном выходе (т 1,Р) формирует последовательность импульсов, число которых равно числу единичных логических сигналов на входах 0,т. Импульсы с первого информационного вы25 хода преобразователя 2 поступают через элемент ИЛИ 8.1 на счетный вход счетчика 5;по модулю К, который подсчитает их число. Импульсы (i+l)-ro выхода преобразователя 2 поступают

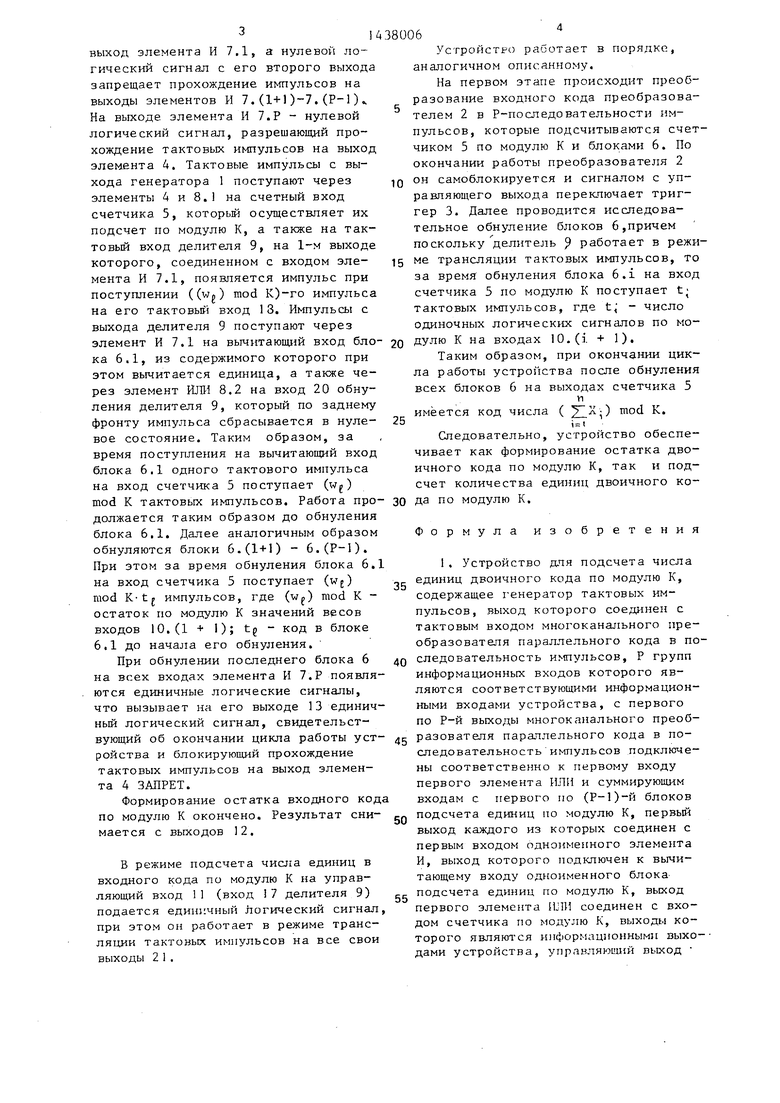

схема устройства; на фиг.2 - схема делителя частоты.

Устройство для подсчета числа единиц двоичного кода по модулю К содержит генератор 1 тактовых импульсов j многоканальный преобразователь 2 параллельного кода в последовательность импульсов, триггер 3, элемент ЗАПРЕТ 4, счетчик 5 по модулю К, блоки 6 подсчета единиц по модулю К,элементы И 7,элементы ИЛИ 8 и делитель 9 частоты. На фиг.1 обозначены также информационные 10 и управляющий 11 входы и .информационные- 12 и контрольный 13 выходы.

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть выполнен так же, как и в известном устройстве.

Входы 10 преобразователя 2 сгруппиро- 30 на суммирующий вход блока 6„1, котованы таким образом, что веса w всех разрядов одной группы входов, взятые по модулю К, одинаковы, а для первой группы входов равны 1.

Блок 6 подсчета единиц по модулю К может быть выполнен в виде реверсивного двоичного счетчика с коэффициентом пересчета К, суммирующий и вычитающи входы которого являются суммирующим и вычитающим входами блока 6, выходы счетчика соединены с входами элемента ИЛИ, прямой выход которого является первым, а инверсный выход - вторым выходами блока 6. Блок 6 может быть также выполнен в виде кольцевого реверсивного распределителя потенциалов (регистра сдвига) на К разрядов, входы сдвига вправо и влево которого являются суммирующим и вьмитающим входами блока 6j а выходы с второго по К-й разрядов соединены с входами элемента ЯЛИ,прямой и инверсный входы которого являются первым и.вторым входами блока- 6.

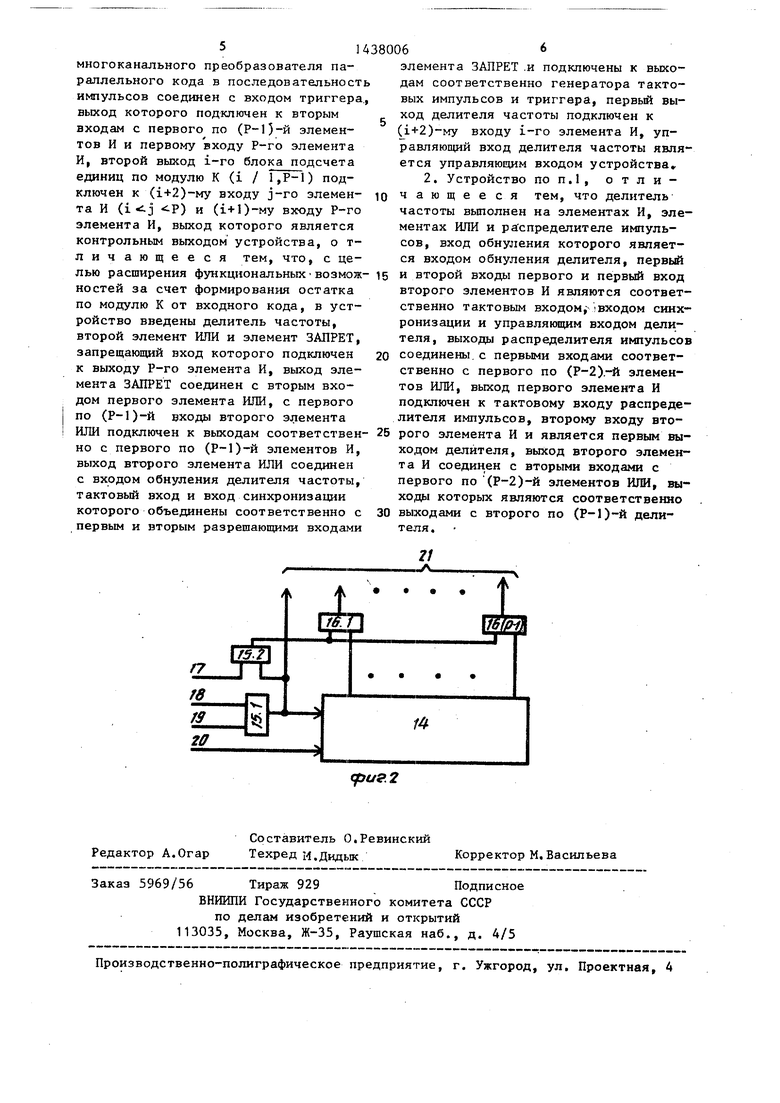

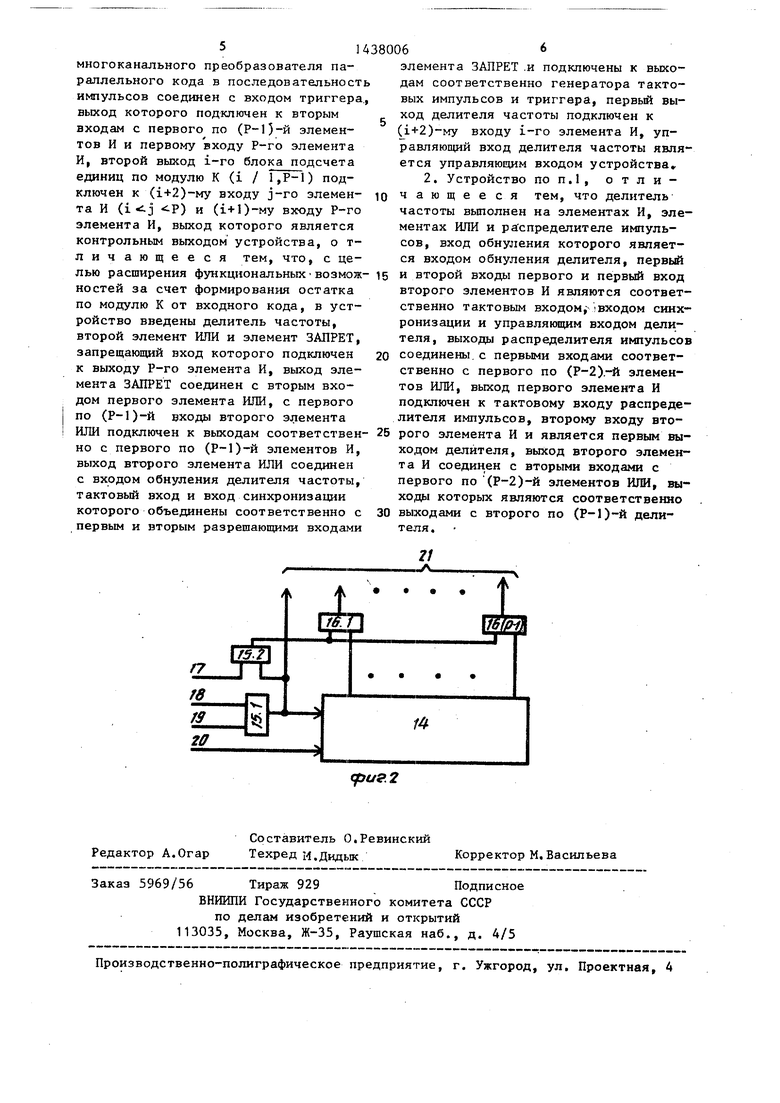

Делитель 9 частоты выполнен (фиг.2) на распределителе 14 импульсов, элементах И 15 и элементах ИЛИ 16. На фиг.2 обозначены также управляющий Г/ и тактовьм 18 входы, входд

5

5

0

5

рый осуществляет их подсчет по модулю К.

По окончании преобразования входного кода преобразователь 2 самоблокируется и далее импульсов на своих информационных выходах не формирует. При этом на .управляющем выходе (останова) преобразователя 2 формируется импульс, переключающий триггер 3, на выходе которого при этом, в паузе между тактовыми импульсами, появляется единичный логический сигнал,

В течение времени работы преобразователя 2 на выходе триггера 3 имеет место нулевой логический сигнал, запрещающий прохождение тактовых импульсов на выходы элемента ЗАПРЕТ и элементов И 7, а также блокирующий работу делителя 9.

После переключения триггера 3 начинается процесс обнуления блоков 6.

Пусть 6,1 - наименьший номер блока 6, в который записан ненулевой код (за время работы преобразователя 2 на его суммирующий вход поступило 1 импульсов, причем (1) raod К г 0), При этом единичньш сигнал с первого выхода блока 6,1 разрешает прохождение импульсов с выхода делителя 9 ня

выход элемента И 7.1, а нулевой логический сигнал с его второго выхода запрещает прохождение импульсов на выходы элементов И 7.(1+)-7.(Р-1) На выходе элемента И 7.Р - нулевой логический сигнал, разрешающий прохождение тактовых импульсов на выход элемента 4. Тактовые импульсы с выхода генератора 1 поступают через элементы 4 и 8. на счетный вход счетчика 5, который осуществляет их подсчет по модулю К, а также на тактовый вход делителя 9, на 1-м выходе которого, соединенном с входом элемента И 7.1, появляется импульс при поступлении ((wj) mod К)-го импульса на его тактовьй вход 13. Импульсы с выхода делителя 9 поступают через элемент И 7.1 на вычитающий вход блока 6,1, из содержимого которого при этом вычитается единица, а также через элемент ШМ 8.2 на вход 20 обнуления делителя 9, который по заднему фронту импульса сбрасывается в нулевое состояние. Таким образом, за время поступления на вычитающий вход блока 6,1 одного тактового импульса на вход счетчика 5 поступает (w) mod К тактовых импульсов. Работа продолжается таким образом до обнуления блока 6.1, Далее аналогичным образом обнуляются блоки 6.(1+1) - 6.(Р-1). При этом за время обнуления блока 6.1 на вход счетчика 5 поступает (wj) mod K-tj импульсов, где (wp) mod К - остаток по модулю К значений весов входов 10.(1 + 1); tg - код в блоке 6,1 до начала его обнуления.

При обнулении последнего блока 6 на всех входах элемента И 7.Р появляются единичные логические сигналы, что вызывает на его выходе 13 единичный логический сигнал, свидетельствующий об окончании цикла работы устройства и блокирующий прохождение тактовых импульсов на выход элемента 4 ЗАПРЕТ.

Формирование остатка входного код по модулю К окончено. Результат снимается с выходов 12.

В режиме подсчета числа единиц в входного кода по модулю К на управляющий вход 11 (вход 7 делителя 9) подается единичный логический сигнал при этом он работает в режиме транс- тактовых импульсов на все свои выходы 21.

6

З стройстрс) работает в порядке, аналогичном описанному.

На первом этапе происходит преобразование входного кода преобразователем 2 в Р-последовательности импульсов, которые подсчитываются счетчиком 5 по модулю К и блоками 6. По окончании работы преобразователя 2

он самоблокируется и сигналом с управляющего выхода переключает триггер 3. Далее проводится исследова- тельное обнуление блоков 6,причем поскольку делитель работает в режиме трансляции тактовых импульсов, то за время обнуления блока 6.1 на вход счетчика 5 по модулю К поступает t тактовых импульсов, где t, - число одиночных логических сигналов по модулю К на входах 10.(i. + 1).

Таким образом, при окончании цикла работы устройства после обнуления всех блоков 6 на выходах счетчика 5

25

имеется код числа ( 2I.X-) mod К.

Следовательно, устройство обеспечивает как формирование остатка двоичного кода по модулю К, так и подсчет количества единиц двоичного ко- да по модулю К.

Формула изобретения

единиц двоичного кода по модулю К, содержащее генератор тактовых импульсов, выход которого соединен с тактовым входом многоканального преобразователя параллельного кода в последовательность импульсов, Р групп информационных входов которого являются соответствующими информационными входами устройства, с первого по Р-й выходы многоканального преобразователя параллельного кода в последовательность импульсов подключены соответственно к первому входу первого элемента ИЛИ и суммирующим входам с первого но (Р-1)-й блоков

подсчета единиц по модулю К, первый выход каждого из которых соединен с первым входом одноиме1 ного элемента И, выход которого подключен к вычитающему входу одноименного блокаподсчета единиц по модулю К, выход первого элемента ИЛИ соединен с входом счетчика по модулю К, выходы которого являются информационными выхо- дами устройства, управляющий выход

многоканального преобразователя параллельного кода в последовательность импульсов соединен с входом триггера., выход которого подключен к вторым входам с первого по (Р-1)-й элементов И и первому входу Р-го элемента И, второй выход i-ro блока подсчета единиц по модулю К (1 / 1,Р-1) подключен к (i+2)-My входу j-ro элемента И (i i;i ) и (1+1)-му входу Р-го элемента И, выход которого является контрольным выходом устройства, о т- личающееся тем, что, с це10

элемента ЗАПРЕТ .и подключены к выходам соответственно генератора тактовых импульсов и триггера, первый выход делителя частоты подключен к (1+2)-му входу i-ro элемента И, управляющий вход делителя частоты является управляющим входом устройства 2. Устройство по П.1, отличающееся тем, что делитель частоты выполнен на элементах И, элементах ИЛИ и ра спределит еле импульсов, вход обнуления которого является входом обнуления делителя, первый

лью расширения функциональныхвозмож- 15 и второй входы первого и первый вход

ностей за счет формирования остатка по модулю К от входного кода, в устройство введены делитель частоты, второй элемент ИЛИ и элемент ЗАПРЕТ, запрещающий вход которого подключен к выходу Р-го элемента И, выход элемента ЗАШ ЕТ соединен с вторым входом первого элемента ИЛИ, с первого по (Р-1)-й входы второго элемента

второго элементов И являются соответственно тактовым входомjjвходом синхронизации и управляющим входом делителя, выходы распределителя импульсов 20 соединены,с первыми входами соответственно с первого по (Р-2).-й элементов ИЛИ, вькод первого элемента И подключен к тактовому входу распределителя импульсов, второму входу втоИЛИ подключен к выходам соответствен- 25 рого элемента И и является первым выно с первого по (Р-1)-й элементов И, выход второго элемента ИЛИ соединен с входом обнуления делителя частоты, тактовый вход и вход синхронизации

ходом делителя, выход второго элемен та И соединен с вторыми входами с первого по ()-й элементов ИЛИ, вы ходы которых являются соответственно

которого объединены соответственно с 30 выходами с второго по (Р-1)-й делипервым и вторым разрешающими входами

ф

gP

элемента ЗАПРЕТ .и подключены к выходам соответственно генератора тактовых импульсов и триггера, первый выход делителя частоты подключен к (1+2)-му входу i-ro элемента И, управляющий вход делителя частоты является управляющим входом устройства 2. Устройство по П.1, отличающееся тем, что делитель частоты выполнен на элементах И, элементах ИЛИ и ра спределит еле импульсов, вход обнуления которого является входом обнуления делителя, первый

второго элементов И являются соответственно тактовым входомjjвходом синхронизации и управляющим входом делителя, выходы распределителя импульсов соединены,с первыми входами соответственно с первого по (Р-2).-й элементов ИЛИ, вькод первого элемента И подключен к тактовому входу распределителя импульсов, второму входу втоходом делителя, выход второго элемента И соединен с вторыми входами с первого по ()-й элементов ИЛИ, выходы которых являются соответственно

теля.

21

1

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1986-12-02—Подача