11

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи и хранения цифровой информации.

Цель изобретения.- повышение на- дежности функционирования и достоверности выходной информации.

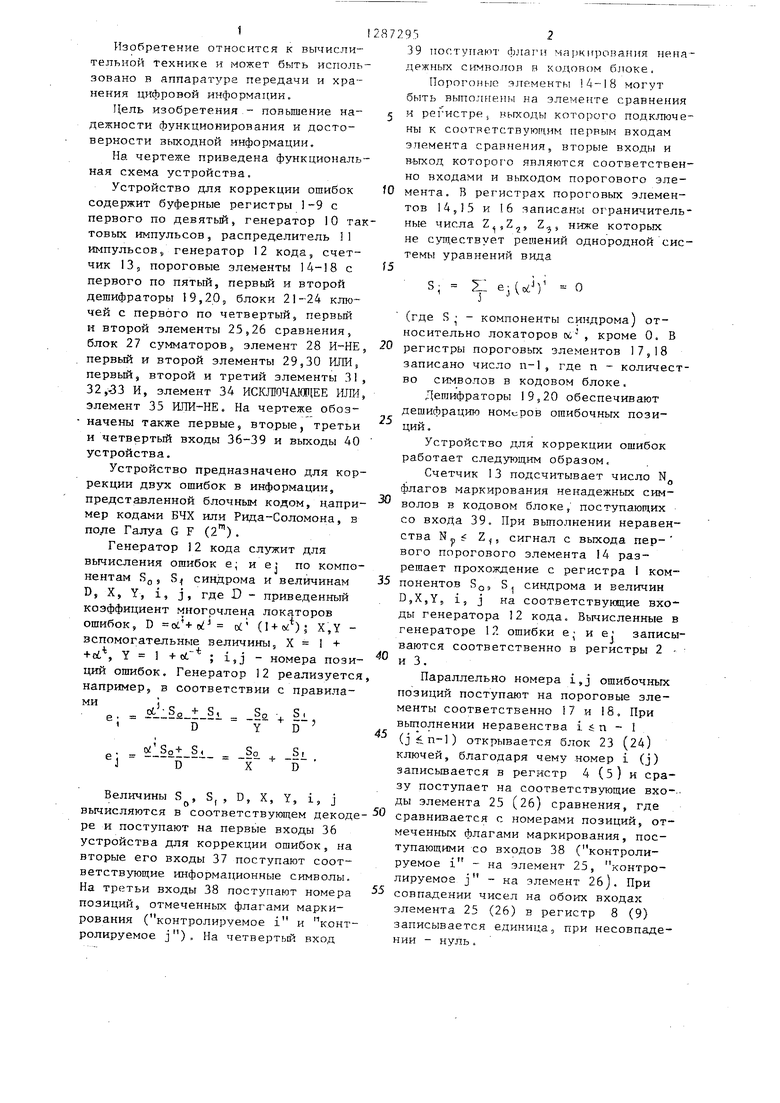

На чертеже приведена функциональная схема устройства.

Устройство для коррекции ошибок содержит буферные регистры 1-9 с первого по девятьА, генератор 10 тактовых импульсов, распределитель 1 импульсов, генератор 12 кода, счетчик 13э пороговые элементы 14-18 с первого по пятый, первьй и второй дешифраторы 19,20, блоки 21-24 ключей с первого по четвертый, первый и второй элементы 25,26 сравнения, блок 27 сумматоров, элемент 28 И-НЕ, первый и второй элементы 29,30 ИЛИ, первый, второй и третий элементы 31, 32,-33 И, элемент 34 ИСКЛОЧАКЩЕЕ ИЛИ, элемент 35 ИПИ-НЕ. На чертеже обозначены также первые, вторые, третьи и четвертый входы 36-39 и выходы 40 устройства.

Устройство предназначено для коррекции двух ошибок в информации, представленной блочным кодом, например кодами БЧХ или Рида-Соломона, в поле Галуа G F (2) .

Генератор 12 кода служит для вычисления ошибок е; и е: по компонентам Sg5 4 синдрома и величинам D, X, Y, i, j, где D - приведенный коэффициент многочлена локаторов ошибок, D oi +c :J сС (1 + х:); X,Y - вспомогательные величины, X + + й, Y 1 +06 ; i,j - номера пози- ций ошибок. Генератор 12 реализуется например, в соответствии с правила

.-

ми

or-So + S,

-So + Si. Y D

e;

5 1Soj; S So Sj D X D

Величины S, S,, D, X, Y, i, j вычисляются в соответствующем декоде ре и поступают на первые входы 36 устройства для коррекции ошибок, на вторые его входы 37 поступают соответствующие информационные символы. На третьи входы 38 поступают номера позиций, отмеченных флагами маркирования (контролируемое i и контролируемое j). На четвертый вход

39 поступают флаги марк1тро1 ания неня- дежньгк ctMBO.rioB в кодовом блоке.

Порогоные элементы 14-18 могут быть выполнен. на элементе сравнения и ре истре S вьгходь которого подключены к соответствующим первым входам элемента сравнения, вторые входы и в-ьгход которог о являются соответственно входами и выходом порогового элемента. В регистрах пороговых элементов 14,5 и 16 записаны ограничительные числа Zg, ниже которых не существует решений однородной системы уравнений вида

S, х: )i . о

fO , 20

35,

25

30

45

50

(где S - компоненты синдрома) относительно локаторов 00 , кроме 0. В регистры пороговых элементов 17,18 записано число п-1, где п - количество символов в кодовом блоке.

Дешифраторы 19,20 обеспечивают дешифрацию номеров ошибочных позиций.

Устройство для коррекции ошибок работает следующим образом.

Счетчик 13 подсчитывает число N флагов маркирования ненадежных символов в кодовом блоке, поступающих со входа 39. При выполнении неравенства Nр Z,5 сигнал с выхода пер- вого порогового элемента 14 разрешает прохождение с регистра 1 компонентов SQ, S, синдрома и величин D,X,Y, i, j на соответствующие входы генератора 12 кода. Вычисленные в генераторе 12 ошибки и е; записываются соответственно в регистры 2 и 3.

Параллельно номера i,j ошибочных позиций поступают на пороговые элементы соответственно 17 и 8, При выполнении неравенства i s п - 1 () открывается блок 23 (24) ключей, благодаря чему номер i (j) записьшается в регистр 4 (5) и сразу поступает на соответствующие вхо-.. ды элемента 25 (26) сравнения, где сравнивается с номерами позиций, отмеченных флагами маркирования, поступающими со входов 38 (контролируемое i - на элемент 25, контролируемое j - на элемент 26). При совпадении чисел на обоих входах элемента 25 (26) в регистр 8 (9) записывается единица, при несовпадении - нуль.

По окончании времени Гвремени прохождения информационны символов кодового блока) из распределителя II импульсов, тактируемого генератором 10, приходит первый считьшающий импульс на регистр 2, Ошибка е считывается из него на блок 2 ключей, на другой информационный вход которого дешифрируется номер позиции ошибки i из ре- гистра 4 в дешифраторе 19 только по разрешающему управляющему сигналу от элемента 31 , Этот сигнал вырабатьшается, если на оба выхода элемента 31 И поступают соответственно из регистров 8 и 9 (без считьтания) единицы как сигналы соответствующих совпадений. При этом ошибка е- и дешифрованный номер ее позиции (ад- рее проходит блок 21 ключей,после чего ошибка е суммируется в блоке 27 сумматоров с информацией, поступившей со входа 37, по дешифрированному адресу. Одновременно информация из регистра 5 переписьшается в регистр 6. По второму импульсу считывания от распределителя I1 считывается ошибка е; из регистра 3, а j - из регистра 6 с дешифрирование номера ее позиции (адреса) в дешифраторе 20 в случае разрешающей единицы с элемента 31 И, которая открывает для блок 22 ключей. В результате ошибка 6: суммируется в блоке 27 сумматоров с информацией, поступившей ранее со входа 37 в ви- де одового блока информационных символов, по адресу из дешифратора 20. Tpet-ий импульс от распределителя I 1 считьшает полученную информацию из блока 27 сумматоров в регистр 7, параллельно сбрасываются регистры 2,3 и 6.

Одновременно происходит анализ сигналов во вспомогательных устройствах Из регистров 8 и 9 сигналы поступают на элемент 34 ИСКЛЮ- ЧАМЦЕЕ ИЛИ и элемент 25 ИЛИ-НЕ. В случае прихода только одной едини- цы от регистров 8, 9 единицу на выход выдает только элемент 34. Эта единица поступает на вход элемента 32 И, на другой вход которого в случае необходимости маркирования ненадежных символов в предлагаемом устройстве поступает единица с выхода второго порогового элемента 5,

как результат сравнения числа Np, поступившего со счетчика 13, с огра ничительным числом 7.,по неравенств Npfr Z.. В этом случае на элемент 29 ИЛИ поступает единица с выхода элемента 32 И. В случае прихода от регистров 8 и 9 только нулей элемент 35 ИЛИ-НЕ в свою очередь посылает на элемент 30 ИЛ единицу. . На выходе элемента 30 ИЛИ единица появляется и в том случае, если на выходах пороговых элементов 17,18 появится хотя бы один нуль - признак невыполнения неравенства i,j и п-1,прн этом соединенный с ними элемент 28 И-НЕ выдает единицу на другой вход элемента 30 ИЛИ.

В обоих случаях элемент 30 ИЛИ выдает единицу на элемент 33 И, который пропускает этот сигнал маркирования на элемент 29 ИЛИ только в случае прихода единицы с выхода порогового элемента 6, если вьшол- няется неравенство для числа флагов предыдущего маркирования N-, поступающего со счетчика 13, и числа Z. Во всех этих случаях необходимости маркирования флагом элемент 29 ИЛИ пропускает сигнал маркирова- НИН единицу на второй информационный вход (вход указателя ошибок) регистра 7 и записывает ее там, как флаг маркирования ненадежных символо всего принятого кодового блока. После этого четвертьй импульс от распределителя 11 сбрасьшает информацию в счетчике 13, генераторе 12 код и в регистрах 4,5,8 и 9. Пятый импульс от распределителя 1I считывает информацию из регистра 7 на выходы 40 устройства, а шестой сбрасывает информацию из регистра 7 и блока 27 сумматоров. В результате устройство готово к обработке информации из следукнцего принимаеного кодового блока.

Таким образом, устройство обеспечивает коррекцию двух ошибок. Кроме того, благодаря тому, что отбраковка данных осуществляется на входе, устройство не работает от некорректи руемой информации, вследствие чего не работает вхолостую, не перегружается, характеризуется больш1-1М сроком службы, меньшим количеством сбоев и отказов, а следовательно, более высокой надежностью.

51

Формула изобретения

Устройство для коррекции ошибок, содержащее блок сумматорон, первый бу(Ъерный регистр, информационные входы которого являются соответствующими первьми входами устройства, первьш дешифратор, выходы которот о соединень с соответствующими первыми информационными входами первого блока ключей, отличающее - с я тем, чт о, с целью повьшшния надежности устройства и достоверности выходной информации, в него введены второй дешифратор, второй, третий и четвертый блоки ключей, генератор тактовых; импульсов, распределитель импульсов, пороговые элементы элементы И, элементы ИЛИ, элемент И-НЕ, элемент liJIH-HE, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы сравнения, буферные регистры с второго по девятый, генератор кода и счетчик, выходы которого подключены к соответ- ствукщим входам первого, второго и третьего пороговых элементов, выход первого порогового элемента соединен с управляющим входом первого буферного регистра, выходы которого с первого по пятый соедютены с соответствующими информационными входами генератора кода, первые и вторые выходы которого соединены с соответст- вугацими информационньии входами соответственно второго и третьего буферных: регистров, шестые выходы первого буферного регистра подключены к .соответствующим информационным входа генератора кода, информационным входам третьего блока ключей и входам четвертого порогового элемента, выход которого соединен с первым входом элемента И-НЕ и с управляющим входом блока ключей,, выходы которого соединены с соответствующими информационными входами четвертого буферного регистра, выходы ко- , торого подключены к соответствующиз-) лервым входам первого элемента сравнения и информационным входам первого дешифратора, седьмые выходы первого буферного регистра подключены к соответствующим информационным входам генератора кода, информационным входам четвертого блока ключей и входам пятого порогового элемента выход которого соединен с вторым входом элемента И-.ЧЕ и управляющим ВХОДОМ четвертого блока ключей, вы

0

ходы которог о соединены с сскггвет- c i ymmviMH информа 1ИО иыми лходв-ми пятого буферного регистра, вьгходы которого подключены к соответствующим парным лходам второго элемента срав- нення и информационньм входам лтесто- го буферного регистра 5 выходы которого подключены к соответствующим ин- формационньм входам второго дешифратора, выходы которого соединены с соответству ощш.1и первыми информационными входами второго блока ключей, выходы второго и третьего буферных регистров соединены с соответствую- 5 шими вторыми информационными входами соотБбтственно первого и второго блоков ключей, первые и вторые выхо- Д о1 которых соответственно объединены и подключены соответственно к адрес- иьм и первым информационным входам блока сумматоров, выходы которого соединень с соответствующими первыми информационными входами седьмого буферного регистра, выходы первого и второго элементов сравнения соеди- яви. с информационными входами соответственно восьмого и девятого буферных регистров, выходы которых подключены соответственно к первым и вто- ръш входам первог о элемента И, эле кер.:та ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента ИЛИ- Ш, выход первого элемента И подключен к управляющим входам дешифраторов и первого и второго блоков ключей, выходы элемента И-НЕ и элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы второго и третьего пороговых элементов подключены к первым входам соответствующих элементов И, выходы элемента ИСКЛЮЧАЮГЦЕЕ Ш1И и первого элемента ИЛИ подключены к вторым входам соответственно второго и третьего элементов И, выходы которых соединянь соответственно с первым и вторым входами второго элемента ИЛ15, выход которого подключен к второму информационному входу седьмого буферного регистра, выход генератора тактовых импульсов соединен с входом распределителя импульсов, первый выход которого подключен к входу считывания второго буферного рег ЕСТра, второй выход соединен с входами считьтания третьего и шестого буферных регистров, третий В1:1ход подключен к входу считывания блока сумматоров и входам сброса

0

5

0

5

0

55

7 12872958

второго, третьего и шестого буферныхрегистра и блока сумматоров, вто- регистров, четвертый выход распре-рые информационные входы которого делителя импульсов подключен к нхо-являются вторыми входами устройства, дам сброса счетчика, генератора кода,вторые входы элементов сравнения четвертого, пятого, восьмого и девя-5 являются третьими входами устройст- того буферных регистров, пятый выходва, вход счетчика является четвер- соединен с входом считьгоания седьмо-тым входом устройства, выходы седьмого -буферного регистра, шестой выход -го буферного регистра являются выхо- с входами сброса седьмого буферногодами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Устройство для формирования лексических массивов | 1980 |

|

SU934487A1 |

| Устройство для контроля телеметрической информации | 1980 |

|

SU920814A1 |

Изобретение относится к вычислительной технике. Его использование в аппарате передачи и хранения циф- рювой информации позволяет повысить надежность функционирования и достоверность выходной информации. Устройство содержит блок 27 суъматоров, буферньй регистр 1, дешифратор 19 и блок 21 ключей. Благодаря введению генератора 12 кода, второго дешифратора 205 трех блоков 22,24 ключей, восьми буферных регистров 2 - 9, счетчика 13, пяти пороговых ментов 14-18, двух элементов 25, 26 сравнения, трех элементов И 31 - 33, двух элементов ИЛИ 29, 30,элемента И-НЕ 28, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 34, элемента ИГИ-НЕ 35, генератора 0 тактовых импульсов и распределителя 11 импульсов обеспечивается возможность коррекции двух ошибок, причем уже на входе устройства осуш.ествляет- ся отбраковка некорректируемых ошибок, что повышает надежность работы устройства. j-ш. 57 39

| Патент CPIA № 4142174, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство декодирования сКОРРЕКциЕй ОшибОК | 1978 |

|

SU794728A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1984-08-10—Подача