1

Изобретение относится к вычислительной технике, может быть использовано в устройствах обнаружения и исправления одиночных и групповых ошибок при контроле хранения и передачи дискретной информации.

Известно устройство декодирования с коррекцией ошибок, содержащее регистр данных, выход которого подключен к входу формирователя контрольных разрядов и первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров первой и второй групп контрольных разрядов, ко вторым входам которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов 1.

Однако известное устройство сложно и имеет невысокую точность декодирования.

Цель изобретения - повышение точности декодирования и упрощение устройства.

Для этого в устройство декодирование с коррекцией ошибок, содержащее регистр данных, выход которого подключен к входу формирователя контрольных разрядов и первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров первой и второй групп

контрольных разрядов, ко вторым входам которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов, введены последовательно соединенные дешифратор обратной величины, блок умножения двух величин, дешифратор номера ошибочной позиции и блок вентилей, выход которого подключен ко второму входу блока сумматоров коррекции, при этом ко второму входу блока вентилей подключен выход сумматора первой группы контрольных разрядов, а выход сумматора второй группы контрольных разрядов подключен ко второму входу дешифратора номера ошибочной позиции.

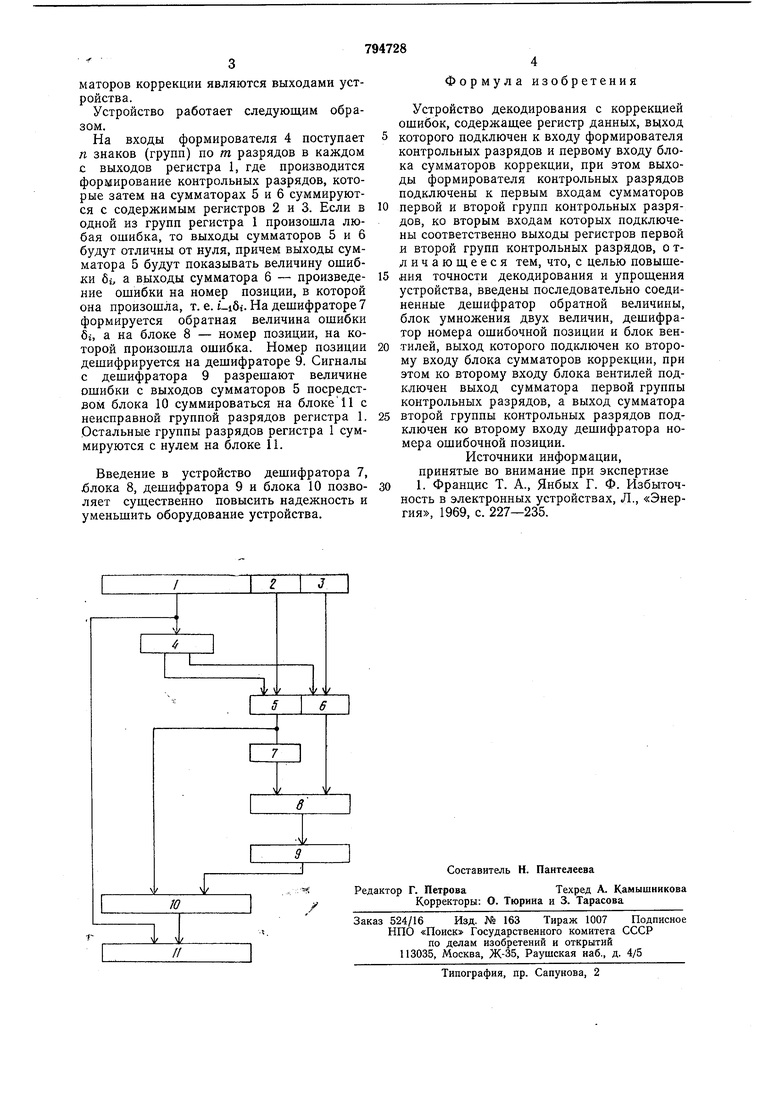

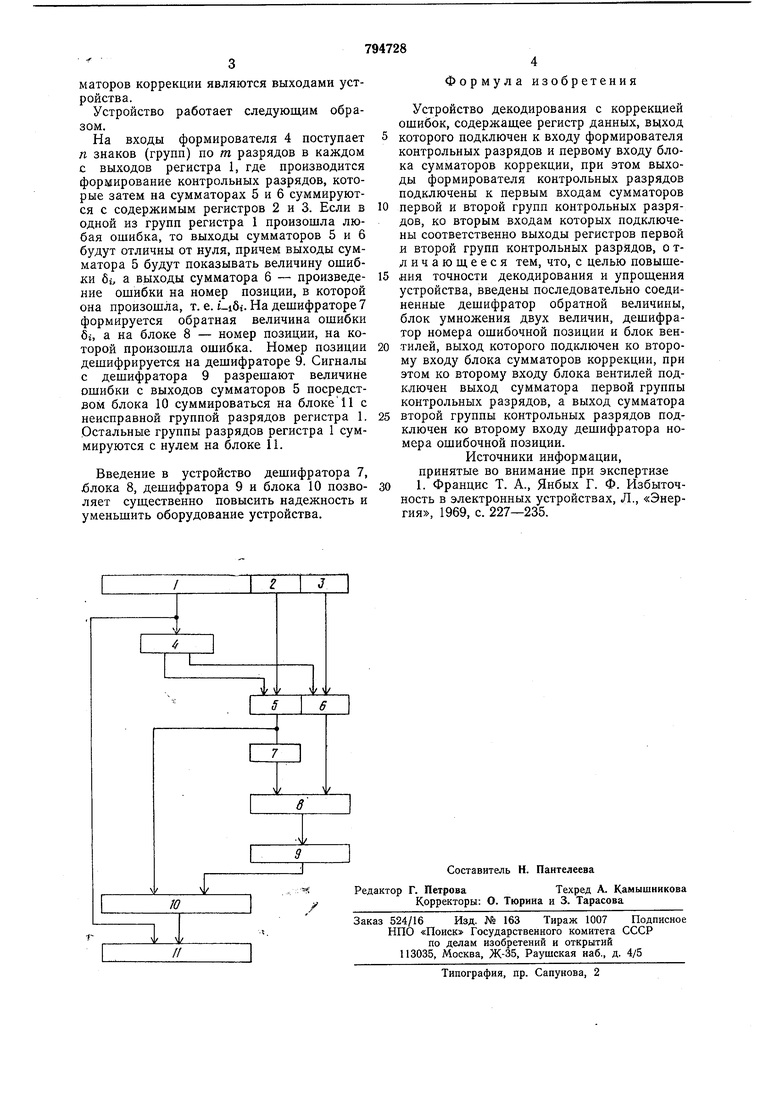

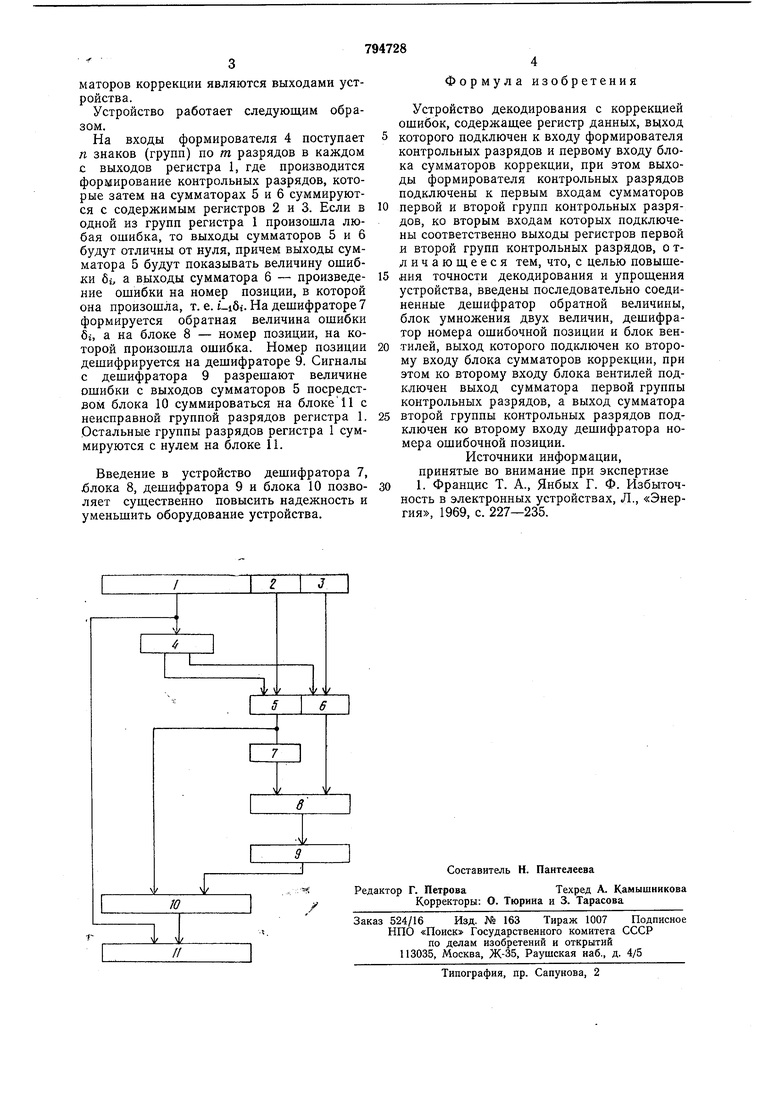

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит регистр 1 данных, регистр 2 первой группы контрольных разрядов, регистр 3 второй группы контрольных разрядов, формирователь 4 контрольных разрядов, сумматоры 5 первой группы

контрольных разрядов, сумматоры 6 второй группы контрольных разрядов, дешифратор 7 обратной величины, блок 8 умножения двух величин, дешифратор 9 номера ошибочной позиции, блок 10 вентилей и блок И

сумматоров коррекции. Выходы блока сумматоров коррекции являются выходами устройства.

Устройство работает следующим образом.

На входы формирователя 4 поступает п знаков (групп) по т разрядов в каждом с выходов регистра 1, где производится формирование контрольных разрядов, которые затем на сумматорах 5 и 6 суммируются с содержимым регистров 2 и 3. Если в одной из групп регистра 1 произошла любая ошибка, то выходы сумматоров 5 и 6 будут отличны от нуля, причем выходы сумматора 5 будут показывать величину ошибки бг. а выходы сумматора 6 - произведение ошибки на номер позиции, в которой она произошла, т. е. . На дешифраторе 7 формируется обратная величина ошибки бг, а на блоке 8 - номер позиции, на которой произошла ошибка. Номер позиции дешифрируется на дешифраторе 9. Сигналы с дешифратора 9 разрешают величине ошибки с выходов сумматоров 5 посредством блока 10 суммироваться на блоке11 с неисправной группой разрядов регистра 1. Остальные группы разрядов регистра 1 суммируются с нулем на блоке 11.

Введение в устройство дешифратора 7, 1лока 8, дешифратора 9 и блока 10 позволяет существенно повысить надежность и уменьшить оборудование устройства.

Формула изобретения

Устройство декодирования с коррекцией ошибок, содержащее регистр данных, выход

которого подключен к входу формирователя контрольных разрядов и первому входу блока сумматоров коррекции, при этом выходы формирователя контрольных разрядов подключены к первым входам сумматоров

первой и второй групп контрольных разрядов, ко вторым входам которых подключены соответственно выходы регистров первой и второй групп контрольных разрядов, о тличающееся тем, что, с целью повышения точности декодирования и упрощения устройства, введены последовательно соединенные дешифратор обратной величины, блок умножения двух величин, дешифратор номера ошибочной позиции и блок вентилей, выход которого подключен ко второму входу блока сумматоров коррекции, при этом ко второму входу блока вентилей подключен выход сумматора первой группы контрольных разрядов, а выход сумматора

второй группы контрольных разрядов подключен ко второму входу дешифратора номера ошибочной позиции.

Источники информации, принятые во внимание при экспертизе

1. Францис Т. А., Янбых Г. Ф. Избыточность в электронных устройствах. Л., «Энергия, 1969, с. 227-235.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с исправ-лЕНиЕМ ОшибОК | 1979 |

|

SU841059A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

W 1

S. I

f

JuL.

Авторы

Даты

1981-01-07—Публикация

1978-10-23—Подача