t1

Изобретение относится к области вычислительной техники и может быть использовано при создании на базе ЦВМ измерительного комплекса для измерения характеристик аналого-циф- ровых преобразователей (АЦП).

Цель изобретения - расширение функциональных возможностей путем определения и статистических составляющих АЦП.

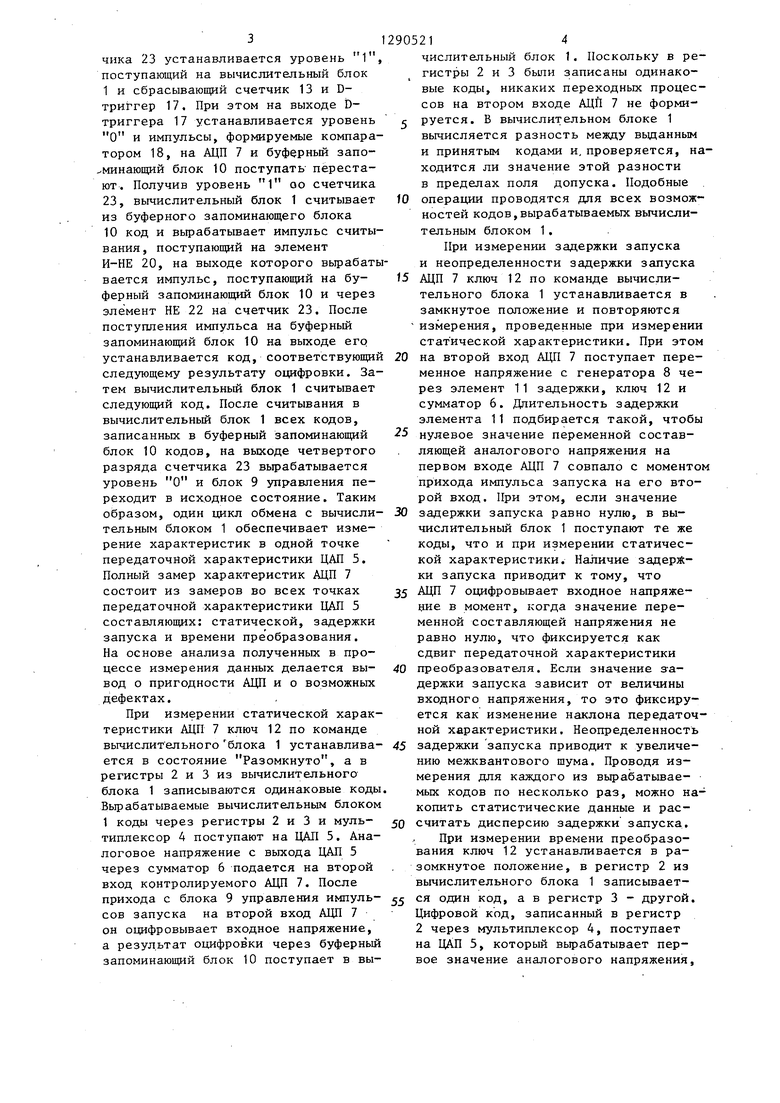

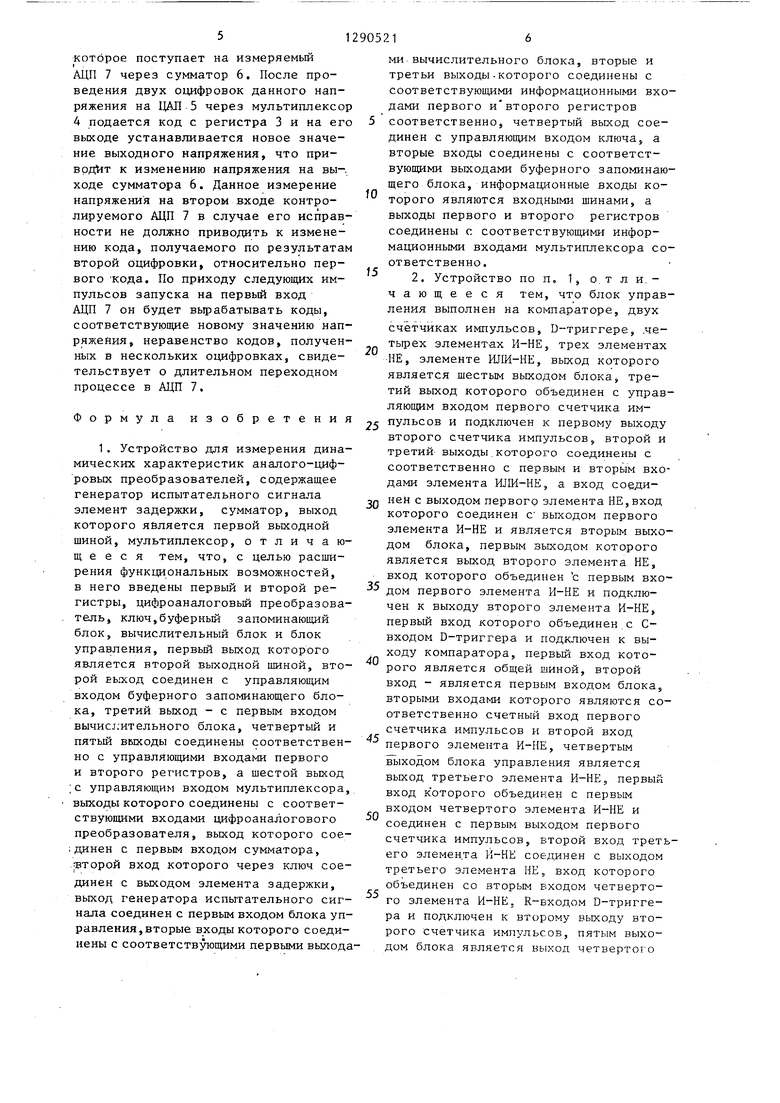

На фиг. 1 представлена схема устройства для измерения динамических характеристик АЦП на фиг. 2 - функциональная схема блока управл ения.

Устройство содержит вычислитель- ный блок 1, регистры 2 и 3, мультиплексор 4, цифроаналоговьй преобра- зователь (ЦАП) 5, сумматор 6, контролируемый АЦП 7, генератор .8 испытательного сигнала, блок 9 управле- НИН, буферный запоминающий блок 10, элемент 11 задерл ки и ключ 12.

Блок 9 управления состоит из счетчика 13 импульсов, элементов И-НЕ 14 и 15, элемента НЕ 16,В-триг- гера 17, компаратора 18, элементов И-НЕ 19 и 20, элементов НЕ 21 и 22, счетчика 23 импульсов и элемента 24,

Устройство работает следующим образом.

Работа устройства основана на формировании изменяющегося напряжени на первом входе АЦП 7 (амплитуда за- дается программным способом вычислительным блоком 1) и записи результатов оцифровки этого напряжения в буферный запоминаюощй блок 10, Быстродействие ЦВМ определяет время, не- обходимое для записи данных об амплитуде и,ьхарактере изменения напряжения в регистры 2 и 3 устройства и считывания результатов оцифровки из буферного запоминающего блока 10; время, необходимое для математической обработки результатов измерения, не влияет на дд5намические параметры устройства, определяющие предельную частоту дискретизации „, которую может задавать устройство на втором входе АЦП 7. Благодаря этому, в качестве вычислительного блока 1 можно использовать любую серийно выпускаемую вычислительную машину,

Процесс измерения складывается из циклов обмена с вычислительным блоком 1, заключающихся в следующем.

O

-5 0

5

0

5 О 0 5

12

Вычислительный блок 1 вырабатывает два кода, допровождаемые импульсами записи, причем по первому импульсу записи вырабатывается перепад напряжения на выходе элемента И-НЕ 15, по которому происходит запись первого кода в регистр 2. С выхода регистра

2через мультиплексор 4 первьш код поступает на вход ЦАП 5, на выходе которого устанавливается напряжение, соответствующее первому коду. С выхода ЦАП 5 через сумматор 6 это напряжение поступает на вход контролируемого АЦП 7. По второму импульсу записи вырабатывается перепад напряжения на выходе элемента И-НЕ 14, по которому происходит запись второго кода в регистр 3 и переход D-тригге- ра 17 из режима работы по установочному входу в режим работы по информационному входу. После этого первый же импульс, формируемый компарат.ором 18 из выходного напряжения генератора 8 приводит к появлению на выходе D-триггера 17 уровня 1, в результате импульсы, формируемые компаратором 18, проходят через элемент И-НЕ 19 элемент НЕ 21 и поступают на первьм ; вход контролируемого АЦП 7, а через элемент И-НЕ 20 поступает на буферный запоминающий блок 10, По каждому из импульсов в буферньй запоминающий блок 10 записывается вькодной код

АЦП 7, D-триггер 17 служит для исключения укороченного по длительности импульса, которьй может возникнуть на выходе элемента И-НЕ 19 из-за асинхронности работы генератора 8 и вычислительного блока 1, С выхода элемента И-НЕ 20 импульсы через элемент НЕ 22 поступают на счетчик 23, которьй после прих-ода второго импульса изменяет состояние элемента ИЛИ-НЕ 24, что приводит к переключению мультиплексора 4 таким образом, что на вход ЦАП 5 поступает код, записанный в регистр 3. Если коды, записанные в регистр 2 и в регистр 3, неодинаковы, то выходное напряжение ЦАП 5 и сумматора 6 изменяется и к моменту прихода очередного импульса запуска на первый вход АЦП 7 устанавливается новое значение этого напряжения. Затем АЦП 7 оцифровывает входное напряжение в шесть раз, после чего буферный запоминающий блок 10 оказывается заполненным, а на выходе четвертого разряда счетчнка 23 устанавливается уровень 1 поступающий на вычислительный блок 1 и сбрасывающий счетчик 13 и D- триГтер 17. При этом на выходе Ь- триггера 17 устанавливается уровень О и импульсы, формируемые компаратором 18, на АЦП 7 и буферный запо- минающий блок 10 поступать перестают. Получив уровень 1 оо счетчика 23, вычислительный блок 1 считывает из буферного запоминающего блока 10 код и вырабатывает импульс считывания , поступающий на элемент И-НЕ 20, на выходе которого вьфабат вается импульс, поступающий на буферный запоминающий блок 10 и через элемент НЕ 22 на счетчик 23. После поступления импульса на буферный запоминающий блок 10 на вьгходе его устанавливается код, соответствующи следующему результату оцифровки. Затем вычислительный блок 1 считывает следующий код. После считывания в вычислительный блок 1 всех кодов, записанных в буферный запоминающий блок 10 кодов, на выходе четвертого разряда счетчика 23 вырабатывается уровень О и блок 9 управления переходит в исходное состояние. Таким образом, один цикл обмена с вычислительным блоком 1 обеспечивает измерение характеристик в одной точке передаточной характеристики ЦАП 5. Полный замер характеристик АЦП 7 состоит из замеров во всех точках передаточной характеристики ЦАП 5 составляющих: статической, задержки запуска и времени преобразования. На основе анализа полученных в процессе измерения данных делается вывод о пригодности АЩ1 и о возможных дефектах.

При измерении статической характеристики АЦП 7 ключ 12 по команде вычислительного блока 1 устанавливается в состояние Разомкнуто, а в регистры 2 и 3 из вычислительного блока 1 записываются одинаковые коды Вырабатываемые вычислительным блоком 1 коды через регистры 2 и 3 и мультиплексор 4 поступают на ЦАП 5. Аналоговое напряжение с выхода ЦАП 5 через сумматор 6 подается на второй вход контролируемого АЦП 7. После прихода с блока 9 управления импульсов запуска на второй вход АЦП 7 он оцифровывает входное напряжение, а результат оцифровки через буферный запоминающий блок 10 поступает в вычислительный блок 1. Поскольку в регистры 2 и 3 бьши записаны одинаковые коды, никаких переходных процессов на втором входе АЦП 7 не форми- с руется. В вычислительном блоке 1 вычисляется разность между выданным и принятым кодами и, проверяется, находится ли значение этой разности в пределах поля допуска. Подобные 10 операции проводятся для всех возмож ностей кодов,вырабатываемых вычислительным блоком 1 . .

При измерении задержки запуска и неопределенности задержки запуска 15 АЦП 7 ключ 12 по команде вычислительного блока 1 устанавливается в замкнутое положение и повторяются измерения, проведенные при измерении статической характеристики. При этом 0 на второй вход АЦП 7 поступает переменное напряжение с генератора 8 через элемент 11 задержки, ключ 12 и сумматор 6. Длительность задержки элемента 11 подбирается такой, чтобы 5 нулевое значение переменной составляющей аналогового напряжения на первом входе АЦП 7 совпало с моментом прихода импульса запуска на его второй вход. При этом, если значение 0 задержки запуска равно нулю, в вычислительный блок 1 поступают те же коды, что и при измерении статической характеристики. Наличие задержки запуска приводит к тому, что 5 АЦП 7 оцифровывает входное напряжение в момент, когда значение переменной составляющей напряжения не равно нулю, что фиксируется как сдвиг передаточной характеристики 0 преобразователя. Если значение З а- держки запуска зависит от величины входного напряжения, то это фиксируется как изменение наклона п.ередаточ- ной характеристики. Неопределенность 5 задержки запуска приводит к увеличению межквантового шума. Проводя измерения для каждого из вырабатываемых кодов по несколько раз, можно накопить статистические данные и рас- 0 считать дисперсию задержки запуска. При измерении времени преобразования ключ 12 устанавливается в разомкнутое положение, в регистр 2 из вычислительного блока 1 записывает- 5 ся один код, а в регистр 3 - другой. Цифровой код, записанный в регистр 2 через мультиплексор 4, поступает на ЦАП 5, который вырабатывает первое значение аналогового напряжения.

которое поступает на измеряемый АЦП 7 через сумматор 6, После проведения двух оцифровок данного напряжения на ЦАП 5 через мультиплексор 4 подается код с регистра 3 и на его выходе устанавливается новое значение выходного напряжения, что при- к изменению напряжения на вы-, ходе сумматора 6. Данное измерение напряжения на втором входе контролируемого АЦП 7 в случае его исправности не должно приводить к изменению кода, получаемого по результатам второй оцифровки, относительно первого кода. По приходу следующих импульсов запуска на первый вход АЦП 7 он будет вырабатывать коды, соответствующие новому значению напряжения, неравенство кодов, полученных в нескольких оцифровках, свидетельствует о длительном переходном процессе в АЦП 7,

Формула изобретения

1. Устройство для измерения динамических характеристик аналого-цифровых преобразователей, содержащее генератор испытательного сигнала элемент задержки, сумматор, выход которого яЁляется первой выходной шиной, мультиплексор, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены первый и второй регистры, цифроаналоговый преобразователь, ключ,буферньм запоминающий блок, вычислительный блок и блок управления, первый выход которого является второй выходной шиной, второй Еьжод соединен с управляющим входом буферного запоминающего блока, третий выход - с первым входом вычис1;ительного блока, четвертый и пятый вБгкоды соединены соответственно с управляющими входами первого и второго регистров, а шестой выход ;с управляющим входом мультиплексора выходы которого соединены с соответствующими входами цифроаналогового преобразователя, выход которого сое iдинен с первым входом сумматора, шторой вход которого через ключ соединен с выходом элемента задержки, выход генератора испытательного сигнала соединен с первым входом блока управления, вторые входы которого соединены с соответствующими первыми выход

5

0

5

ми вычислительного блока, вторые и третьи выходы-которого соединены с соответствуюшдми информационными входами первого и второго регистров соответственно, четвертый выход соединен с управляющим входом ключа, а вторые входы соединены с соответствующими выходами буферного запоминающего блока, информационные входы которого являются входными шинами, а выходы первого и второго регистров соединены с соответствующими информационными входами мультиплексора соответственно,

2. Устройство по п. 1, о, т л и.- чающееся тем, что блок управления выполнен на KoivtnapaTope, двух

счетчиках импульсов, В триггере, .четырех элементах И-НЕ, трех элементах НЕ, элементе Ш1И-НЕ, выход которого является шестым выходом блока, третий выход которого объединен с управляющим входом первого счетчика импульсов и подключен к первому выходу второго счетчика импульсов, второй и третий выходы.которого соединены с соответственно с первым и вторым входами элемента ИЛИ-НЕ, а вход соединен с выходом первого элемента НЕ, вход которого соединен с выходом первого элемента И-НЕ и является вторым выходом блока, первым выходом которого является выход второго элемента НЕ, вход которого объединен с первым входом первого элемента И-НЕ и подключен к выходу второго элемента И-НЕ, первый вход которого объединен.с С- входом D-триггера и подключен к выходу компаратора, первый вход которого является общей шиной, второй вход - является первым входом блока, вторыми входами которого являются соответственно счетный вход первого Счетчика импульсов и второй вход первого элемента И-НЕ, четвертым выходом блока управления является выход третьего элемента И-НЕ, первый вход к оторого объединен с первым входом четвертого элемента И-НЕ и соединен с первым выходом первого счетчика импульсов, второй вход третьего элемента И-НЕ соединен с выходом третьего элемента НЕ, вход которого объединен со вторьгм входом четвертого элемента И-НЕ. R-входом D-триггера и подключен к второму выходу второго счетчика импульсов, пятым выходом блока является выход четвертого

0

5

0

5

0

5

- 1 12905218

элемента H-IIE, S- и D-входы D-триг- динен с вторым входом второго элемен- гера являются шиной 1, а выход сое- та И-НЕ.

Редактор Л.Пчолинская

Составитель И.Романова

Техред И.Попович Корректор А.Тяско

7У16/57

Тираж 922Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

6x01 2 9 импу/ { ср/ считывания

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь информации | 1986 |

|

SU1322476A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2012036C1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| ТЕЛЕВИЗИОННАЯ ЦИФРОВАЯ СИСТЕМА ДЛЯ ДИАГНОСТИКИ ПАРАМЕТРОВ ПУЧКОВ | 1989 |

|

SU1732781A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

Изобретение относится к области вьгаислительной техники и может быть использовано при создании на базе ЦВМ измерительного комплекса для измерения характеристик аналого- цифровых преобразователей. Изобретение позволяет расширить функщюналь- ные возможности устройства, содержащего генератор 8 испытатедьного сигнала, злемент 11 задержки, сумматор 6, мультиплексор 4 за счет введения в него первого 2 и второго 3 регистров, цифроаналогового -преобразователя 5, буферного запоминающего блока 10, блока 9 управления, ключа 12 и вычислительного блока 1. 1 з.п. ф-лы, 2 ил. О) С

| Способ измерения динамическихХАРАКТЕРиСТиК АНАлОгО-цифРОВыХ пРЕ-ОбРАзОВАТЕлЕй | 1979 |

|

SU809548A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для автоматического измерения характеристики преобразования быстродействующих аналого-цифровых преобразователей | 1982 |

|

SU1058048A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1984-10-03—Подача