Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.

Известно устройство для деления на константу типа 2-1, содержащее сумматор, регистр делимого, элемент-НЕ, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, две группы элементов И, промежуточный регистр и элемент И,

Недостатком устройства являются ограниченные функциональные возможности.

Известно устройство для деления на константу типа 2+1, выбранное в качестве прототипа и содержащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИНЕ, элементы НЕ группы, элементы И группы, причем л-разрядный информационный вход регистра делимого является входом делимого устройства, а выходы п разрядов регистра делимого соединены с соответствующими входами первой группы входов сумматора, входы с (п-1+2)-го по n-й второй группы входов сумматора и вход переноса сумматора соединены с единичной шиной, I младших выходов сумматора соединены с первыми входами соответствующих элементов И группы, выходы которых и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами остатка устройства, вход сброса промежуточного регистра обьединен со входом установки счетчика и синхровходом реXI

Ю

со

GO

гистра делимого и является входом запуска устройства, синхровход промежуточного регистра объединен с вычитающим входом счетчика и является тактовым входом устройства, выходы промежуточного регистра соединены с соответствующими входами элементов НЕ группы, выходы которых соединены с соответствующими входами второй группы уходов сумматора, выходы +1, +2, .... сумматора являются выходами частного устройства и соединены с информационными входами промежуточного регистра, выход +1 сумматора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход промежуточного регистра соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого.соединен с первым входом элемента И-НЕ, первый выход сумматора соединен со вторым входом элемента l/l-НЕ, выход которого соединен со входом разрешения приема промежуточного регистра, а также со вторыми входами элементов И группы, выход счетчика соединен со входом разрешения счета счетчика, а также с третьим входом элемента И-НЕ (инверсным).

Недостатком устройства являются ограниченные функциональные возможности, обусловленные невозможностью его работы в двоично-десятичной систе.ме счисления,

Целью изобретения является расширение области применения устройства.

Цель достигается тем, что в устройство для деления на константу типа 2 +1, содержащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элементы НЕ групяы, элементы И группы, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, выходы разрядов которого соединены с первой группой входов сумматора, вход переноса которого подключен к единичной шине, информационные входы промежуточного регистра объединены с соответствующими выходами частного результата устройства, а выходы промежуточного регистра подключены ко входам соответствующих элементов НЕ группы, выход первого разряда сумматора и информационный вход первого разряда промежуточного регистра соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом старшего разряда остатка устройства и соединен с первым прямым входом элемента И-НЕ, второй прямой вход которого объединен с первым входом первого элемента И группы, а выход элемента И-НЕ соединен со входом разрешения приема промежуточного регистра и вторыми входами элементов И группы, вход

запуска устройства соединен с входом сброса промежуточного регистра, с синхровхо- дом регистра делимого и входом установки счетчика, синхровход которого соединен с синхровходом промежуточного регистра и с

0 тактовым входом устройства, инверсный выход заема счетчика соединен с входом разрешения счета счетчика и инверсным входом элемента И-НЕ, выход элемента И группы является выходами младших разря5 дов остатка результата устройства, введены узел преобразования и делитель на 2 , причем входы узлы преобразования подключены к выходам соответствующих элементов НЕ группы, а выходы - к соответствующим

0 входам второй группы входов сумматора, выходы которого подключены к соответствующим входам делителя на 21, выходы частного которого являются выходами частного результата устройства, а выходы остатка со5 единены с первыми входами элементов И группы.

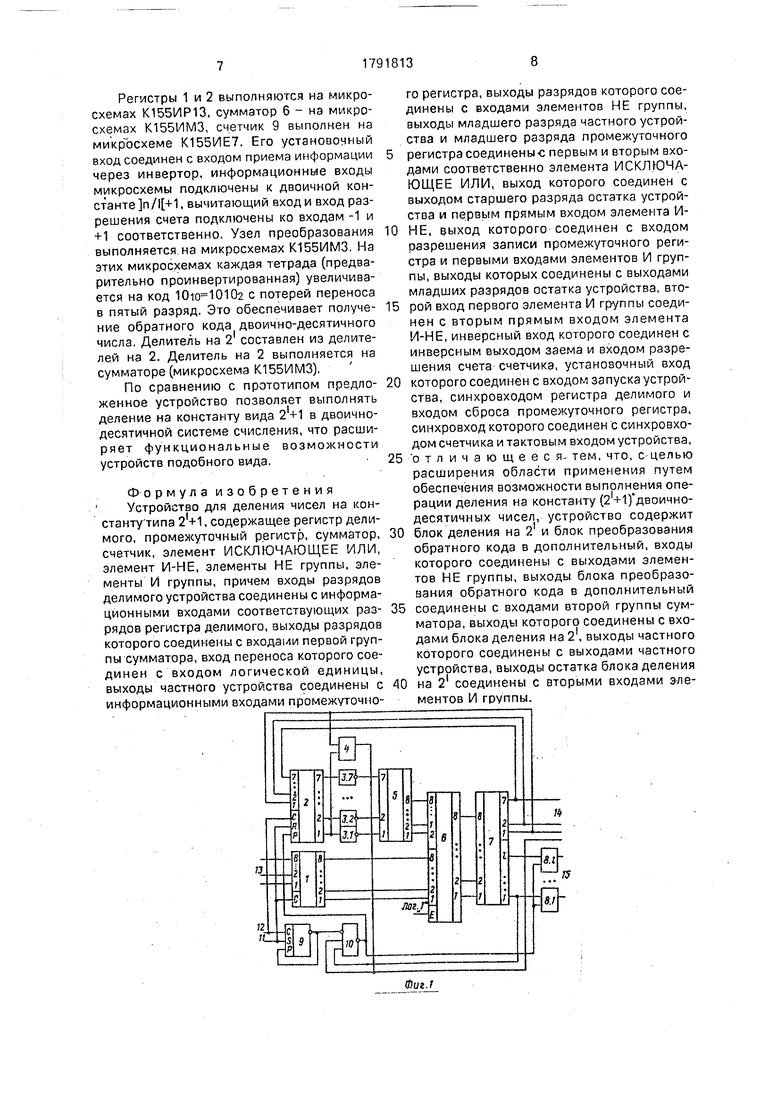

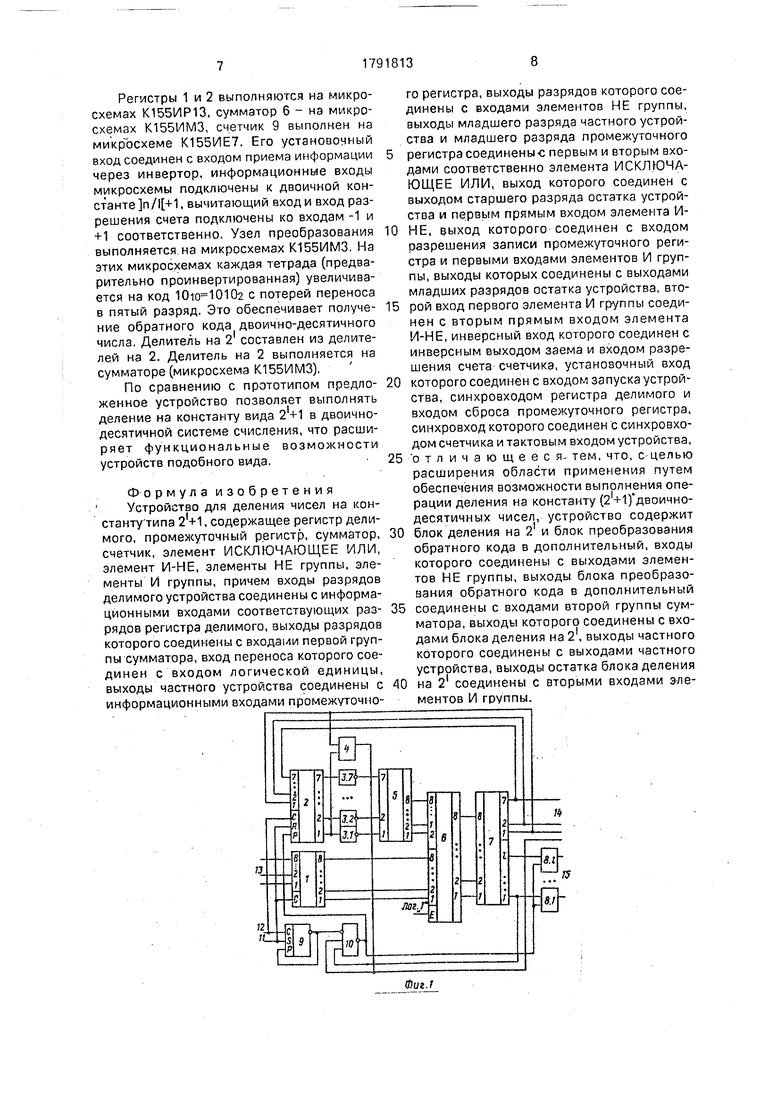

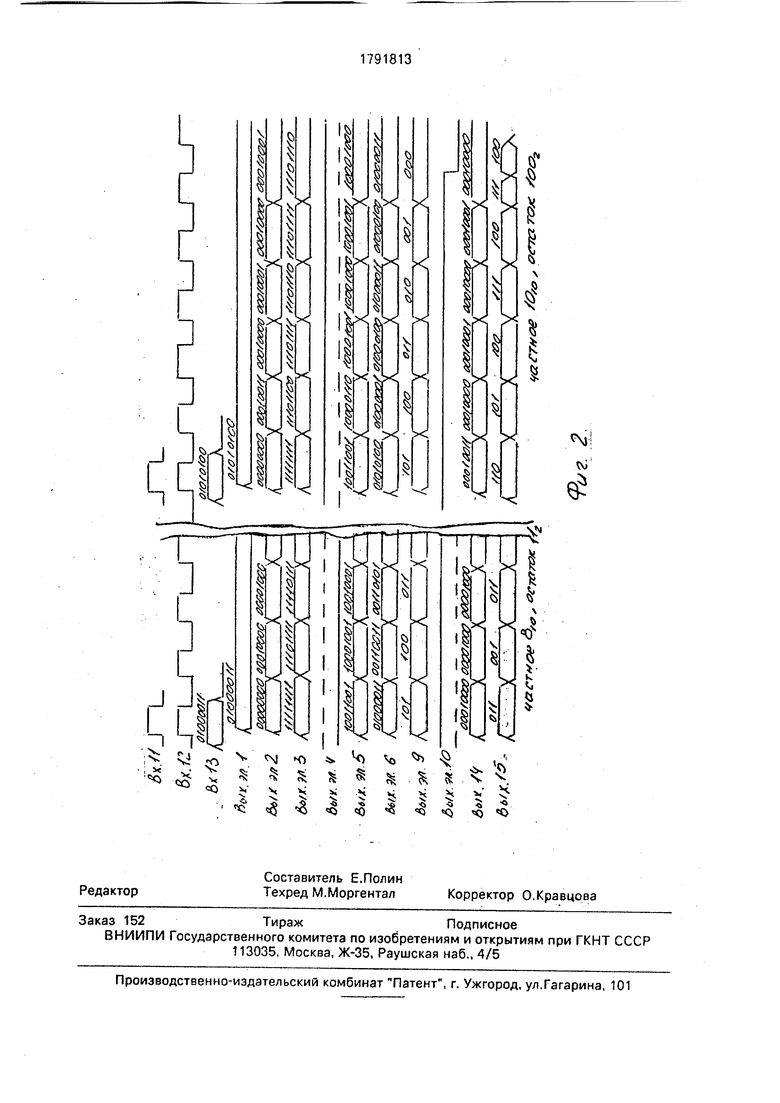

На чертеже показана схема устройства для случая двухтетрадного делимого; на фиг, 2 - временные диаграммы, иллюстри0 рующие работу устройства.

Устройство содержит регистр делимого 1, промежуточный регистр 2, элементы НЕ 3.1-3.7 группы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ А, узел преобразования 5, сумматор 6,

5 делитель на 21 7, элементы И 8.1-8. группы, счетчик 9, элемент И-НЕ 10, причем вход 11 запуска устройства подключен к входу сброса промежуточного регистра 2, синхровходу регистра делимого 1 и входу установки счет0 чика 9, синхровход которого соединен с синхровходом промежуточного регистра 2 и является тактовым входом 12 устройства, входы 13 делимого устройства соединены с информационными входами соответствую5 щих разрядов регистра делимого 1, выходы разрядов которого соединены с соответствующими входами первой группы входов сумматора 6, вход переноса которого подключен к единичной шине, а входы второй группы

0 входов подключены к соответствующим выходам узла преобразования 5, входы которого соединены с выходами соответствующих элементов НЕ группы 3, входы которых подключены к выходам соответствующих разрядов про5 межуточного регистра 2, информационные входы разрядов которого соединены соответственно с выходами частного делителя на 21 7 и являются выходами 14 частного результата устройства, выходы разрядов сумматора 6 соединены с соответствующими входами

делителя на 2 7, выходы остатка которого соединены с первыми входами соответствующих элементов И группы 8, выходы которых являются выходами 15 остатка результата устройства, выход младшего разряда промежуточного регистра 2 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, второй вход которого соединен с информационным входом младшего разряда промежуточного регистра 2, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен с выходом старшего разряда остатка результата устройства 15 и с первым прямым входом элемента И-НЕ 10, второй прямой вход которого соединен с первым входом первого элемента И группы 8, инверсный выход заема счетчика 9 подключен к входу разрешения счета счетчика 9 и к инверсному входу элемента И-НЕ 10, выход которого соединен со входом разрешения приема промежуточного регистра 2 и вторыми входами элементов И группы 8.

Устройство работает следующим образом.

На вход 13 устройства поступает делимое - двоично-десятичное число А (двухтет- радное). Это число записывается в регистр делимого 1 по сигналу, поступающему на синхровход этого регистра через вход. 11 устройства. Одновременно этот сигнал приходит на вход сброса промежуточного регистра 2, устанавливая его в нулевое состояние, а также на вход установки счетчика 9.

Получение исходного частного X можно описать уравнением

А/(2 +1)Х Х+Х.

Из этого следует, что частное X совпадает с делимым, поделенным на 21, и при этом имеет место погрешность, определяемая значением X и также выражаемая через делимое А, Погрешность учитывается на сумматоре 6 путем вычитания в дополнительном коде из делимого А результата этого вычитания, деленного на 2, а также синхронизации этой операции с использованием промежуточного регистра 2. Для этого число А с выходов регистра делимого 1 подается на первую группу входов сумматора 6, являющегося двоично-десятичным сумматором. Код с выходов сумматора 6 поступает на входы делителя на 2, выполняющего целочисленное деление и формирующего на выходах код частного Х1 и код остатка Х2. Код частного Х1 далее поступает на информационные входы промежуточного регистра 2,

прием в который осуществляется по синхроимпульсам, поступающим с тактового входа 12 устройства. Эти же синхроимпульсы поступают на счетный вход счетчика 9 для под5 счета тактов работы устройства. С выходов промежуточного регистра 2 код частного поступает на входы соответствующих его разрядам элементов НЕ группы 3, с выходов которых в инверсном значении подается на

10 входы узла преобразования 5. Этот узел завершает преобразование двоично-десятичного числа -Х1 в обратный код, начатое группой 3 элементов НЕ. Полученный обратный код поступает на вторую группу входов

15 сумматора 6, на вход переноса которого подается уровень лог.1 с единичной шины, что обеспечивает выполнение операции в дополнительном коде. При значении остатка, меньшем I, процесс вычисления завер20 шается не более, чем ,за тактов. Промежуточный регистр 2 подтверждает на выходах значение кода Х1 частного. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, сравнивающий младший разряд кода Х1 на соседних

5 тактах, принимает нулевое значение, поступающее на выход 15 устройства в качестве старшего (1+1)-го разряда остатка Х2, а также на вход элемента И-НЕ (Х разрешающе- го единичным значением прохождение ,f

0 младших разрядов кода Х2 через группу 8 элементов И на выходы 15 устройства. При значении остатка, равном I, на выходах сумматора б через тактов генерируется последовательность двух значений: с недо5 статком - искомая величина кода Х1 и составленные из единиц I младших разрядов кода Х2 с избытком - код Х1 + 1 и нулевые младшие разряды кода Х2. Счетчик 9 отсчитывает тактов работы устройства, по0 еле чего устанавливает на выходе, являющемся выходом заема, нулевое значение, останавливающее счет по входу разрешения счета. Это значение поступает также на третий инверсный вход элемента И-НЕ

5 10. На первые два входа элемента И-НЕ 10 поступают единичные сигналы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 (это означает, что остаток равен 2) и первого выхода сумматора 6 (это означает, что на старших выходах

0 сумматора 6 определена искомая величина кода Х1). При этом на выходе элемента И-НЕ 10 вырабатывается нулевое значение.запрещающее дальнейший прием информации в промежуточный регистр 2 и обнуляющее

5 код на выходах элементов И группы 8, а на выходах 14 и 15 устройства устанавливаются соответственно коды Х1 частного (в двоично-десятичной системе счисления) и (1+1 разрядный остаток ...0 (в двоич- ной системе счисления).

Регистры 1 и 2 выполняются на микросхемах К155ИР13, сумматор 6 - на микросхемах К155ИМЗ, счетчик 9 выполнен на микрЪсхеме К155ИЕ7, Его установочный вход соединен с входом приема информации через инвертор, информационные входы микросхемы подключены к двоичной константе , вычитающий вход и вход разрешения счета подключены ко входам -1 и +1 соответственно. Узел преобразования выполняется, на микросхемах К155ИМЗ. На этих микросхемах каждая тетрада (предварительно проинвертированная) увеличивается на код с потерей переноса в пятый разряд. Это обеспечивает получе- ние обратного кода двоично-десятичного числа. Делитель на 2 составлен из делителей на 2. Делитель на 2 выполняется на сумматоре (микросхема К155ИМЗ).

По сравнению с прототипом предло- женное устройство позволяет выполнять деление на константу вида в двоично- десятичной системе счисления, что расширяет функциональные возможности устройств подобного вида.

Формула изобретения Устройство для деления чисел на кон- станту типа , содержащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элементы НЕ группы, элементы И группы, причем входы разрядов делимого устройства соединены с информационными входами соответствующих раз- рядов регистра делимого, выходы разрядов которого соединены с входами первой группы сумматора, вход переноса которого соединен с входом логической единицы, выходы частного устройства соединены с информационными входами промежуточного регистра, выходы разрядов которого соединены с входами элементов НЕ группы, выходы младшего разряда частного устройства и младшего разряда промежуточного регистра соединены с первым и вторым входами соответственно элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с выходом старшего разряда остатка устройства и первым прямым входом элемента И- НЕ, выход которого соединен с входом разрешения записи промежуточного регистра и первыми входами элементов И группы, выходы которых соединены с выходами младших разрядов остатка устройства, второй вход первого элемента И группы соединен с вторым прямым входом элемента I/I-HE, инверсный вход которого соединен с инверсным выходом заема и входом разрешения счета счетчика, установочный вход которого соединен с входом запуска устройства, синхровходом регистра делимого и входом сброса промежуточного регистра, синхровход которого соединен с синхровходом счетчика и тактовым входом устройства, отличающееся, тем, что, с целью расширения области применения путем обеспечения возможности выполнения операции деления на константу (2+1)двоично- десятичных чисел, устройство содержит блок деления на 2 и блок преобразования обратного кода в дополнительный, входы которого соединены с выходами элементов НЕ группы, выходы блока преобразования обратного кода в дополнительный соединены с входами второй группы сумматора, выходы которого соединены с входами блока деления на 2 , выходы частного которого соединены с выходами частного устройства, выходы остатка блока деления на 21 соединены с вторыми входами элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1233139A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

Изобретение относится к вычислительной технике, может быть использовано в арифметических блоках ЭВМ и позволяет делить числа на константу типа в двоично-десятичной системе счисления. Целью изобретения является расширение области применения за счет возможности выполнения операции деления на константу (2 +1) двоично-десятичных чисел. Устройство содержит регистр делимого, сумматор, выполняющий сложение в двоично-десятичной системе счисления в дополнительном коде с результатом сложения, деленным с помощью блока деления на 2, задержанным на промежуточном регистре, взятом со знаком - и преобразованным в обратный код на элементах НЕ группы и блока преобразования обратного кода в дополнительный. Вычисления выполняются итерационно за несколько тактов, отсчитываемых счетчиком, по истечении тактов вычислительный процесс останавливается, если остаток не равен 2 . Частное и остаток поступают с выхода делителя на выходы устройства. В противном случае вырабатывается последовательность чередующихся значений результата с недостатком, где вычисляется правильное частное и остаток, равный 2-1, и с избытком. 2 ил. (Л С

| Устройство для деления на константу 2 @ -1 | 1987 |

|

SU1490675A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-30—Публикация

1990-12-10—Подача