«

M oOviereime относится к цифровой вычислительной технике и может 5ыть испольяовяно при построении микропрограммных устройств управления распределенных вычислительных систем, проектируемых на однотипных БИС и реализующих параллельные алгоритмы овработки информации,

Цель изобретения - повышение производительности устройстве.

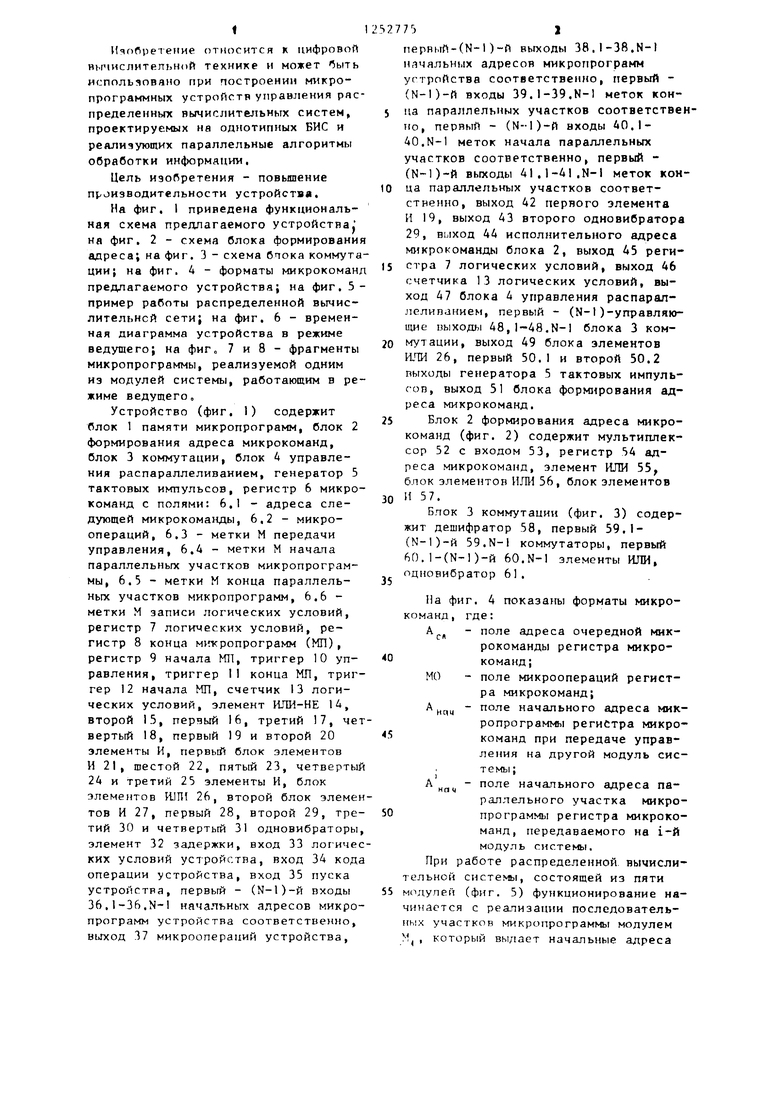

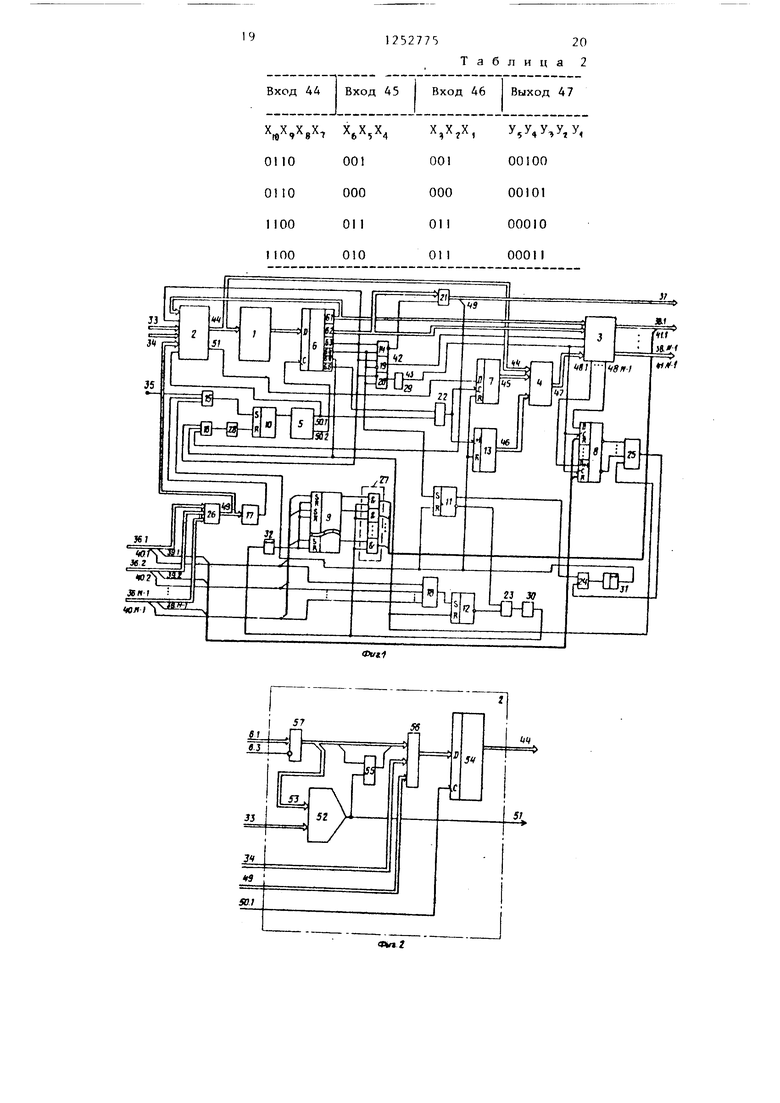

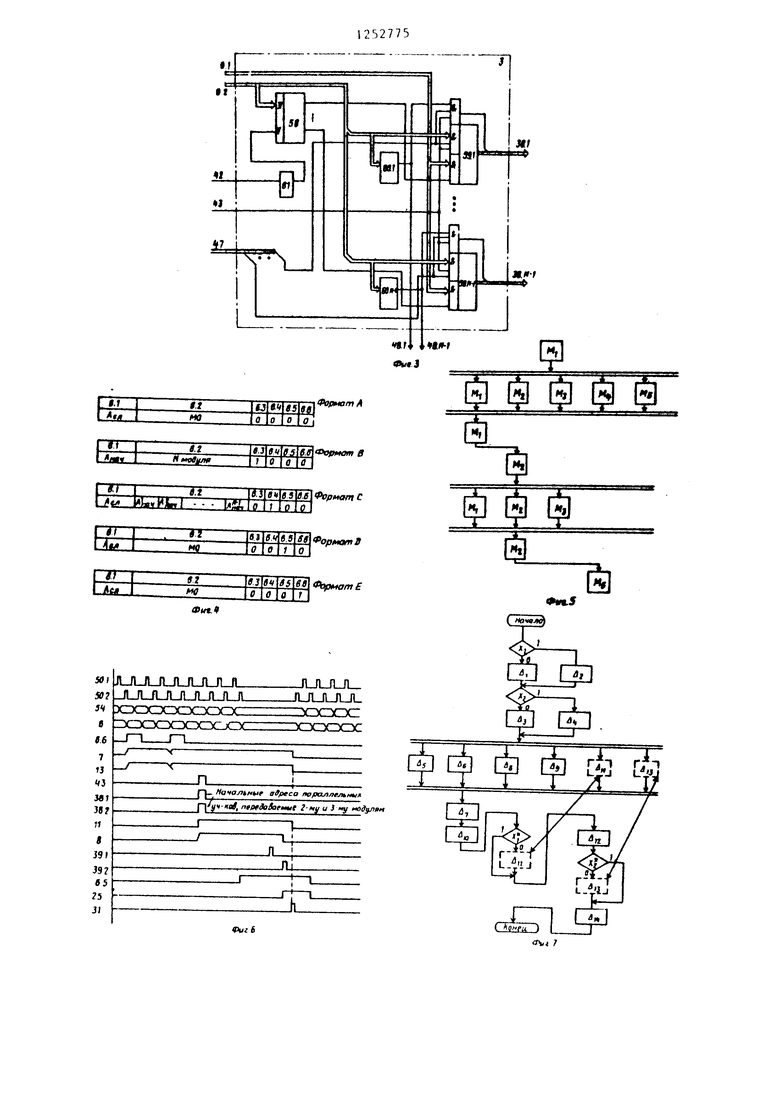

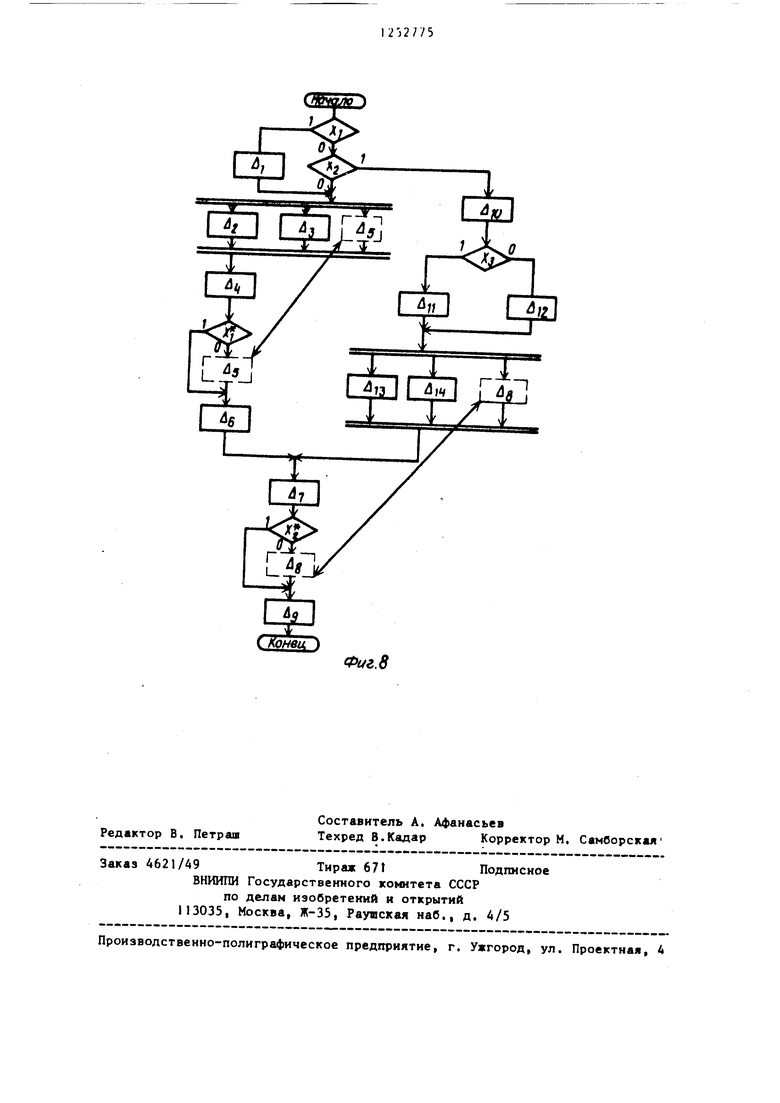

На фиг. 1 приведена функциональная схема предлагаемого устройства на фиг, 2 - схема блока формирования адреса; на фиг, 3 - схема блока коммутации; на фиг. А - форматы микрокоманд предлагаемого устройства; на фиг, 5- пример работы распределенной вычислительной сети; на фиг. 6 - временная диаграмма устройства в режиме ведущего; на фиг 7 и 8 - фрагменты микропрограммы, реализуемой одним из модулей системы, работающим в режиме ведущего.

Устройство (фиг. 1) содержит блок 1 памяти микропрограмм, блок 2 формирования адреса микрокоманд, блок 3 коммутации, блок 4 управления распараллеливанием, генератор 5 тактовых импульсов, регистр 6 микрокоманд с полями: 6.1 - адреса следующей микрокоманды, 6,2 - микроопераций, 6,3 - метки М передачи управления, 6.4 - метки М начала параллельных участков микропрограммы, 6.5 - метки М конца параллельных участков микропрограмм, 6.6 - метки М записи логических условий, регистр 7 логических условий, регистр 8 конца м1п ропрограмм (МП) , регистр 9 начала МП, триггер 10 управления, триггер II конца МП, триггер 12 начала МП, счетчик 13 логических условий, элемент ИЛИ-НЕ 1А, второй 15, первый 16, третий 17, четвертый 18, первый 19 и второй 20 элементы И, первый блок элементов И 21, шестой 22, пятый 23, четвертый 24 и третий 25 элементы И, блок элементов ШГИ 26, второй блок элементов И 27, первый 28, второй 29, третий 30 и четвертый 31 одновибраторы, элемент 32 задержки, вход 33 логических условий устройства, вход 34 кода операции устройства, вход 35 пуска устройства, первый - (N-l)-й входы 36,1-36,N-I начальных адресов микропрограмм устройства соответственно, выход 37 микроопераций устройства.

32773I

перный-(К-I)-й выходы 38,1-38,N-I начальных адресов микропрограмм устройства соответственно, первый - (Ы-1)-й входы 39,1-39,N-1 меток кон5 на параллельных участков соответственно, первый - (М--1)-й входы 40,1- 40,N-1 меток начала параллельных участков соответственно, первый - (N-l)-й выходы 41.1-41,N-I меток кон10 ца параллельных участков соответственно, выход 42 первого элемента И 19, выход 43 второго одновибратора 29, выход 44 исполнительного адреса микрокоманды блока 2, выход 45 реги15 стра 7 логических условий, выход 46 счетчика 13 логических условий, выход 47 блока 4 управления распарал- лелипанием, первый - (N-I)-управляющие 1) 48,.N-1 блока 3 ком20 мутации, выход 49 блока элементов ПТИ 26, первый 50,1 и второй 50.2 выходы генератора 5 тактовых импуль- соп, выход 51 блока формирования адреса микрокоманд,

25 Блок 2 формирования адреса микрокоманд (фиг, 2) содержит мультиплексор 32 с входом 53, регистр 54 адреса микрокоманд, элемент ИЛИ 55, блок элементов ИЛИ 56, блок элементов

30 ч 57,

Блок 3 коммутации (фиг, 3) содержит дешифратор 58, первый 59,1- (Ы-1)-й 59,N-1 коммутаторы, первый 60,1-(Ы-1)-й 60,N-1 элементы ИЛИ,

одновибратор 61,

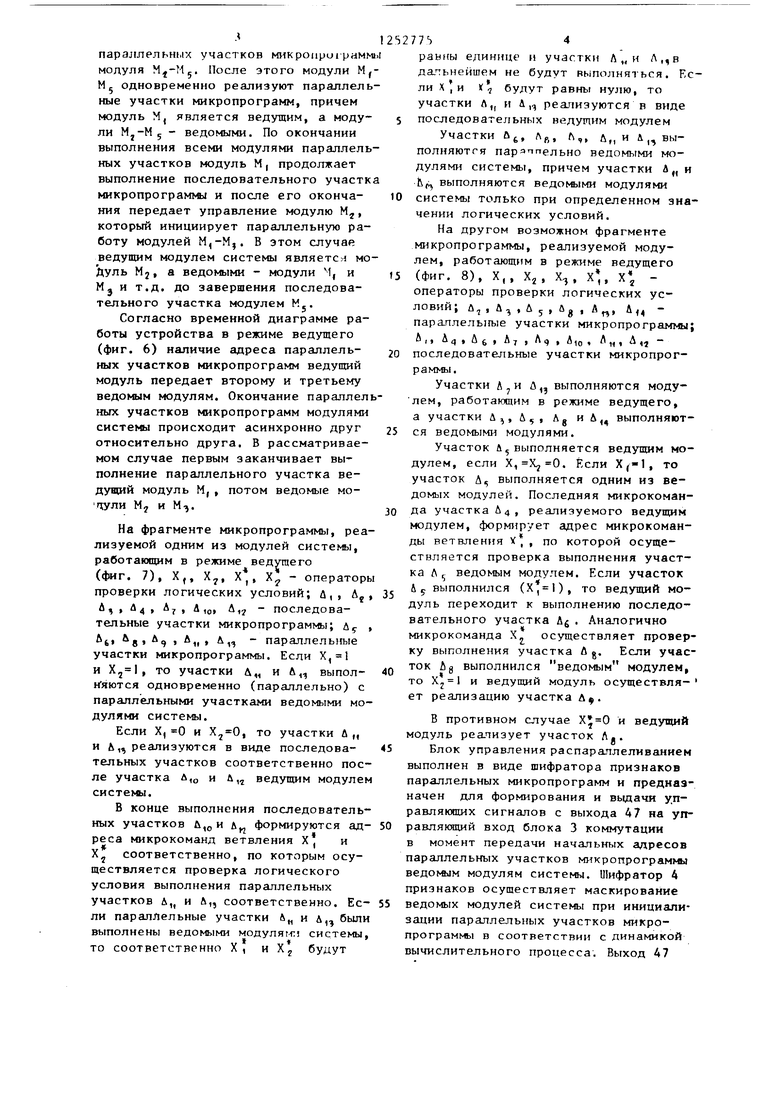

На фиг, 4 показаны форматы микрокоманд, где:

Aj, - поле адреса очередной микрокоманды регистра микрокоманд;

МО - поле микроопераций регистра микрокоманд;

нчч поле начального адреса микропрограммы регистра микрокоманд при передаче управления на другой модуль системы;

А - поле начального адреса параллельного участка микропрограммы регистра микрокоманд, передаваемого на i-й модуль системы.

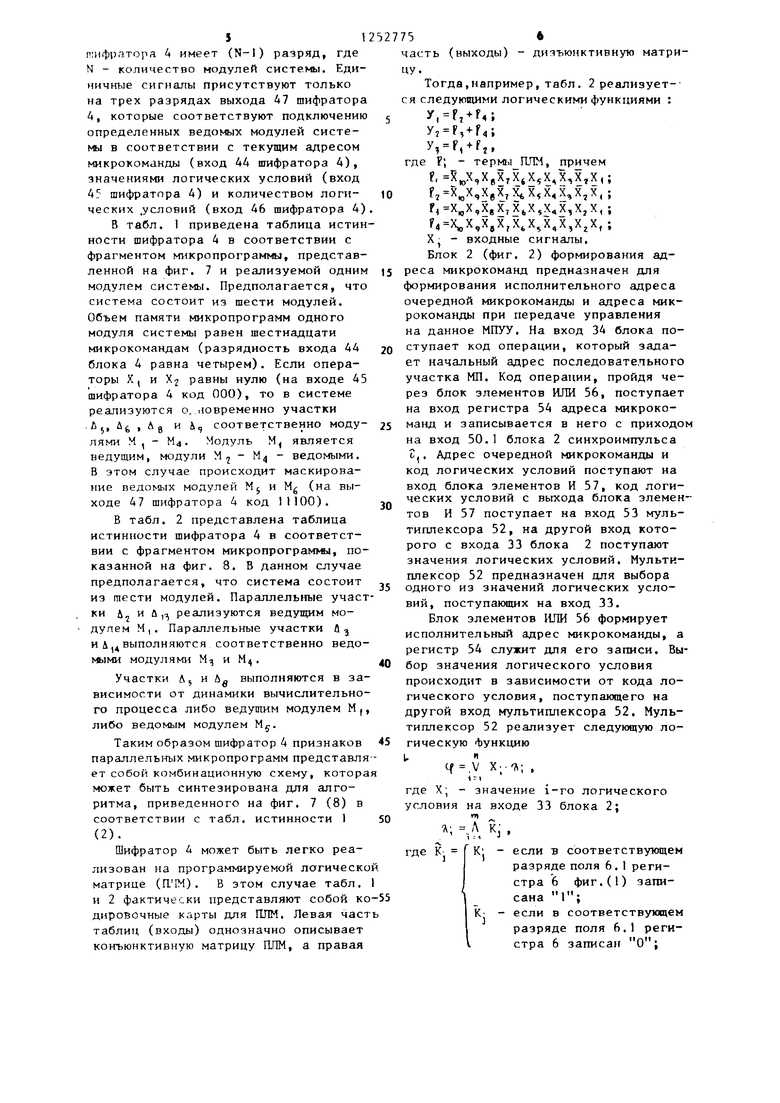

При работе распределенной вычислительной системы, состоящей из пяти модулей (фиг. 3) функционирование начинается с реализации последовательных участков микропрограммы модулем М , который выдает начальные адреса

параллельных участков микропрограмм модуля Mj-Mj. После этого модули М,- М одновременно реализуют параллельные участки микропрограмм, причем модуль М, является ведущим, а модули Mj-My ведомыми. По окончании выполнения всеми модулями параллельных участков модуль М, продолжает выполнение последовательного участка микропрогра п 1 и после его оконча- ния передает управление модулю Mj, который инициирует параллельную работу модулей М,-М,. В этом случае ведущим модулем системы являетС) модуль М, а ведомыми - модули М, и М и т.д. до завершения последовательного участка модулем М.

Согласно временной диаграмме работы устройства в режиме ведущего (фиг. 6) наличие адреса параллель- ных участков микропрограмм ведущий модуль передает второму и третьему ведомым модулям. Окончание параллельных участков микропрограмм модулями системы происходит асинхронно друг относительно друга. В рассматриваемом случае первым заканчивает выполнение параллельного участка ведущий модуль М,, потом ведомые мо- дули Mj и M-j.

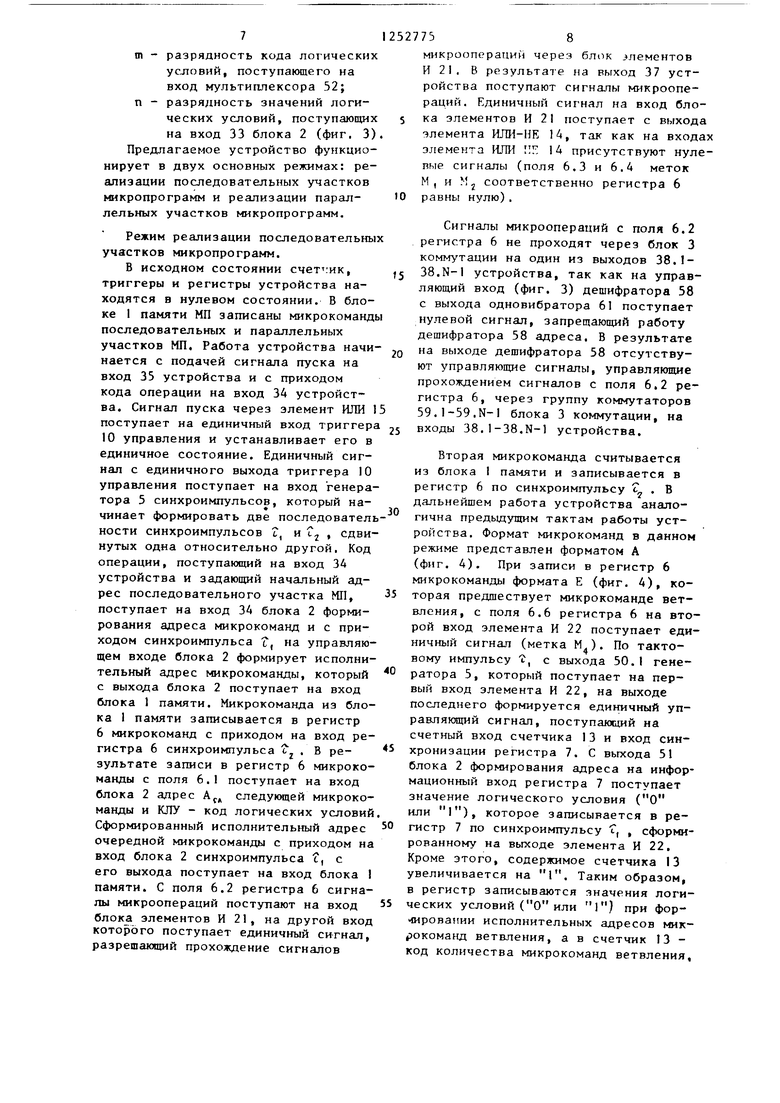

На фрагменте микропрограммы, реализуемой одним из модулей систе}«)1, работающим в режиме ведущего ((. 7), Xj, Ху, Х|, Х - операторы проверки логических условий; и,, А , Л, , 4 , А 10 Ai2 последовательные участки микропрограммы; д

tt 8 9

Л„ , л,, - параллельные участки микропрограммы. Если Х,1 и , то участки д„ и Л,, выпол- яются одновременно (параллельно) с параллельными участками ведомыми модулями системы.

Если X, 0 и , то участки Д ,, и Д,, реализуются в виде последова- тельных участков соответственно после участка Д,о и л„ ведущим модулем системы.

В конце выполнения последовательных участков й,о и , формируются ад-

и

п реса микрокоманд ветвления X

Х соответственно, по которым осуществляется проверка логического условия выполнения параллельных участков д„ и Д,, соответственно. Ее- ли параллельные участки &„ и д, были выполнены ведомыми модулж) системы, то соответственно X, и Х- будут

э2

77 Ь4

единице и участки Л„и Л,,в да/тьнейшем не будут выполняться. Если X , и Х будут равны нулю, то участки Л,, и Д , реализуются в виде 5 последовательных нелущим модулем

U

б

fi.

Л, Л

„и Л „ вы

полняютгя пар 1пельно ведомыми модулями системы, причем участки Л„и Ь,;, выполняются модулями системы только при определенном значении логических условий.

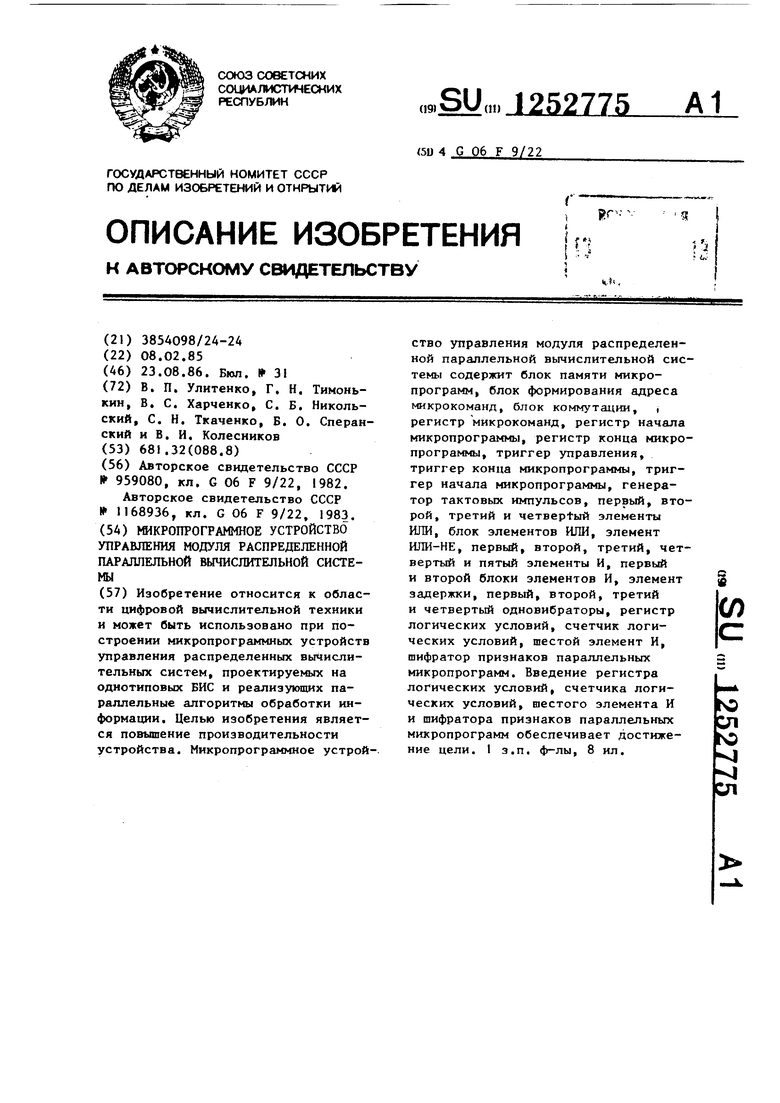

На другом возможном фрагменте микропрограммы, реализуемой модулем, работающим в режиме ведущего

(фиг. 8), X,, Xj, Х

у Y« Л , , Л 2

операторы проверки логических условий; д,,д,,, Л, - параллельные участки микропрограммы; й|. ,U6, Aj , Aq , Д,о, Д„, Д,, - последовательные участки микропрог- .

Участки А ,, и Д,, выполняются моду- лем, работающим в режиме ведущего, а участки Д,,,, Д. иД выполняются ведомыми модулями.

Участок довыполняется ведущим модулем, если Х,. Если Х, то участок Д, выполняется одним из ведомых модулей. Последняя микрокоманда участка U4 реализуемого ведущим

модулем, формирует адрес микрокоман«

ды ветвления V,, по которой осуществляется проверка выполнения участка Д ведомым модулем. Если участок &У выполнился (Х,1), то ведущий модуль переходит к выполнению последовательного участка Д . Аналогично

.-

микрокоманда Х осуществляет проверку выполнения участка и g. Если участок Ag выполнился ведомым модулем, то Xj l и ведущий модуль осуществля- ет реализацию участка д.

В противном случае и ведущий модуль реализует участок Л.

Блок управления распараллеливанием выполнен в виде шифратора признаков параллельных микропрограмм и преднаэ начен для формирования и выдачи управляющих сигналов с выхода 47 на управляющий вход блока 3 коммутации в момент передачи начальных адресов параллельных участков микропрограммы модулям системы. Шифратор 4 признаков осуществляет маскирование ведомых модулей системы при инициализации параллельных участков микропрограммы в соответствии с динамикой вычислительного процесса. Выход А7

51

п:ифр,1тора 4 имеет (N-1) разряд, где N - количество модулей системы. Единичные сигналы присутствуют только на трех разрядах выхода 47 шифратора 4, которые соответствуют подключению определенных ведо{ 1х модулей системы в соответствии с текущим адресом микрокоманды (вход 44 шифратора 4), значениями логических условий (вход 45 шифратора 4) и количеством логи- ческих .условий (вход 46 шифратора 4)

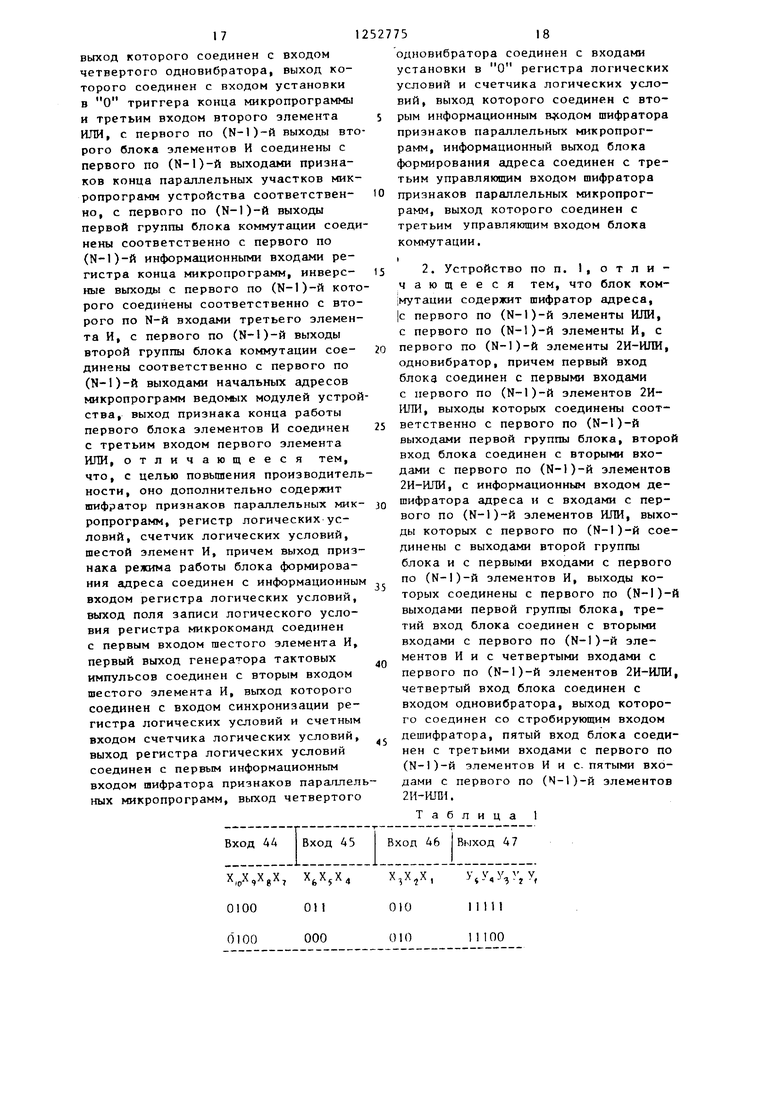

В табл. 1 приведена таблица истинности шифратора 4 в соответствии с фрагментом микропрограммы, представленной на фиг. 7 и реализуемой одним модулем системы. Предполагается, что система состоит из шести модулей. Объем памяти микропрограмм одного модуля системы равен шестнадцати микрокомандам (разрядность входа 44 блока 4 равна четырем). Если операторы X, и Х2 равны нулю (на входе 45 шифратора 4 код 000), то в системе реализуются о, .ювременно участки 5 fe В ч соответственно моду- лями М, - М4. Модуль М является ведущим, модули М - М - ведомыми. В этом случае происходит маскирование ведом1,1х модулей М и М (на выходе 47 шифратора 4 код 11100).

В табл. 2 представлена таблица истинности шифратора 4 в соответствии с фрагментом микропрограм, показанной на фиг. 8. В данном случае предполагается, что система состоит из гаести модулей. Параллельные участки Д и а, реализуются ведущим модулем М,. Параллельные участки й и 4 ц выполняются соответственно ведо- ) модулями М и М .

Участки Л 5 и йд выполняются в зависимости от динамики вычислительного процесса либо ведущим модулем М,, либо ведомым модулем М.

Таким образом шифратор 4 признаков параллельных микропрограмм представляет собой комбинационную схему, котора может быть синтезирована для алгоритма, приведенного на фиг. 7 (8) в соответствии с табл. истинности 1 (2).

Шифратор 4 может быть легко реализован на программируемой логическо матрице (П.ЧМ) . В этом случае табл. и 2 фактически представляют собой ко дировочные карты для ШТМ. Левая част таблиц (входы) однозначно описывает конъюнктивную матрицу ШТМ, а правая

75

часть (выходы) - дизъюнктивную матрицу.

Тогда,например, табл. 2 реализуется следующими логическими функциями :

y,

У7 Г4;

y, F,f

г

где Р; - терм1,, причем

( J f,,XeX,X,X,X,X,X,X,;

Г,Х„Х,Х,Х,Х,Х,Х,Х,Х,Х,;

,Х,Х,Х,Х,Х,Х,Х,Х,;

X, - входные сигналы.

Блок 2 (фиг. 2) формирования адреса микрокоманд предназначен для формирования исполнительного адреса очередной микрокоманды и адреса микрокоманды при передаче управления на данное МПУУ. На вход 34 блока поступает код операции, который задает начальный адрес последовательного участка МП. Код операции, пройдя через блок элементов ИЛИ 56, поступает на вход регистра 54 адреса микрокоманд и записывается в него с приходо на вход 50.1 блока 2 синхроимпульса l, Адрес очередной микрокоманды и код логических условий поступают на

вход блока элементов И 57, код логических условий с выхода блока злементов И 57 поступает на вход 53 мультиплексора 52, на другой вход которого с входа 33 блока 2 поступают значения логических условий. Мультиплексор 52 предназначен цпя выбора одного из значений логических условий, поступающих на вход 33.

Блок элементов ИЛИ 56 формирует исполнительный адрес микрокоманды, а регистр 54 служит для его записи. Выбор значения логического условия происходит в зависимости от кода логического условия, поступающего на другой вход мультиплексора 52. Мультиплексор 52 реализует следующую логическую функцию

U 1

Cf ,V Х- Л; ,

1 1

где X; - значение i-ro логического условия на входе 33 блока 2;

Л; ,Л Kj ,

К-

К; - если в соответствующем разряде поля 6. 1 регистра 6 фиг.(1) записана

К- - если в соответствующем разряде поля 6.1 регистра 6 записан

m - разрядность кода логических условий, поступающего на вход мультиплексора 52; п - разрядность значений логических условий, поступающих на вход 33 блока 2 (фиг, 3). Предлагаемое устройство функционирует в двух основных режимах: реализации последовательных участков микропрограмм и реализации параллельных участков микропрограмм.

Режим реализации последовательных участков микропрограмм.

В исходном состоянии счет . ик, триггеры и регистры устройства находятся в нулевом состоянии. В блоке 1 памяти МП записаны микрокоманды последовательных и параллельных участков МП, Работа устройства начи- нается с подачей сигнала пуска на вход 35 устройства и с приходом кода операции на вход 34 устройства. Сигнал пуска через элемент ИЛИ 1 поступает на единичный вход триггера 10 управления и устанавливает его в единичное состояние. Единичный сигнал с единичного выхода триггера 10 управления поступает на вход генератора 5 синхроимпульсов, который начинает формировать две последователь ности синхроимпульсов (, и Cj, , сдвинутых одна относительно другой, Код операции, поступающий на вход 34 устройства и задающий начальный адрес последовательного участка МП, поступает на вход 34 блока 2 формирования адреса микрокоманд и с приходом синхроимпульса t, на управляющем входе блока 2 формирует исполнительный адрес микрокоманды, который с выхода блока 2 поступает на вход блока 1 памяти. Микрокоманда из блока 1 памяти записывается в регистр 6 микрокоманд с приходом на вход регистра 6 синхроимпульса t . В ре- зультате записи в регистр 6 микрокоманды с поля 6.1 поступает на вход блока 2 адрес А, следующей микрокоманды и КЛУ - код логических условий Сформированный исполнительный адрес очередной микрокоманды с приходом на вход блока 2 синхроимпульса t, с его выхода поступает на вход блока I памяти. С поля 6.2 регистра 6 сигналы микроопераций поступают на вход блок элементов И 21, на другой вход которого поступает единичный сигнал, разрещающий прохождение сигналов

$

10

0

,, - 5 5

микроопераций через блок элементов И 21, В результате яа выход 37 устройства поступают сигналы микроопераций. Единичный сигнал на вход блока элементов И 21 поступает с выхода элемента ИЛИ-НЕ 14, так как на входах элемента ИЛИ Г. 14 присутствуют нулевые сигналы (поля 6.3 и 6,4 меток М, и М соответственно регистра 6 равны нулю),

Сигналы микроопераций с поля 6.2 регистра 6 не проходят через блок 3 коммутации на один из выходов 38.1- 38.N-1 устройства, так как на управляющий вход (фиг. 3) дешифратора 58 с выхода одновибратора 61 поступает нулевой сигнал, запрещающий работу дешифратора 58 адреса. В результате на выходе дешифратора 58 отсутствуют управляющие сигналы, управляющие прохождением сигналов с поля 6,2 регистра 6, через группу коммутаторов 59.1-59,N-I блока 3 коммутации, на входы 38,1-38.N-1 устройства.

Вторая микрокоманда считывается из блока 1 памяти и записывается в регистр 6 по синхроимпульсу с . В дальнейшем работа устройства аналогична предыдущим тактам работы устройства. Формат микрокоманд в данном режиме представлен форматом А (фиг. 4). При записи в регистр 6 микрокоманды формата Е (фиг, 4), которая предшествует микрокоманде ветвления, с поля 6.6 регистра 6 на второй вход элемента И 22 поступает единичный сигнал (метка М ). По тактовому импульсу t, с выхода 50.I генератора 5, который поступает на первый вход элемента И 22, на выходе последнего формируется единичный управляющий сигнал, поступающий на счетный вход счетчика 13 и вход синхронизации регистра 7. С выхода 51 блока 2 формирования адреса на информационный вход регистра 7 поступает значение логического условия (О или 1), которое записывается в регистр 7 по синхроимпульсу Г, , сформированному на выходе элемента И 22, Кроме этого, содержимое счетчика 13 увеличивается на 1. Таким образом, в регистр записываются значения логических условий (О или 1) при фор- шроваиии исполнительных адресов микрокоманд ветвления, а в счетчик 13 - код количества микрокоманд ветвления,

iTin ;uijt стьую ии.х а;)а.г1Г1е чьиым участкам микропригрнмм.

Ряссмотрим функционирование уст- рпйства при передаче управления на другой модуль распределенной парал- лельной вычислительной системы. После реализации всех микропрограмм, хранящихся в блоке 1 памяти Mil, в регистр 6 записывается микрокоманда {х рмата В, в которой метка Mj (поле 6.3 регистра 6) равна единице (фиг. 4). С поля 6.3 регистра 6 единичный сигнал, пройдя через элемент ЯПИ-НЕ i4, запрещает прохождение информации через блок элементов И 2 Кроме того, единичный сигнал (метка М,), поступая на вход блока 2, запрещает прохождение кода начального адреса микропрограммы A.c поля 6,1 регистра 6 для формирования оче- редного адреса микрокоманды данного устройства. Код А поступает на вхо блока 3 коммутации и, в зависимости от кода номера модуля N, , поступающего с поля 6.2 регистра 6 на вход дешифратора 58 (фиг. 3), проходит на один из выходов 38.1-38.N-1.

Единичный сигнал с поля 6.3 (метка М, передачи управления) регистра 6, пройдя через элемент И 19 (на инверсн1)1Й вход элемента И 19 поступает нулевой сигнал с поля 6.4 регистра 6), поступает на вход одно- вибратора 61. С выхода последнего на упрар тяюший вход дешифратора 58 поступает единичный сигнал, в результате чего при поступлении кода

модуля с выхода 6.2 регистра 6 на вход дещифратора 58 на его выходе формируется управляющий сигнал, ко- торый поступает на вход одного из коммутаторов 59.I-59.N-1, разрешая прохождение кода N ,р модуля с поля 6.2 регистра 6 через коммутатор 59.i на выход 38.1 устройства, где i Г, N-I.

С выходов 38.1-38.N-1 устройства передается начальньш адрес последовательного участка микропрограммы, ко- торый будет выполняться очередным модулем распределенной вычислительной систем,.

Единичный сигнал (метка М,), прошедший через элемент ИЛИ 16 и сформированный одновибрАтором 28, поступае ил нулевой вход триггера 10 упраипенчя, который устанавлива

o 5 5

Q

5

5

J

5

7 О

стся в нулевое С(тстояние и тем са- sfiiM выключает генератор 5 синхроимпульсов. Данное устройство выключа- г1тся, и управление передается на другое микропрограммное устройство управления.

Рассмотрим работу устройства при приеме управления. Код адреса А„дц поступает на один из входов 36.1- 36.N-1 начальных адресов микропрограмм устройства в зависимости от того, от какого устройства системы происходит передача управления. Код адреса А, пройдя череп блок элементов ИЛИ 26, поступает на вход элемента ИЛИ 17, который формирует сигнал пуска данного устройства. Сигнал пуска, пройдя через элемент ИЛИ 15, поступает на единичный вход триггера 10 управления и переводит его в единичное состояние. Единичный сигнал с единичного выхода триггера 10 поступает на вход генератора 5 и включает его. Генератор 5 начинает формировать две последовательности синхроимпульсов Т, и L, , которые поступают на входы блока 2 и регистра 6 соответственно. С приходом на вход блока 2 синхроимпульса L, код адреса А,, поступает на выход блоков. Считанная из блока 1 памяти Ш по данному адресу микрокоманда записывается в регистр 6 по синхроимпульсу 2 В дальнейшем работа устройства ничем не отличается от работы устройства на рассмотренных этапах функционирования.

Выключение устройства происходит сигналом микрооперации конца работы, поступающим с выхода блока элементов И 21. Сигнал конца работы, прошедший через элемент ИЛИ 16 и сформированный одновибратором 28, переводит триггер 10 управления в нулевое состояние. В результате генератор 5 синхроимпульсов выключается.

Таким образом, в данном режиме функционирования устройства можно вьщелить следую1цие этапы работ:

выполнение последовательных участков микропрограмм (формат микрокоманд А, метки М, - М равны нулю, формат микрокоманд Е, метка М равна единице) ;

передача управления другому модулю распределенной вычислительной системы (формат микрокоманд В, метка М, равна единице);

прием управления и выполнение последовательного участка МП.

Режим реализации параллельных участков микропрограммы.

Рассмотрим работу в данном режим если устройство является ведущим. В регистр 6 (фиг. I) записывается микрокоманда формата С (фиг. 4). Циничный сигнал (метка М) с поля 6.4 регистра 6, пройдя через элемент ИЛИ-НЕ 14 и поступая на блок элементов И 21, запрещает прохождение информации с поля 6.2 регистров 6 на выход 37 устройства. Коды адресов п«р пер поля 6.2 регистра 6 поступают на соответствующие входы блока 3 коммутации.

Единичный сигнал с поля 6.4 регистра 6 поступает на единичный вход триггера 1I и переводит его в единич ное состояние. Кроме того, этот же сигнал, пройдя через элемент И 20 и поступая на вход одновибратора 29 формируется и проходит на входы синхронизации регистра 8, а также на управляющий вход 43 блока 3 коммутации (фиг. 3). С входа 43 управляющий сигнал поступает на входы коммутаторов 59.1-59.N-1. С входа 6.2 на входы коммутаторов 59.1- 59.N-I поступают соответственно начальные адреса микропрограмм иац которые будут выполняться параллельно несколькими модулями системы. С входа 47 на входы коммутаторов 59.I-59.N-1 поступают единичные сигналы только на коммутаторы, через которые выдаются начальные адреса параллельных участков микропрограммы, поступающие на соот- ветствующие выходы 38.1-38.N-I уст- ройств а. Одновременно с выдачей на другой модуль системы начального адреса А цдц на вьиод 38.1 устройства с выхода коммутатора 59.1 по- ступает сигнал начала параллельного участка микропрограммы. Данный сигнал формируется с выхода элемента ИЛИ 60.1, который поступает на вход коммутатора 59.1 и переходит через него при поступлении единичных сигналов с входа 43 и соответствующего разряда входа 47 блока 3 коммутации .

Таким образом, ведущий модуль системы выдает начальные адреса параллельных участков и сигналы начала параллельных участков микро5 5

20 5 jO Q j «

35

5

программ ведомым модулям при записи в регистр 6 микрокоманды формата С. При этом на входы щифратора 4 признаков параллельных микропрограмм поступает адрес исполняемой микрокоманды с выхода 44 блока 2, код значений логичегкмг: условий с выхода 45 регистра 7 и код количества логических условий микрокоманд ветвления с выхода 46 счетчика 13, выполняемых по ходу алгоритма. С выхода 47 блока на вход блока 3 коммутации по- .ступает информация о тех модулях системы, микропрограммные устройства управления которых будут реализовывать параллельные участки микропрограмм. Одновременно с выдачей начальных адресов параллельных участков на выходы 38.I-38.N-I устройства с соответствующих выходов 48.1-48.N-1 блока 3 коммутации на информационные входы триггеров регистра 8 ведущего модуля поступают единичные сигналы, которые запишутся в регистр 8 с приходом на его входы синхронизации триггеров единичного сигнала с выхода 43 одновибратора 29.

В последующем выполнение параллель ного участка ведущим модулем система ничем не отличается от работы устройства в режиме выполнения последовательного участка МП. В момент окончания параллельного участка ведущим модулем в регистр 6 записывается микрокоманда формата D (фиг. 4). Единичный сигнал с поля 6.5 регистра 6, пройдя через элемент ИЛИ 16 и одно- вибратор 28, поступает на нулевой вход триггера 10 и переводит его в нулевое состоянне. Нулевой сигнал с единичного выхода триггера 10 выключает генератор 5 синхроимпульсов.

Единичный сигнал (метка Mj) с поля 6.5 регистра 6, поступая на нулевой вход триггера 12, подтверждает его исходное (нулевое) состояние, а также поступает на вход элемента И 25. По мере окончания параллельных участков МП ведомыми модулями распределенной вычислительной снстемл на входы 36.1-36.N-1 устройства ведущего модуля поступают сигналы окончания параллельных участков МП, которые с входов 39.1-39.N-1 поступают на нулевые входы первого - (N-l)-ro триггеров регистра 8 соответственно. Триггеры регистра 8 переводятся в нулевое состояние. В ре131

зультате г. выходов регистра 8 на входы элемента И 25 поступают единичные сигналы. После окончания всех параллельных участков МП на выходе элемента И 25 фop Q pyeтcя единичный сигнал, который, пройдя через элемент И 24, одновибратор 31, устанавливает счетчик 13 и регистр 7 в исходное (нулевое) состояние.

Единичный сигнал с выхода триггера 10 включает генератор 5 синхроимпульсов. С выхода поля 6.1 регистра 6 адрес очередной микрокоманды А поступает на вход блока 2 (микрокоманда формата D). С приходом на вход блока 2 синхроимпульса , исполнительный адрес очередной микрокоманды с выхода блока 2 поступает на вход блока I памяти. Таким образом, устройство переходит в режим реализации последовательного участка.

Рассмотрим работу устройства в режиме ведомого. В исходном состоянии все триггеры, счетчик и регистры находятся в нулевом состоянии. Адрес параллельного участка А„д поступает на вход 36,1 начального адреса устройства. Этот код, пройдя через блок элементов ИЛИ 26, поступает на вход элемента ИЛИ 17. Единичный сигнал с выхода элемента ИЛИ 17, пройдя через элемент ИЛИ 15, устанавливает триггер 10 управления в единичное состояние. Генератор 5 синхроимпульсов начинает формировать последовательности тактовых импульсов Т, и С приходом на вход блока 2 синхроимпульса на его выходе будет сформирован исполнительный (начальный) адрес параллельного участка МП. В последующем работа устройства не отличается от режима реализации последовательного участка МП. Одновременно t приходом А на вход 36.1 начального адреса устройства на вход 40.1 поступает сигнал начала параллельного участка МП, который, пройдя череэ элемент ИЛИ 18, переводит триггер 12 в единичное состояние. Этот же сигнал поступает на единичный вход одного из триггеров регистра 9 начала Mil.

По окончании параллельного участка МП в регистре 6 будет записана микрокоманда формата D, В данном i случае поле 6,1 регистра 6 А(-д микрокоманды формата D будет обнулен, Единичный сигнап (метка М), прой751А

ця через элемент ИЛИ 16 и одновибратор 28, поступает на нулевой вход триггера 10 и выключает генератор 5 синхроимпульсов. Кроме того, этот же сигнал, поступая a нулевой вход триггера 12, переводит его в нулевое состояние. Единичный сигнал с нулевого выхода триггера 12, пройдя через элемент И 23 и одновибратор 30,

поступает на входы блока элементов И 27. Сигнал конца параллельного участка МП формируется на выходе того элемента И блока элементов И 27, вход которого подключен к триггеру

регистра 9, находящемуся в единичном состоянии. Сигнал конца параллельного участка МП с выхода блока элементов И 27 поступает на выход 38,1 устройства, сигнализируя ведующему модулю системы об окончании параллельного участка i-м ведомым модулем.

Кроме того, единичный сигнап с выхода одновибратора 30, пройдя элемент 32 задержки и поступая на нулевые входы триггеров регистра 9, обнуляет триггер, находящийся в единичном состоянии. После этого устройство готово к приему управления для

реализации других последовательных или параллельных участков.

На этом работа устройства в режиме ведомого заканчивается.

После окончания программы работы системы (после реализации всех последовательных и параллельных участков микропрограмм) выключение устройства происходит микрооперацией Конец работы, поступающей с выхода блока элементов И 21. Сигнап конца работы, прошедший через элемент ИЛИ 16 и сформированный одновибрато- ром 28, переводит триггер 10 управления в нулевое состояние. Генератор 5 прекращает формирование тактовых импульсов Г, и Tj , и на этом функционирование предлагаемого устройства завершается.

50

Формула изобретения

1. Микропрограммное устройство управления модуля распределенной па- раплельной вычислительной системы, содержащее блок памяти микропрог- рамм, блок формирования адреса микрокоманд, блок коммутации, рст истр микрокоманд, регистры начала и конца микропрограммы, триггеры управления.

конца и начапа ьп1крс)программы, генератор тактовых импульсов, с первого по четвертый элементы ИЛИ, блок элементов ИЛИ, ИЛИ-НЕ, с первого по пятый элементы И, первый и второй блоки элементов И, элемент эадержки, с первого по четвертый одновибраторы, причем входы логических условий и кода команды устройства соединены соответственно с первым и вторым информационными входами блока формирования адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выходы поля адреса которого соединены с первым информационным входом блока ком тации и третьим информационным входом блока формирования адреса, выход поля микроопераций регистра микрокоманд соединен с вторым информационным входом блока коммутации и с информационным входом первого блок элементов И, выход поля признака передачи управления регистра микрокоманд соединен с управляющим входом блока формирования адреса, первым входом элемента ИЛИ-НЕ, первым входом первого элемента И, инверсным входом второго элемента И и первым входом первого элемента ИЛИ, выход которого соединен с входом первого одноьибратора, выход которого соединен с входом установки в О триггера управления, выход поля признака начала параллельных участков микропрограмм регистра микрокоманд соединен с вторым входом элемента ИЛИ-НЕ, инверсным входом первого элемента И, прямым входом второго элемента И и входом установки в 1 триггера конца микропрограмм, выход поля признака конца параллельных участков микропрограмм регистра микрокоманд соединен с вторым входом первого элемента ИЛИ, с входом установки в

г

О триггера начала микропрограм, первым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента И, выход элемента ИЛИ-НЕ соединен с вторым входом первого блока элементов И, выход которого соединен с выходом микроопераций устройства, вход пуска устройства соединен с первым входом второго элемента ПТИ, выход которого соединен с входом установки

0

5

0

5

0

5

0

5

в I 1ригг ера управления, прямой выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входом синхронизации блока формирования адреса и входом синхронизации регистра микрокоманд, с первого по (N-l)-A входы начальных адресов микропрограмм устройства соединены соответственно с первого по (М-1)-й входами блока элементов ИЛИ (где N - число модулей в распределенной системе), выход которого соединен с четвертым информационным входом блока формирования адреса и с входом третьего элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход элемента задержки соединен с входами установки в О регистра начала микропрограмм, выход которого соединен с первым входом второго блока элементов И, выход первого элемента И соединен с первым управляющим входом блока коммутации, выход второго элемента И соединен с входом второго одно- вибратора, выход которого соединен с вторым управляющим входом блока коммутации и с входом синхронизации регистра конца микропрограмм, с первого по (Ы-1)-й входы признаков начала параллельных участков микропрограмм устройства соединены соответственно с первого по (N-l)-fl входами установки в 1 регистра начала микропрограмм и с первого по (N-l)-A входами четвертого элемента ИЛИ, выход когорого соединен с входом установки в 1 триггера начала микропрограммы, инверсный выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с инверсным выходом триггера конца микропрограммы, выход пятого элемента И соединен с входом третьего одновибратора, выход которого соединен с входом элемента эадержки и с вторым входом второго блока элементов И, с первого по (Ы-1)-й входы признаков конца параллельных участков микропрограмм устройства соединены с входами уста- нрвки в О с первого по (N-l)-ft

регистров конца микропрограммы соответственно, прямой выход триггера конца микропрограммы соединен с вторым входом четвертого элемента И,

выход которого соединен с входом четвертого одновибратора, выход которого соединен с входом установки в О триггера конца микропрограммы и третьим входом второго элемента 5 ИЛИ, с первого по (N-l)-ft выходы второго блока элементов И соединены с первого по (N-l)-u выходами признаков конца параллельных участков микропрограмм устройства соответствен- Ю но, с первого по (N-l)-ft выходы первой группы блока коммутации соединены соответственно с первого по (N-l)-A информационными входами регистра конца микропрограмм, инверс- 15 ные выходы с первого по (Ы-1)-й которого соединены соответственно с второго по N-й входами третьего элемента И, с первого по (М-1)-й выходы второй группы блока коммутации сое- 20 динены соответственно с первого по (N-l)-A выходами начальных адресов микропрограмм ведомых модулей устройства, выход признака конца работы первого блока элементов И соединен 25 с третьим входом первого элемента ШШ, отличающееся тем, что, с целью повышения производительности, оно дополнительно содержит шифратор признаков параллельных мик- jo ропрограмм, регистр логических условий, счетчик логических условий, шестой элемент И, причем выход признака режима работы блока формироваодиовибратора соединен с входами установки в О регистра логически условий и счетчика логических усло вий, выход которого соединен с вто рым информационным в;цодом шифратор признаков параллельных микропрограмм, информационный выход блока формирования адреса соединен с тре тьим управляющим входом шифратора признаков параллельных микропрограмм, выход которого соединен с третьим управляющим входом блока коммутации, t

2. Устройство по п. I, отли чающееся тем, что блок ком |мутации содержит шифратор адреса, |с первого по (Ы-1)-й элементы ИЛИ, с первого по (Ы-1)-й элементы И, с первого по (Ы-1)-й элементы 2И-ИЛИ одновибратор, причем первый вход блока соединен с первыми входами с первого по (Ы-1)-й элементов 2И- ИЛИ, выходы которых соединены соот ветственно с первого по (N-l)-A выходами первой группы блока, втор вход блока соединен с вторыми входами с первого по (Ы-1)-й элементо 2И-ИЛИ, с информационным входом де шифратора адреса и с входами с пер вого по (Н-1)-й элементов ИЛИ, вых ды которых с первого по (Ы-1)-й сое динены с выходами второй группы блока и с первыми входами с первог

ния адреса соединен с информационным ,, по (Ы-1)-й элементов И, выходы . /«, .4

входом регистра логических условий, выход поля записи логического условия регистра микрокоманд соединен с первым входом шестого элемента И, первый выход генератора тактовых импульсов соединен с вторым входом шестого элемента И, выход которого соединен с входом синхронизации регистра логических условий и счетным входом счетчика логических условий, выход регистра логических условий соединен с первым информационным входом шифратора признаков параллельных микропрограмм, выход четвертого

40

45

торых соединены с первого по (Ы-1) выходами первой группы блока, третий вход блока соединен с вторыми входами с первого по (N-l)-й элементов И и с четвертыми входами с первого по (Ы-1)-й элементов 2И-ИЛИ четвертый вход блока соединен с входом одновибратора, выход которого соединен со стробирующим входом дешифратора, пятый вход блока соеди нен с третьими входами с первого по (Ы-1)-й элементов И и с- пятыми вхо дами с первого по (N-l)-й элементов 2И-ИЛ11.

X,oX,XgX, Х,Х,Х4 Х,Х,Х, ,,У, 0100 011 010 11111 0100 000 010 11100

одиовибратора соединен с входами установки в О регистра логических условий и счетчика логических условий, выход которого соединен с вторым информационным в;цодом шифратора признаков параллельных микропрограмм, информационный выход блока формирования адреса соединен с третьим управляющим входом шифратора признаков параллельных микропрограмм, выход которого соединен с третьим управляющим входом блока коммутации, t

2. Устройство по п. I, отличающееся тем, что блок ком- |мутации содержит шифратор адреса, |с первого по (Ы-1)-й элементы ИЛИ, с первого по (Ы-1)-й элементы И, с первого по (Ы-1)-й элементы 2И-ИЛИ, одновибратор, причем первый вход блока соединен с первыми входами с первого по (Ы-1)-й элементов 2И- ИЛИ, выходы которых соединены соответственно с первого по (N-l)-A выходами первой группы блока, второ вход блока соединен с вторыми входами с первого по (Ы-1)-й элементов 2И-ИЛИ, с информационным входом дешифратора адреса и с входами с первого по (Н-1)-й элементов ИЛИ, выходы которых с первого по (Ы-1)-й соединены с выходами второй группы блока и с первыми входами с первого

. /«, .4

торых соединены с первого по (Ы-1)-й выходами первой группы блока, третий вход блока соединен с вторыми входами с первого по (N-l)-й элементов И и с четвертыми входами с первого по (Ы-1)-й элементов 2И-ИЛИ, четвертый вход блока соединен с входом одновибратора, выход которого соединен со стробирующим входом дешифратора, пятый вход блока соединен с третьими входами с первого по (Ы-1)-й элементов И и с- пятыми входами с первого по (N-l)-й элементов 2И-ИЛ11.

Таблица 1

,У.УзУ.У

00100100

00000101

01100010

01100011

J/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано при построении микропрограммных устройств управления распределенных вычислительных систем, проектируемых на одиотиповых БИС и реализующих параллельные алгоритмы обработки информации. Целью изобретения является повышение производительности устройства. Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы содержит блок памяти микропрограмм, блок формирования адреса микрокоманд, блок коммутации, i регистр микрокоманд, регистр начала микропрограммы, регистр конца микропрограммы, триггер управления, триггер конца микропрограммы, трнг- гер начала микропрограммы, генератор тактовых импульсов, первый, второй, третий и чeтвeptый элементы ИЛИ, блок элементов ИЛИ, элемент ИЛИ-НЕ, первый, второй, третий, четвертый и пятый элементы И, первый и второй блоки элементов И, элемент задержки, первый, второй, третий и четвертый одновибраторы, регнстр логических условий, счетчик логических условий, шестой элемент И, шифратор признаков параллельных микропрограмм. Введение регистра логических условий, счетчика логических условий, шестого элемента И и шифратора признаков параллельных микропрограмм обеспечивает достижение цели. I з.п. ф-лы, 8 ил. г (Л

1

Я.я-1

tt

МО

13

о IPlo

Форно/пА

Ы El Ы

fopHOrnC

opiHomS

К J Ijy

f afuwmf

Л1П.9

Фм.5

ri-. i

L LjiJ L Li-J M

Фогв

С Коней 3

Редактор В. Петраш

Составитель А. Афанасьев

Техред В.Кадар Корректор М. СамСорская

Заказ 4621/49Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рауяская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

.в

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-02-08—Подача