(54) МИКРОПРОГРЛМЬШОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1979 |

|

SU826348A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

1

Изобретение относится к вычислительной технике, предназначено для формирования последовательности команд при одновременном вычислении ряда функций и может применяться в устройствах обработки дангалх.

Известно устройство управления, содержащее запоминающее устройстве, генератор тактовых импульсов, регистр, дешифраторы, логические схемы, регистр информации П.

Недостатки устройства - малое быстродействие и ограниченные функциональные возможности.

Известно также устройство управления, содержащее арифметический блок, матрицу микропрограмм, счетчик команд, регистр адреса возврата, группы элементов ШШ 2.

Недостатки устройства - невысокое быстродействие и сложность построения .

Наиболее близким по технической сущности к предлагаемому является

устройство, содержащее регистр команд, модификатор адресов команд, регистр адреса микрокоманд, блок памяти, регистр микрокоманд, блок дополнительного условного перехода, блок ввода-вывода, блок прерывания, коммутатор 3 .

Надостато : устройства - ограниченные функциональные возможности, так как оно не позволяет организовать параллельное выполнение нескольких программ.

Целью изобретения является расширение функциональных возможностей за счет организации параллельного

15 выполнения ряда программ.

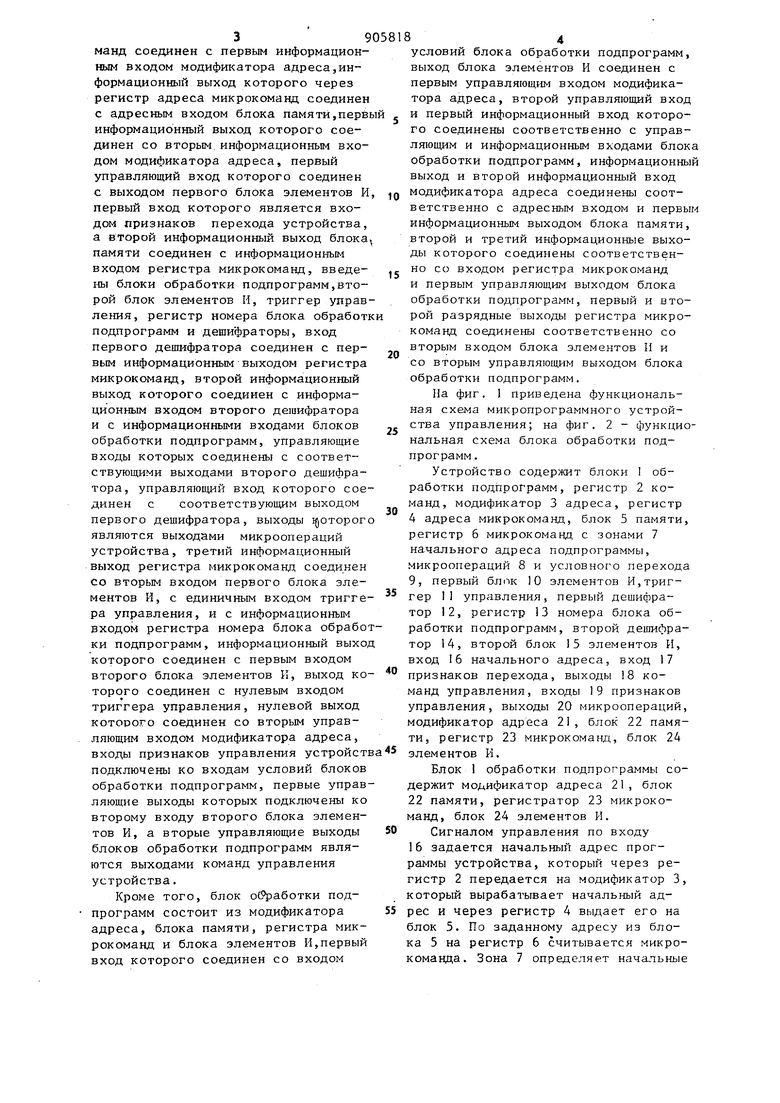

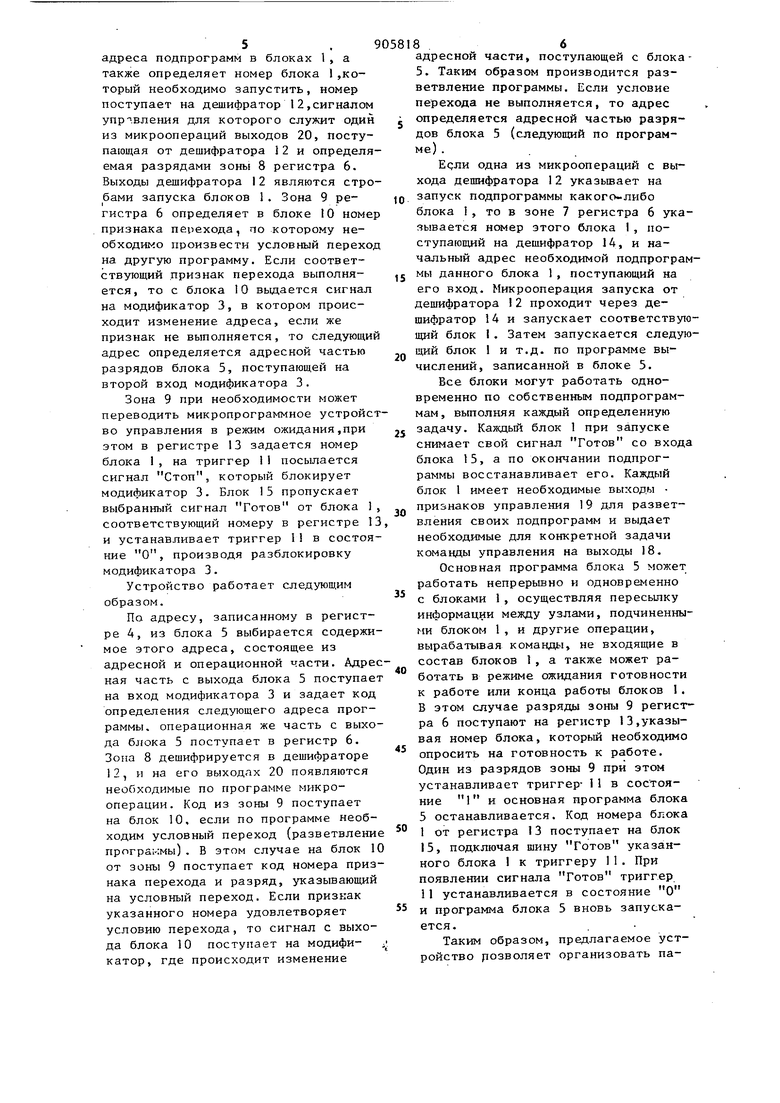

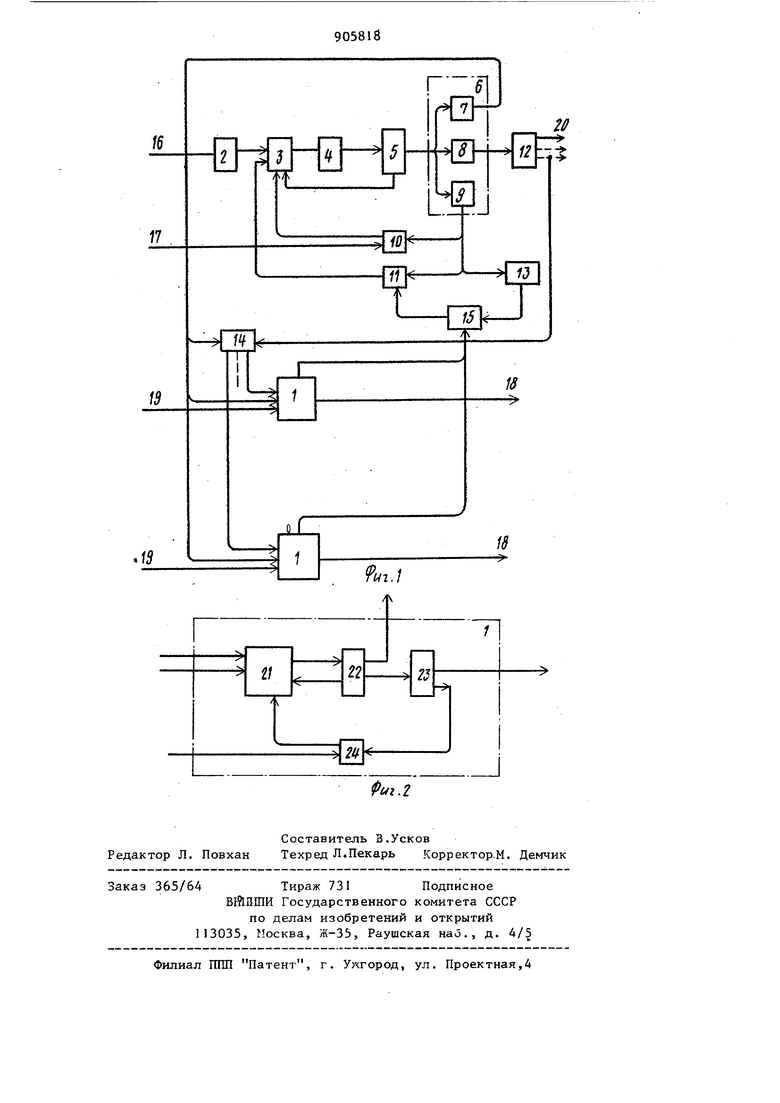

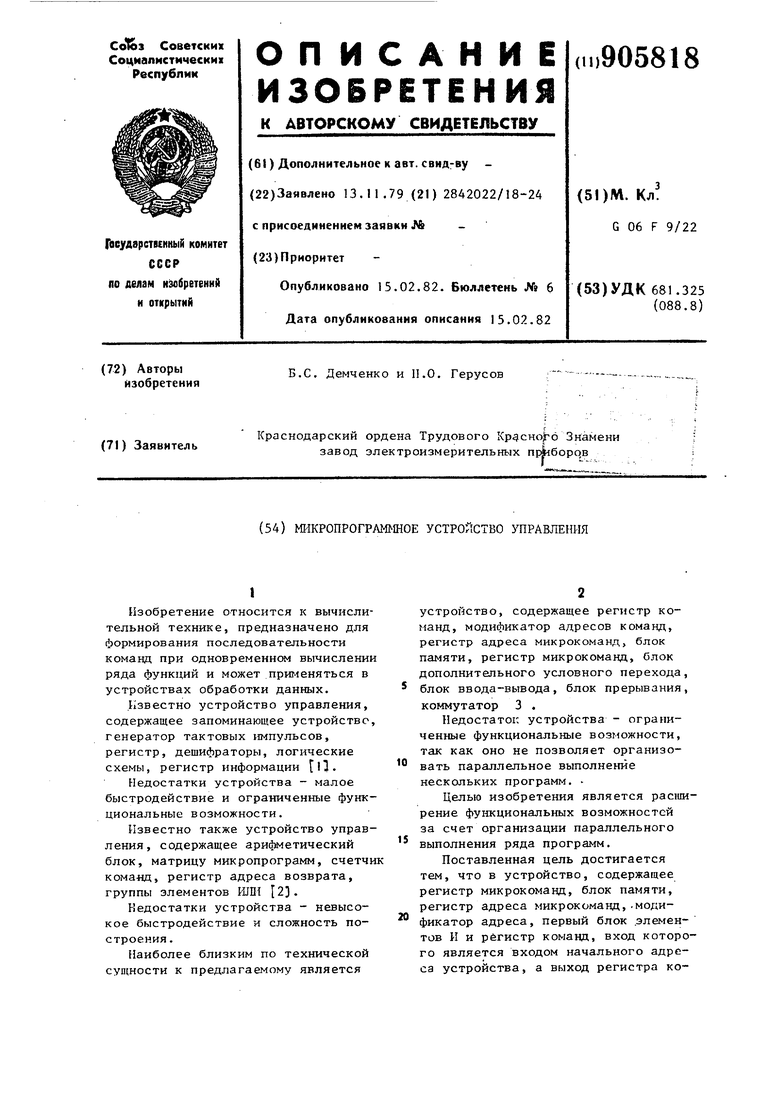

Поставленная цель достигается тем, что в устройство, содержащее регистр микрокоманд, блок памяти, регистр адреса микрокоманд,.моди20фикатор адреса, первый блок элементов И и регистр команд, вход которого является входом начального адреса устройства, а выход регистра ко39манд соединен с первым информационным входом модификатора адреса,информационный выход которого через регистр адреса микрокоманд соединен с адресным входом блока памяти,перв информационный выход которого соединен со вторым информационным входом модификатора адреса, первый управляющий вход которого соединен с выходом первого блока элементов И первый вход которого является входом признаков перехода устройства, а второй информационный выход блока памяти соединен с информационным входом регистра микрокоманд, введены блоки обработки подпрограмм,второй блок элементов И, триггер управ ления, регистр номера блока обработ подпрограмм и дешифраторы, вход первого дешифратора соединен с первым информационным выходом регистра микрокоманд, второй информационный выход которого соединен с информационным входом второго дешифратора и с информационными входами блоков обработки подпрограмм, управляющие входы которых соединень с соответствующими выходами второго дещифратора, управляющий вход которого сое динен с соответствующим выходом первого дешифратора, выходы ijoTopor являются выходами микроопераций устройства, третий информационный выход регистра микрокоманд соединен со вторым входом первого блока элементов И, с единичным входом тригге ра управления, и с информационным входом регистра номера блока обрабо ки подпрограмм, информационный выхо которого соединен с первым входом второго блока элементов И, выход ко торого соединен с нулевым входом триггера управления, нулевой выход которого соединен со вторым управляющим входом модификатора адреса. входы признаков управления устройст подключены ко входам условий блоков обработки подпрограмм, первые управ ляющие выходы которых подключены ко второму входу второго блока элементов И, а вторые управляющие выходы блоков обработки подпрограмм являются выходами команд управления устройства. Кроме того, блок об работки подпрограмм состоит из модификатора адреса, блока памяти, регистра микрокоманд и блока элементов И,первый вход которого соединен со входом 4 условий блока обработки подпрограмм, выход блока элементов И соединен с первым управляющим входом модификатора адреса, второй управляющий вход и первый информационный вход которого соединены соответственно с управляющим и информационным входами блока обработки подпрограмм, информационный выход и второй информационный вход модификатора адреса соединены соответственно с адресным входом и первым информационным выходом блока памяти, второй и третий информационные выходы которого соединены соответственно со входом регистра микрокоманд и первым управляющим выходом блока обработки подпрограмм, первый и второй разрядные выходы регистра микрокоманд соедине Л соответственно со вторым входом блока элементов И и со вторым управляющим выходом блока обработки подпрограмм. На фиг, 1 приведена функциональная схема микропрограммного устройства управления; на фиг. 2 - функциональная схема блока обработки подпрограмм. Устройство содержит блоки обработки подпрограмм, регистр 2 команд, модификатор 3 адреса, регистр 4 адреса микрокоманд, блок 5 памяти, регистр 6 микрокоманд с зонами 7 начального адреса подпрограммы, микроопераций 8 и условного перехода 9, первый блпк 10 элементов И,триггер II управления, первый дешифратор 12, регистр 13 номера блока обработки подпрограмм, второй дешифратор 14, второй блок 15 элементов И, вход 16 начального адреса, вход 17 признаков перехода, выходы 18 команд управления, входы 19 признаков управления, выходы 20 микроопераций, модификатор адреса 21, блок 22 памяти, регистр 23 микрокоманд, блок 24 элементов И. Блок 1 обработки подпрограммы содержит модификатор адреса 21, блок 22 памяти, регистратор 23 микрокоманд, блок 24 элементов И. Сигналом управления по входу 16 задается начальный адрес программы устройства, который через регистр 2 передается на модификатор 3, который вырабатывает начальный адрес и через регистр 4 выдает его на блок 5. По заданному адресу из блока 5 на регистр 6 считывается микрокоманда. Зона 7 определяет начальные 5 . адреса подпрограмм в блоках 1, а также определяет номер блока 1,который необходимо запустить, номер поступает на дешифратор 12,сигналом упр-.вления для которого служит один из микроопераций выходов 20, поступающая от дешифратора 12 и определя емая разрядами зоны 8 регистра 6. Выходы дешифратора I2 являются стро бами запуска блоков J. Зона 9 регистра 6 определяет в блоке 10 номе признака перехода, по которому необходимо произвести условный перехо на другую программу. Если соответствующий признак перехода выполниется, то с блока 10 выдается сигнал на модификатор 3, в котором происходит изменение адреса, если же признак не выполняется, то следующи адрес определяется адресной частью разрядов блока 5, поступающей на второй вход модификатора 3. Зона 9 при необходимости может переводить микропрограммное устройс во управления в режим ожидания,при этом в регистре 13 задается номер блока 1, на триггер 11 посылается сигнал Стоп, который блокирует модификатор 3. Блок 15 пропускает выбранный сигнал Готов от блока 1 соответствующий номеру в регистре 1 и устанавливает триггер 11 в состоя ние О, производя разблокировку модификатора 3. Устройство работает следующим образом. По адресу, записанному в регистре 4, из блока 5 выбирается содержи мое этого адреса, состоящее из адресной и операционной части. Адре ная часть с выхода блока 5 поступае на вход модификатора 3 и задает код определения следующего адреса программы, операционная же часть с выхо да блока 5 поступает в регистр 6. Зона 8 дешифрируется в дешифраторе 12, и на его выходах 20 появляются необходимые по программе микрооперации. Код из зоны 9 поступает на блок 10, если по программе необходим условный переход (разветвлени программы). В этом случае на блок 1 от зоны 9 поступает код номера приз нака перехода и разряд, указывающий на условный переход. Если признак указанного номера удовлетворяет условию перехода, то сигнал с выхода блока 10 поступает на модификатор, где происходит изменение 86 адресной части, поступающей с блока5. Таким образом производится разветвление программы. Если условие перехода не выполняется, то адрес определяется адресной частью разрядов блока 5 (следующий по программе) . Едли одна из микроопераций с выхода дешифратора 12 указьшает на запуск подпрограммы какого-либо блока 1, то в зоне 7 регистра 6 указывается Hcwep этого блока I, поступающий на дешифратор 14, и начальный адрес необходимой подпрограммы данного блока 1, поступающий на его вход. Микрооперация запуска от дешифратора I2 проходит через дешифратор 14 и запускает соответствующий блок I. Затем запускается следующий блок 1 и т.д. по программе вычислений, записанной в блоке 5. Все блоки могут работать одновременно по собственным подпрограммам, выполняя каждый определенную задачу. Каждый блок 1 при запуске снимает свой сигнал Готов со входа блока 15, а по окончании подпрограммы восстанавливает его. Каждый блок 1 имеет необходимые выходы признаков управления 19 для разветвления своих подпрограмм и выдает необходимые для конкретной задачи команды управления на выходы 18. Основная программа блока 5 может работать непрерывно и одновременно с блоками 1, осуществляя пересылку информации между узлами, подчиненными блоком I, и другие операции, вырабатывая команды, не входящие в состав блоков 1, а также может работать в режиме ожидания готовности к работе или конца работы блоков 1. В этом случае разряды зоны 9 регистра 6 поступают на регистр 13,указывая номер блока, который необходимо опросить на готовность к работе. Один из разрядов зоны 9 при этом устанавливает триггер- 1 1 в состояние 1 и основная программа блока 5 останавливается. Код номера блока Iот регистра 13 поступает на блок 15, подключая шину Готов указанного блока 1 к триггеру 11. При появлении сигнала Готов триггер I1устанавливается в состояние О и программа блока 5 вновь запускается. Таким образом, предлагаемое устройство розволяет организовать па7раллельную работу различных управляемых узлов при вычислении несколь ких функций одновременно, т.е. позволяет расширить функциональные позможности известного устройства за счет организации параллельного программирования. Формула изобретения 1. Микропрограммное устройство управления,содержащее регистр микр команд, блок памяти, регистр адреса микрокоманд, модификатор адреса, первый блок элементов И и регистр команд, вход которого является входом начального адреса устройства, а выход регистра команд соединен с первым информационным входом модификатора адреса, информационный выход которого через регистр адреса микрокоманд соединен с адресным входом блока памяти, первый информационный выход которого соединен со вторым информационным входом модификатора адреса, первый управляющий вход которого соединен с выходом первого блока элементов И,первый вход которого является входом признаков перехода устройства а второй информационный выход блока памяти соединен с информационным входом регистра микрокоманд, о тличающееся тем, что, с целью расширения функциональных воз можностей за счет организации парал лепьного выполнения ряда программ, 3 него введены блоки обработки подпрограмм, второй блок элементов К, триггер управления, регистр номера блока обработки подпрограмм и дешифраторы, вход первого дешифратора соединен с первым информационным выходом регистра микрокоманд,второй информационный выход которого соеди нен с информационным входом второго дешифратора и с информационными входами блоков обработки подпрограм управляющие входы которых соединены с соответствующими выходами второго дешифратора, управляющий вход которого соединен с соответствующим выходом первого дешифратора, выходы которого являются выходками микроопе раций устройства, третий информаци(жный выход регистра микрокоманд 88 соединен со вторь1м входом первого блока элементов И, с единичным входом триггера управления и с информационным входом регистра номера блока обработки подпрограмм, информационный которого соединен с первым входом второго блока элементов И, выход которого соединен с нулевым входом триггера управления, нулевой выход которого соединен со вторым управляющим входом модификатора адреса, входы признаков управления устройства Подключены ко входам условиг блоков обработки подпрограмм, первые управляющие выходы которых подключены ко второму входу второго блока элементов И, а вторые управляющие выходы блоков обработки подпрограмм являются выходами команд управления устройства. 2. Устройство по п.1, отличающееся тем, что блок обработки подпрограмм состоит из модификатора адреса, блока ггамяти,регистра микрокоманд и блока эле ентов И, первый вход которого соединен со входом условий блока обработки подпрограмм, выход блока элементов И соединен с первым упраБляю Цим входом модификатора адреса, второй управляющий вход и первый информационный вход которого соединены соответственно с управляющим и информационным входами блока обработки подпрограмм, информационный выход и второй информационный вход модификатора адреса соединены соответственно с адресным входом и первым информационным выходом блока памяти, второй и третий информационные выходы которого соединены соответственно со входом регистра микрокоманд и первым управляющим выходом блока обработки подпрограмм, первый и второй разрядные выходы регистра микрокоманд соединены соответственно со вторым входом блока элe.eнтoв И и со вторым управляющим выходом блока обработки подпрограмм. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 291201, кл. G 06 F 9/16, 1969. 2.Авторское свидетельство СССР № 596947, кл. G 06 F 9/16, 1976. 3. Электронная промышленность, 1978, № 6, с. 49-54 (прототип).

Авторы

Даты

1982-02-15—Публикация

1979-11-13—Подача