11

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации.

Цель изобретения - повьпиение дос- товерности передачи за счет устранения искажений сигналов с резкими перепадами уровня.

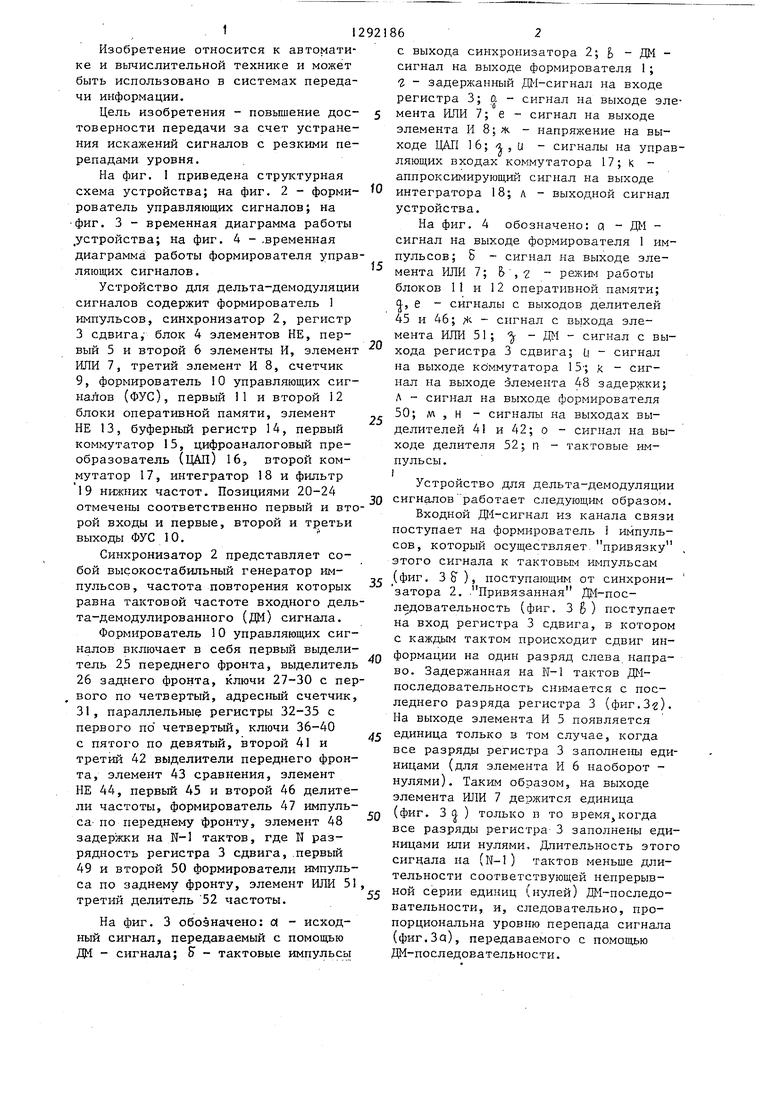

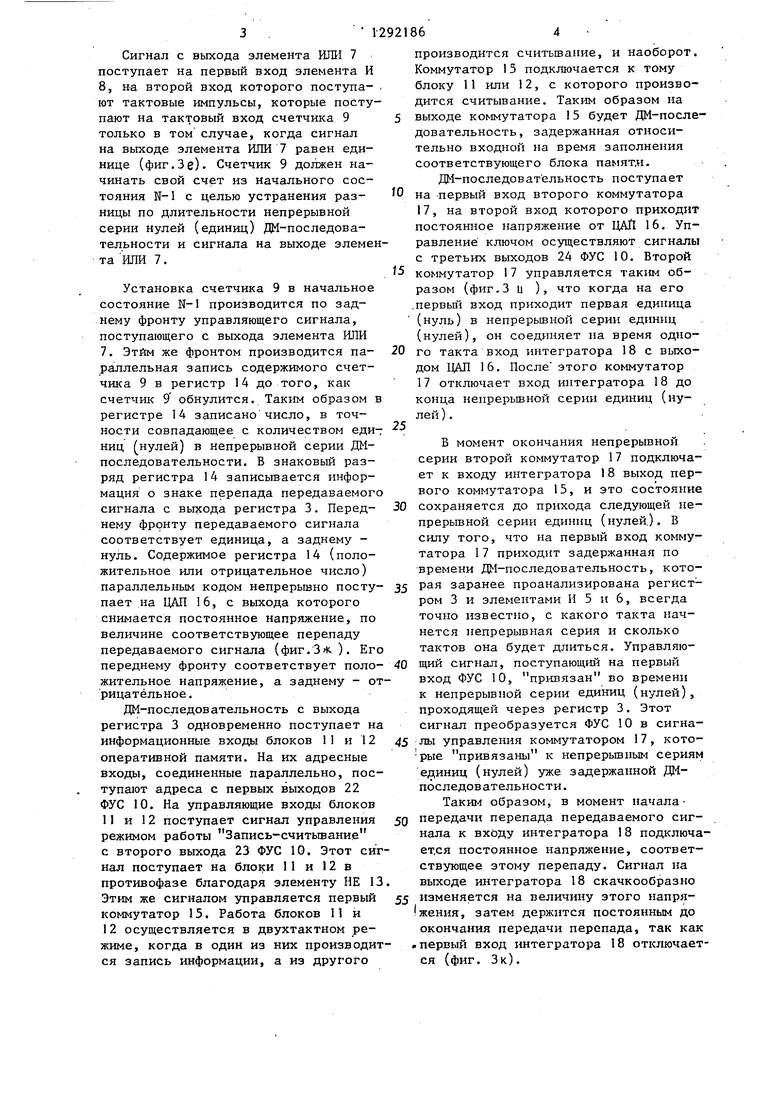

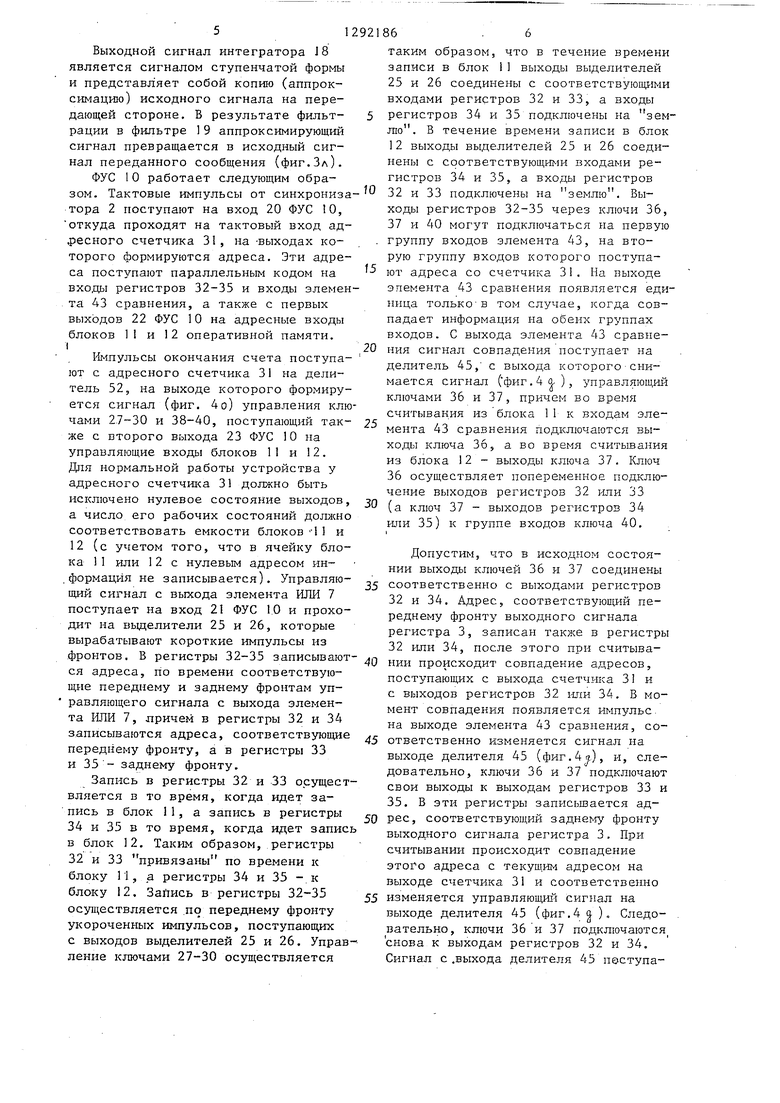

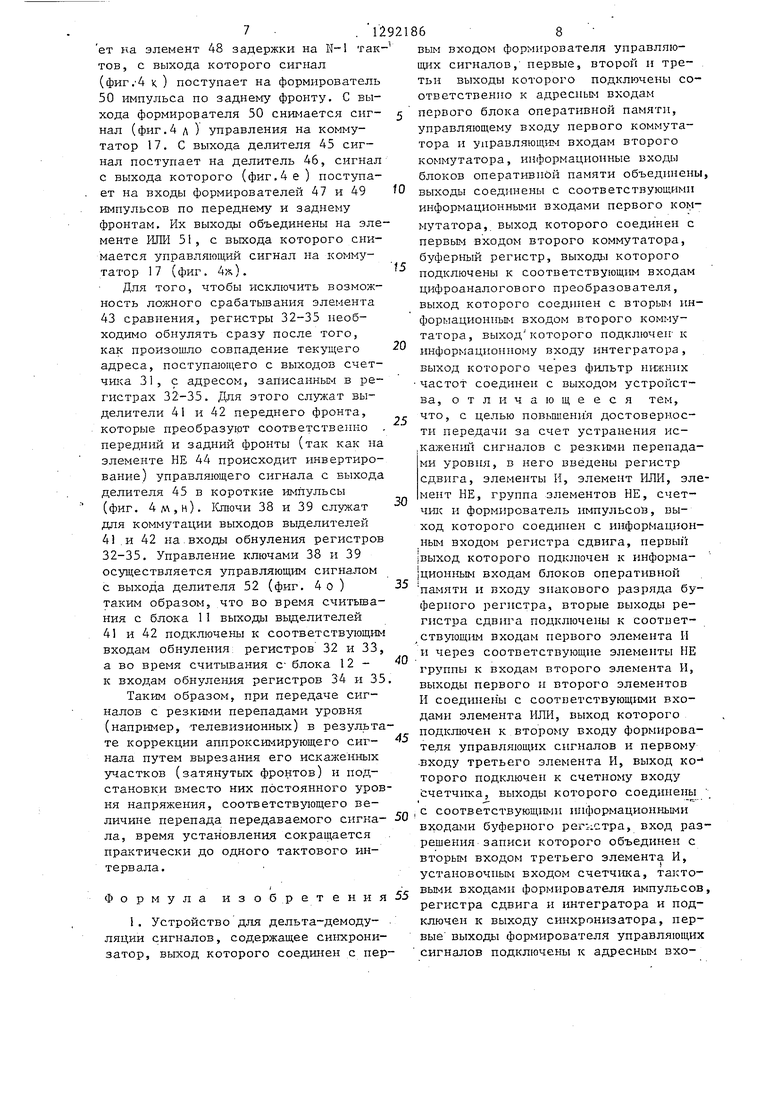

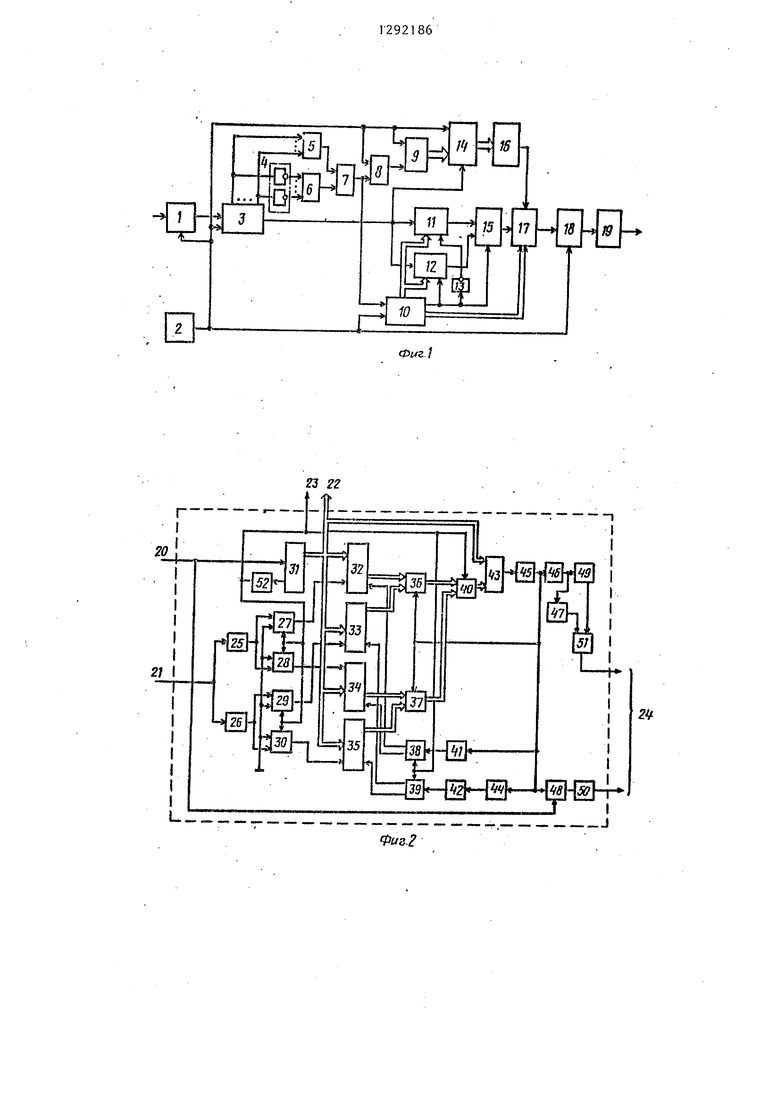

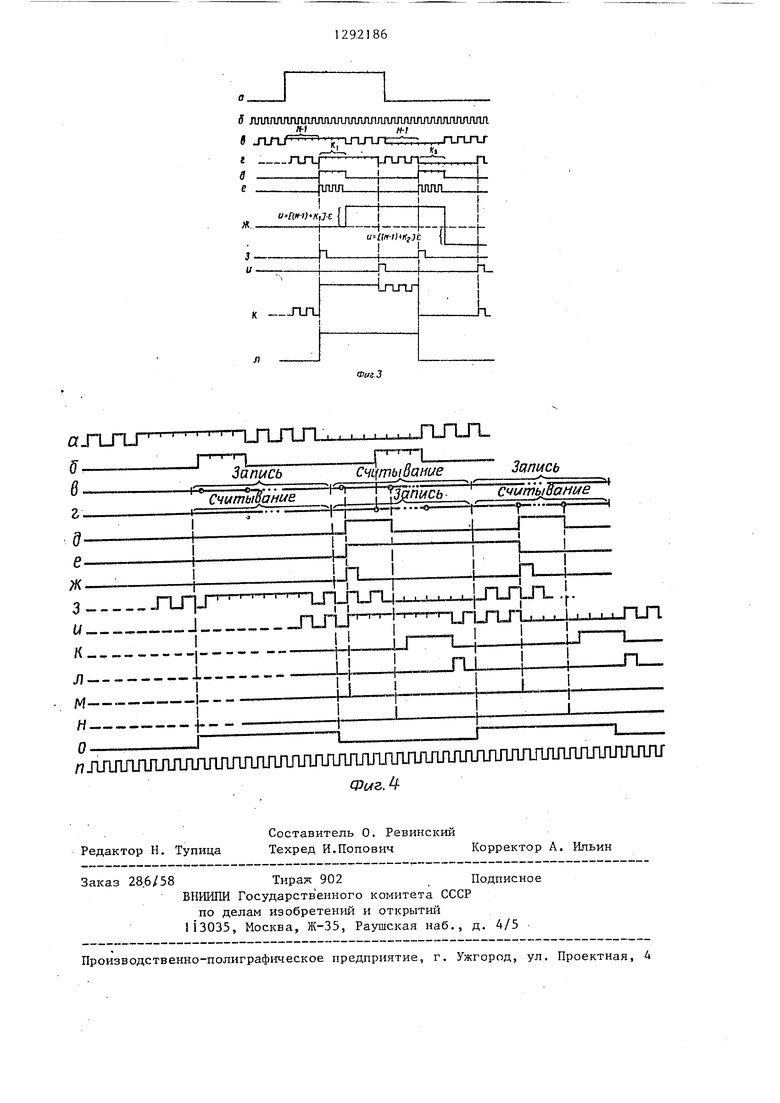

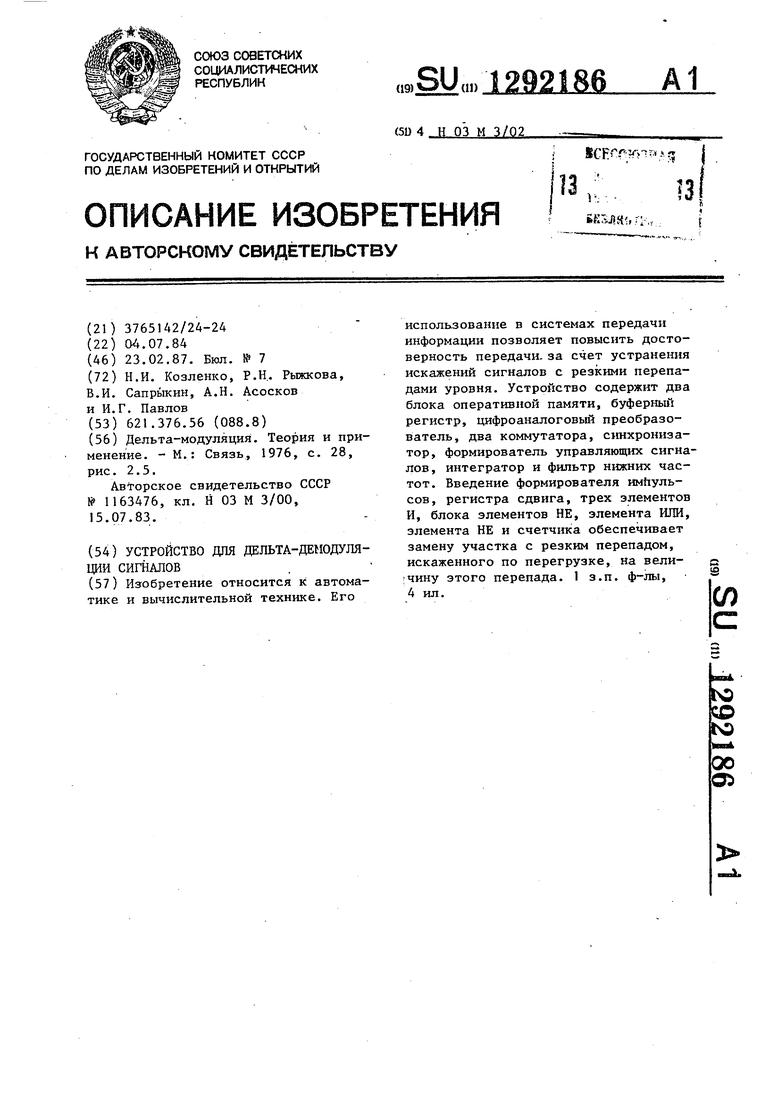

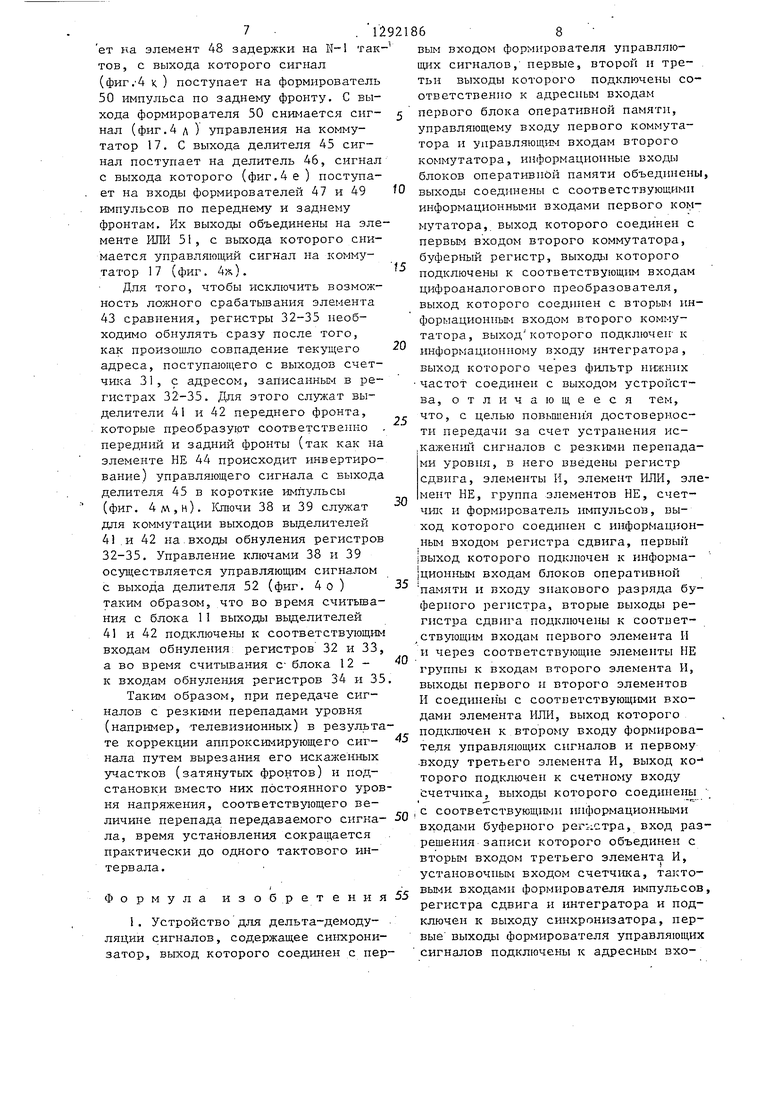

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - форми- рователь управляющих сигналов; на фиг. 3 - временная диаграмма работы ,устройства; на фиг. 4 - .временная диаграмма работы формирователя управляющих сигналов.

Устройство для дельта-демодуляции сигналов содержит формирователь 1 импульсов, синхронизатор 2, регистр 3 сдвига,- блок 4 элементов НЕ, первый 5 и второй 6 элементы И, элемент ИЛИ 7, третий элемент И 8, счетчик 9, формирователь 10 управляющих сигналов (ФУС), первый II и второй 12 блоки оперативной памяти, элемент НЕ 13, буферный регистр 14, первый коммутатор 15, цифроаналоговый преобразователь (ЦАП) 16, второй коммутатор 17, интегратор 18 и фильтр 19 нижних частот. Позициями 20-24

отмечены соответственно первый и второй входы и первые, второй и третьи выходы ФУС 10.

Синхронизатор 2 представляет собой высокостабильный генератор импульсов, частота повторения которых равна тактовой частоте входного дель- та-демодулированного (ДМ) сигнала.

Формирователь 10 управляющих сигналов включает в себя первый выделитель 25 переднего фронта, выделитель 26 заднего фронта, ключи 27-30 с первого по четвертый, адресный счетчик, 31, параллельные регистры 32-35 с первого по четвертый, ключи 36-40 с пятого по девятый, второй 41 и третий 42 выделители переднего фронта, элемент 43 сравнения, элемент НЕ 44, первый 45 и второй 46 делители частоты, формирователь 47 импульса по переднему фронту, элемент 48 задержки на N-1 тактов, где N разрядность регистра 3 сдвига,.первый 49 и второй 50 формирователи импульса по заднему фронту, элемент ИЛИ 51, третий делитель 52 частоты.

На фиг. 3 обозначено: а - исходный сигнал, передаваемый с помощью ДМ - сигнала; 5 - тактовые импульсы

5

0

5

0

0

5

0

5

0

5

862

с выхода синхронизатора 2; I - ДМ - сигнал на выходе формирователя 1; Z - задержанный ДМ-сигнал на входе регистра 3; о. - сигнал на выходе элемента ИЛИ 7; е - сигнал на выходе элемента И 8;, ж - напряжение на выходе ЦАП 16; 1 5 U - сигналы на управляющих входах коммутатора 17; к - аппроксимирующий сигнал на выходе интегратора 18; л - выходной сигнал устройства.

На фиг. 4 обозначено: а - ДМ - сигнал на выходе формирователя 1 импульсов; Б - сигнал на выходе элемента ИЛИ 7; Ь ,2 - режим работы блоков 11 и 12 оперативной памяти; , е - сигналы с выходов делителей 45 и 46; ; - сигнал с выхода элемента ИЛИ 51; - ДМ - сигнал с выхода регистра 3 сдвига; LI - сигнал на выходе кбммутатора 15 ; к - сигнал на выходе элемента 48 задержки; Л сигнал на выходе формирователя 50; м , Н - сигналы на выходах выделителей 41 и 42; о - сигнал на выходе делителя 52; п - тактовые импульсы. I

Устройство для дельта-демодуляции сигналов работает следующим образом.

Входной ДМ-сигнал из канала связи поступает на формирователь 1 импульсов, который осуществляет привязку этого сигнала к тактовьих импульсам (фиг. 38), поступающим от синхрони- затора 2. .Привязанная ДМ-пос- ледовательность (фиг. 3 S) поступает на вход регистра 3 сдвига, в котором с каждым тактом происходит сдвиг информации на однн разряд слева направо. Задержанная на W-1 тактов последовательность снимается с последнего разряда регистра 3 (фиг.З). Па выходе элемента И 5 появляется единица только в том случае, когда все разряды регистра 3 заполнены единицами (для э.лемента И 6 наоборот - нулями). Таким образом, на выходе элемента ИЛИ 7 держится единица (фиг. 3 (J ) только в то время когда все разряды р-егистра 3 заполнены единицами или нулями. Длительность этого сигнала на (N-1) тактов меньше длительности соответствующей непрерывной серии единиц (нулей) ДМ последо- вательности, и, следовательно, пропорциональна уровню перепада сигнала (фиг.За), передаваемого с помощью ДМ-последовательности.

Сигнал с выхода элемента ИЛИ 7 поступает на первый вход элемента И 8, на второй вход которого поступа- , ют тактовые импульсы, которые поступают на тактовый вход счетчика 9 только в том случае, когда сигнал на выходе элемента ИЛИ 7 равен единице (фиг.Зе). Счетчик 9 должен начинать свой счет из начального состояния N-1 с целью устранения разницы по длительности непрерывной серии нулей (единиц) ДМ-последова- тельности и сигнала на выходе элемента ИЛИ 7.

Установка счетчика 9 в начальное состояние N-1 производится по заднему фронту управляющего сигнала, поступающего с выхода элемента ИЛИ 7. Этим же фронтом производится параллельная запись содержимого счетчика 9 в регистр 14 до того, как счетчик 9 обнулится. Таким образом в регистре 14 записано число, в точности совпадающее с количеством единиц нулей) в непрерывной серии ДМ- последовательности. В знаковый разряд регистра 14 записывается информация о знаке перепада передаваемого сигнала с выхода регистра 3. Переднему фронту передаваемого сигнала соответствует единица, а заднему - нуль. Содержимое регистра 14 (положительное или отрицательное число) параллельным кодом непрерывно поступает на ЦАП 16, с выхода которого снимается постоянное напряжение, по величине соответствующее перепаду передаваемого сигнала (фиг.З.). Его

переднему фронту соответствует поло- 40 щий сигнал, поступающий на первый

жительное напряжение, а заднему - отрицательное.

ДМ-последовательность с выхода регистра 3 одновременно поступает на информационные входы блоков 11 и 12 оперативной памяти. На их адресные входы, соединенные параллельно, поступают адреса с первых выходов 22 ФУС 10. На управляющие входы блоков

11и 12 поступает сигнал управления режимом работы Запись-считывание

с второго выхода 23 ФУС 10. Этот сигнал поступает на блоки 11 и 12 в противофазе благодаря элементу НЕ 13. Этим же сигналом управляется первый коммутатор 15. Работа блоков 11 и

12осуществляется в двухтактном режиме, когда в один из них производится запись информации, а из другого

10

921864

производится считьтание, и наоборот. Коммутатор 15 подключается к тому блоку 11 или 12, с которого производится считывание. Таким образом на

5 выходе коммутатора 5 будет ДМ-после- довательность, задержанная относительно входной на время заполнения соответствующего блока памятл.

ДМ-последовательность поступает на первый вход второго коммутатора 17, на второй вход которого приходит постоянное напряжение от 11АП 16. Управление ключом осуществляют сигналы с третьих выходов 24 ФУС 10. Второй

5 коммутатор 17 управляется таким образом (фиг.З ц ), что когда на его .первьш вход приходит первая единица (нуль) в непрерьшной серии единиц (нулей), он соединяет на время одного такта вход интегратора 18 с выходом ЦАП 16. После этого коммутатор 17 отключает вход интегратора 18 до конца непрерьшной серии единиц (нулей).

20

25

0

5

В момент окончания непрерывной серии второй коммутатор 17 подключает к входу интегратора 18 выход первого коммутатора 15, и это состояние сохраняется до прихода следующей непрерывной серии единиц (нулей.), В силу того, что на первый вход коммутатора 17 приходит задержанная по времени ДМ-последовательность, которая заранее проанализирована регистром 3 и элементами И 5 и 6, всегда точно известно, с какого такта начнется непрерывная серия и сколько тактов она будет длиться. Управляювход ФУС 10, привязан во времени к непрерывной серии единиц (нулей), проходящей через регистр 3. Этот сигнал преобразуется ФУС 10 в сигна- 45 ЛЫ управления коммутатором 17, кото- рые привязаны к непрерьшным сериям единиц (нулей) уже задержанной ДМ- последовательности.

Таким образом, в момент начала- 50 передачи перепада передаваемого сигнала к входу интегратора 18 подключается постоянное напряжение, соответствующее этому перепаду. Сигнал на выходе интегратора 18 скачкообразно 55 изменяется на величину этого напря- 1жения, затем держится постоянным до окончания передачи перепада, так как «первый вход интегратора 18 отключается (фиг. Зк).

Выходной сигнал интегратора J8 является сигналом ступенчатой формы и представл яет собой копию (аппроксимацию) исходного сигнала на передающей стороне. В результате фильтрации в фильтре 19 аппроксимирующий сигнал превращается в исходный сигнал переданного сообщения (фиг.3л).

ФУС 10 работает следующим обра1292186 . 6

таким образом, что в течение времени записи в блок 11 выходы выделителей 25 и 26 соединены с соответствующими входами регистров 32 и 33, а входы регистров 34 и 35 подключены на землю. В течение времени записи в блок 12 выходы выделителей 25 и 26 соединены с соответствующими входами регистров 34 и 35, а входы регистров

зом. Тактовые импульсы от синхрониза- 32 и 33 подключены на землю. Вытора 2 поступают на вход 20 ФУС 10, откуда проходят на тактовый вход ад- .ресного счетчика 31, на -выходах которого формируются адреса. Эти адреса поступают параллельньпч кодом на входы регистров 32-35 и входы элемен- та 43 сравнения, а также с первых выходов 22 ФУС 10 на адресные входы

блоков 11 и 12 оперативной памяти. I

Импульсы окончания счета поступают с адресного счетчика 31 на делитель 52, на выходе которого формируется сигнал (фиг. 4о) управления ключами 2.7-30 и 38-40, поступающий также с второго выхода 23 ФУС 10 на управляющие входы блоков 11 и 12. Дпя нормальной работы устройства у адресного счетчика 31 должно быть исключено нулевое состояние выходов, а число его рабочих состояний доллшо соответствовать емкости блоков 1 и 12 (с учетом того, что в ячейку блока 11 или 12 с нулевым адресом ин- формация не записывается). Управляющий сигнал с выхода элемента ИЛИ 7 поступает на вход 21 ФУС 10 и проходит на вьщелители 25 и 26, которые вырабатывают короткие импульсы из фронтов. В регистры 32-35 записываются адреса, по времени соответствующие переднему и заднему фронтам уп- равляющего сигнала с выхода элемента ИЛИ 7, лричем в регистры 32 и 34 записываются адреса, соответствующие переднему фронту, а в регистры 33 и 35- заднему фронту.

Запись в регистры 32 и 33 осуществляется в То время, когда идет запись в блок 11, а запись в регистры 34 и 35 в то время, когда идет запись в блок 12. Таким образом, регистры 32 и 33 привязаны по времени к блоку 11, а регистры 34 и 35 блоку 12. Запись в регистры 32-35 осуществляется по переднему фронту укороченных импульсов, поступающих с выходов выделителей 25 и 26. Управление ключами 27-30 осуществляется

ходы регистров 32-35 через ключи 36, 37 и 40 могут подключаться на первую группу входов элемента 43, на вторую группу входов которого поступают адреса со счетчика 31. На выходе элемента 43 сравнения появляется единица только В том случае, когда совпадает информация на обеих группах входов. С выхода элемента 43 сравне- ния сигнал совпадения поступает на делитель 45, с выхода которого снимается сигнал ( фиг. 4 q. ), управляющий ключами 36 и 37, причем во время считывания из блока 11 к входам элемента 43 сравнения подключаются выходы ключа 36, а во время считывания из блока 12 - выходы ключа 37. Ключ 36 осуществляет попеременное подключение выходов регистров 32 или 33

(а ключ 37 - выходов регистров 34 или 35) к группе входов ключа 40.

Допустим, что в исходном состоянии выходы ключей 36 и 37 соединены

соответственно с выходами регистров 32 и 34. Адрес, соответствующий переднему фронту выходного сигнала регистра 3, записан также в регистры 32 или 34, после этого при считываНИИ происходит совпадение адресов, поступающих с выхода счетчика 31 и с выходов регистров 32 1ши 34. В момент совпадения появляется импульс. tia выходе элемента 43 сравнения, соответственно изменяется сигнал на выходе делителя 45 (фиг.4ч ,), и, следовательно, ключи 36 и 37 подключают свои выходы к выходам регистров 33 и 35. В эти регистры записьшается адрес, соответствующий заднему фронту выходного сигнала регистра 3. При считывании происходит совпадение этого адреса с текуш.им адресом на выходе счетчика 31 и соответственно

изменяется управляющий сигнал на

выходе делителя 45 (фиг.4 ), Следовательно, ключи 36 и 37 подключаются снова к выходам регистров 32 и 34, Сигнал с .выхода делителя 45 пеступа

7 . 12

ет на элемент 48 задержки на Ы-1 так тов, с выхода которого сигнал (фиг. 4 к ) поступает на формирователь 50 импульса по заднему фронту, С выхода формирорателя 50 снимается сиг- нал (фиг.4 л ) управления на коммутатор 17. С выхода делителя 45 сигнал поступает на делитель 46, сигнал с выхода которого (фиг.4е) поступает На входы формирователей 47 и 49 импульсов по переднему и заднему фронтам. Их выходы объединены на элементе ИЛИ 51, с выхода которого снимается управляющий сигнал на коммутатор 17 (фиг. .).

Для того, чтобы исключить возможность ложного срабатывания элемента 43 сравнения, регистры 32-35 необходимо обнулять сразу после того, как произошло совпадение текущего адреса, поступающего с выходов счет- чшса 31, с адресом, записанньм в регистрах 32-35. Для этого служат выделители 41 и 42 переднего фронта, которые преобразуют соответственно передний и задний фронты (так как па элементе НЕ 44 происходит инвертирование) управляющего сигнала с выхода делителя 45 в короткие импульсы (фиг. 4м, и). 1Сточи 38 и 39 служат для коммутации выходов выделителей 41.и 42 на.входы обнуления регистров 32-35. Управление ключами 38 и 39 осуществляется управляющим сигналом с выхода делителя 52 (фиг. 4 о ) таким образом, что во время считьша- ния с блока 11 выходы выделителей 41 и 42 подключены к соответствующим входам обнуления: регистров 32 и 33, а во время считывания С блока 12 - к входам обнуления регистров 34 и 35

Таким образом, при передаче сигналов с резкими перепадами уровня (например, телевизионных) в результате коррекции аппроксимирующего сиг- нала путем вырезания его искаженных участков (затянутых фронтов) и подстановки вместо них постоянного уровня напряжения, соответствзпощего величине перепада передаваемого сигна- ла, время установления сокращается практически до одного тактового интервала.

/ Формула изобретения

1. Устройство для дельта-демодуляции с.игналов, содержащее синхронизатор, выход которого соединен с пер5

21

O -5

0 5

-5 0

5

868

вым входом формирователя управляющих сигналов, первые, второй и тре- . тьи выходы которого подключены соответственно к адресным входам первого блока оперативной памяти, управляющему входу первого коммутатора и управляющим входам второго коммутатора, информационные входы блоков оперативной памяти объединены, выходы соединены с соответствующими информационньми входамн первого коммутатора,, выход которого соединен с первым входом второго коммутатора, буферный регистр, выходы которого подключены к соответствующим входам цифроаналогового преобразователя, выход которого соедпнен с вторым ин- формационныг-1 входом второго коммутатора, выход которого подключен- к информационному входу интегратора, выход которого через фильтр in-скних

частот соединен с выходом устройства, отличающееся тем, что, с целью повьпдени я достоверности передачи за счет устранения ис- каженш сигналов с резкими перепадами уровня, в него введены регистр сдвига, элементы И, элемент I-LOH, элемент НЕ, групна элементов НЕ, счет- чшс и формирователь импульсой, выход которого соединен с информационным входом регистра сдвига, первы |выход которого подключен к информа- |Циомным входам блоков оперативной и входу знакового разряда буферного регистра, вторые выходы регистра сдвига подключены к соответ ству ощим входам первого элемента И и через соответствующие элементы НЕ группы к входам второго элемента И, выходы первого и второго элементов И соединен ы с соответствующими входами элемента ИЛИ, выход которого подключен к второму входу формирователя управляющих сигналов и первому ВХОДУ третьего элемента И, выход ко- торого подключен к счетному входу счетчика, выходы которого соединены

, с соответствующими ипформационньими входами буферного рег:-:стра, вход раз- рещения записи которого объединен с вторым входом третьего элемента И, установочным входом счетчика, такто- BbijviK входами формирователя импульсов, регистра сдвига и интегратора и подключен к выходу синхронизатора, первые выходы формирователя управляющих сигналов подключены к адресньм вхоf5

91292186

дам второго блока оперативной памяти, второй выход, формирователя управляющих сигналов соединен с управляющим входом второго блока оперативной памяти и через элемент НЕ с управляю- 5 щим входом первого блока оперативной памяти, информационный вход формирователя импульсов является информационным входом устройства. 2. Устройство по П.1, о т л и ч а-JO ю щ е е с я тем, что формирователь

управляющих сигналов включает в себя .адресньй счетчик, первые выходы которого подключены к соответствующим информационным входам параллельных регистров с первого по четвертый, соответствующим первым входам элемента сравнения, и являются соответствующими первыми выходами формирователя управляющих сигналов, тактовый вход адресного счетчика объединен с управляющим входом элемента задержки на N-1 тактов и является первым входом формирователя управляющих сигналов, первый выделитель переднего фронта и выделитель заднего фронта, входы которых объединены и являются вторым входом формирователя управляющих сигналов, выходы подключены к первьм входам соответственно первого, второго, третьего и четвертого ключей, вторые входы которых объединены и подключены к шине нулевого потенциала, выходы первого, третьего, второго и четвертого ключей соединены с входами разрешения записи параллельных регистров соответственно с первого по четвертый, выходы первого и второго параллельных регистров подключены cooTBeT-t ственно к первым и вторым входам пятого ключа, выходы третьего и четвер того параллельных регистров подключены соотв етственно к первым и вторым входам шестого ключа, седьмой

20

25

30

35

40

45

кл го со па пе ди ст ле ше ве де кл вх то ты пя ро вх то вы ко вх та де то вх ад тр то да и вт ля те ми фр пу то вх за вх са и им щи

5

2186

5 O

0

5

0

5

0

5

10

ключ, первый и второй выходы которого соединены с входами обнуления соответственно первого и третьего параллельных регистров, восьмой ключ, первый и второй выходы которого соединены с входами обнуления соответственно второго и четвертого параллельных регистров, выходы пятого и шестого ключей соединены соответственно с первыми и вторыми входами девятого ключа, выходы которого подключены к соответствующим вторым входам элемента сравнения, выход которого через первый делитель частоты соединен с управляющими входами пятого и шестого ключей, входами второго делителя частоты, информационным входом элемента задержки на N-1 тактов, входами элемента НЕ и второго выделителя переднего фронта, выход которого соединен с информационным входом седьмого ключа, выход элемента НЕ подключен к входу третьего выделителя переднего фронта, выход которого соединен с информационным входом восьмого ключа, второй выход адресного счетчика соединен с входом третьего делителя частоты, выход ко- торого подключен к управляющим входам ключей с первого по четвертьй и с седьмого по девятый и является вторым выходом формирователя; управляющих сигналов, выход второго делителя частоты соединен с входами формирователя импульса по переднему фронту и первого формирователя импульса по заднему фронту, выходы которых подключены к соответствующим входам элемента ИЛИ, выход элемента задержки на N-1 тактов соединен с входом второго формирователя импульса по заднему фронту, выход которого и выход элемента ИЛИ являются третьими выходами формирователя управляющих сигналов.

I

лллллшшпллштпшшгтпллллппллпшгллпя

9

К-r-

rU-Lrxr

| название | год | авторы | номер документа |

|---|---|---|---|

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство синхронизации М-последовательности | 1981 |

|

SU1053312A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для измерения линейных перемещений | 1981 |

|

SU1013734A1 |

| ГЕНЕРАТОР СИГНАЛОВ СЛОЖНОЙ ФОРМЫ | 1991 |

|

RU2019908C1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи информации позволяет повысить достоверность передачи- за счет устранения искажений сигналов с резкими перепадами уровня. Устройство содержит два блока оперативной памяти, буферньш регистр, цифроаналоговый преобразователь, два коммутатора, синхронизатор, формирователь управляющих сигналов, интегратор и фильтр нижних частот. Введение формирователя имhyль- сов, регистра сдвига, трех элементов И, блока элементов НЕ, элемента ИЛИ, элемента НЕ и счетчика обеспечивает замену участка с резким перепадом, искаженного по перегрузке, на вели- ;чину этого перепада. 1 з.п. ф-лы, 4 ил. iS сл

TJ

ТЛЛЛ. „,,,,., jnjUl-.

Запись

Считывание

А7 лJгIшnJIJlгuгплгlЛJ JШJШJlJU

Фмг.

Редактор Н. Тупица

Составитель О. Ревинский

Техред И.Попович Корректор А. Ильин

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытие 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственйо-полиграфвдеское нредприятие, г. Ужгород, ул. Проектная, 4

Считывание

| Дельта-модуляция | |||

| Теория и применение | |||

| - М.: Связь, 1976, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1984-07-04—Подача