Изобретение относится к автоматике и вычислительной технике и может быть кспопъздвано в цифровых вычислительных, системах, а также терминальной аппаратуре.

Целью изобретения является повышение надежности работы устройства за счет стробирования уровней входны сигналов и их длительности.

На фиг.1 изображена функциональ- пая схема микропрограммного устройства управления; на фиг.2 - функциональная схема блока синхронизации; на фиг,3 - функциональная схема формирователя адресов микрокоманд; на фиг. 4 - схема определения адреса следующей микрокоманды; на - таблица истинности схемы определения йдреса следующей микрокоманды; на фиг.6 - формат микрокоманды; на фиг.7 - временные диаграммы, иллюстрирующие работу устройства; на фиг.8 - функциональная схема схемы сравнения.

Микропрограммное устройство управления (фиг.1) имеет первьш 1 и второй 2 входы логических условий, вход 3 кода команды, вход 4 начальной ус- тановк и и содержит первый 5, второй 6 и третий 7 компараторы уровней, первый 8 и второй 9 мультиплексоры условий, мультиплексор 1.0 команды, элемент ИЛИ 1I, регистр 12 адреса и регистр 13 условий, мультиплексор 14 адреса, формирователь 15 адресов микрокоманд, схему 16 сравнения, первый элемент И 17, первый 18.1 и второй 8.2 элементы задержки, блок 19 памяти микрокоманд, блок 20 синхронизации, второй 21 и третий 22 элементы И, выход 23 микрооперации.

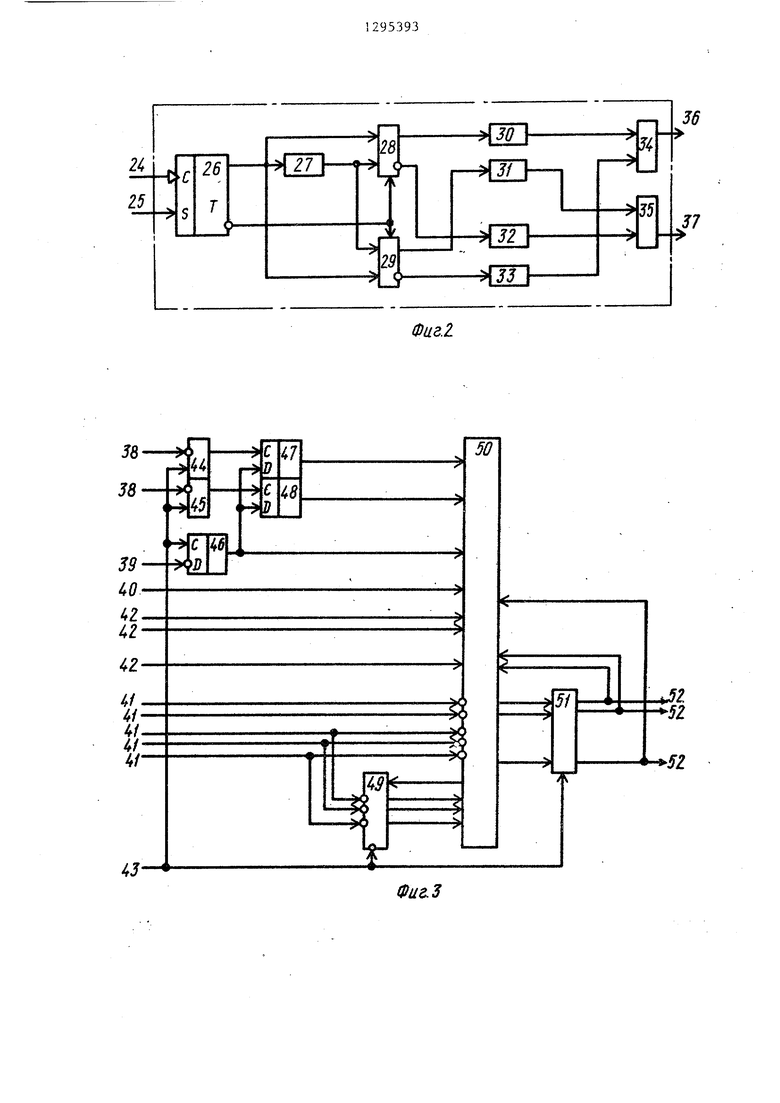

Блок синхронизации (фиг.2)имеет вход 24 зтаравления режимом, вход 25 запуска и содержит счетньй триггер 26, элемент 27 задержки, первый 28 и второй 29 мультиплексоры, первый 30, второй 31, третий 32 и четвертый 33 генераторы импульсов, первый 34 и второй 35 элементы ИЛИ и второй 36

и первый 37 выходы. I

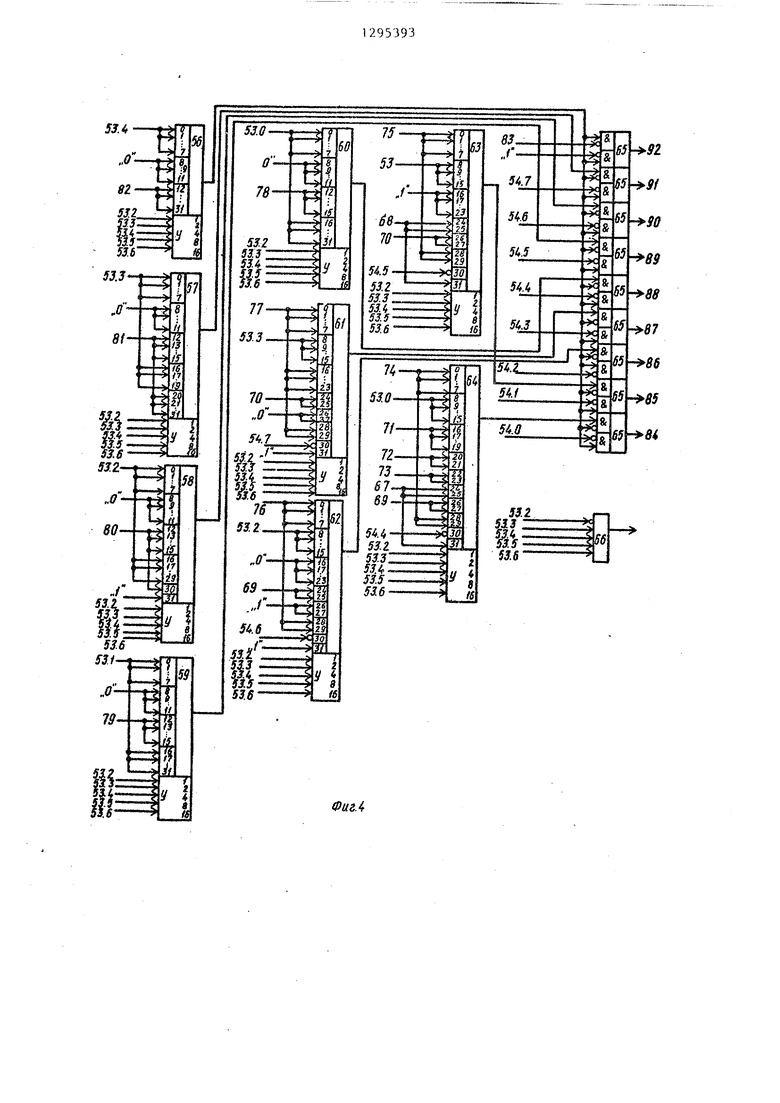

Формирователь адресов микрокоманд

(фиг.З) имеет вход 38 управления адресным переходом, вход 39 признаков перехода, вход 40 начальной.установки, первый 4 и второй 42 информационные входы, вход 43 синхронизации и содержит первый 44 и второй 45 элементы И, первый 46, второй 47 и

5

0

5

0

5

0

5

0

5

TpeTKf t 48 триггеры, регистр 4У команд, схему 50 определения адреса следующей микрокоманды, регистр 51 адреса и выход 52.

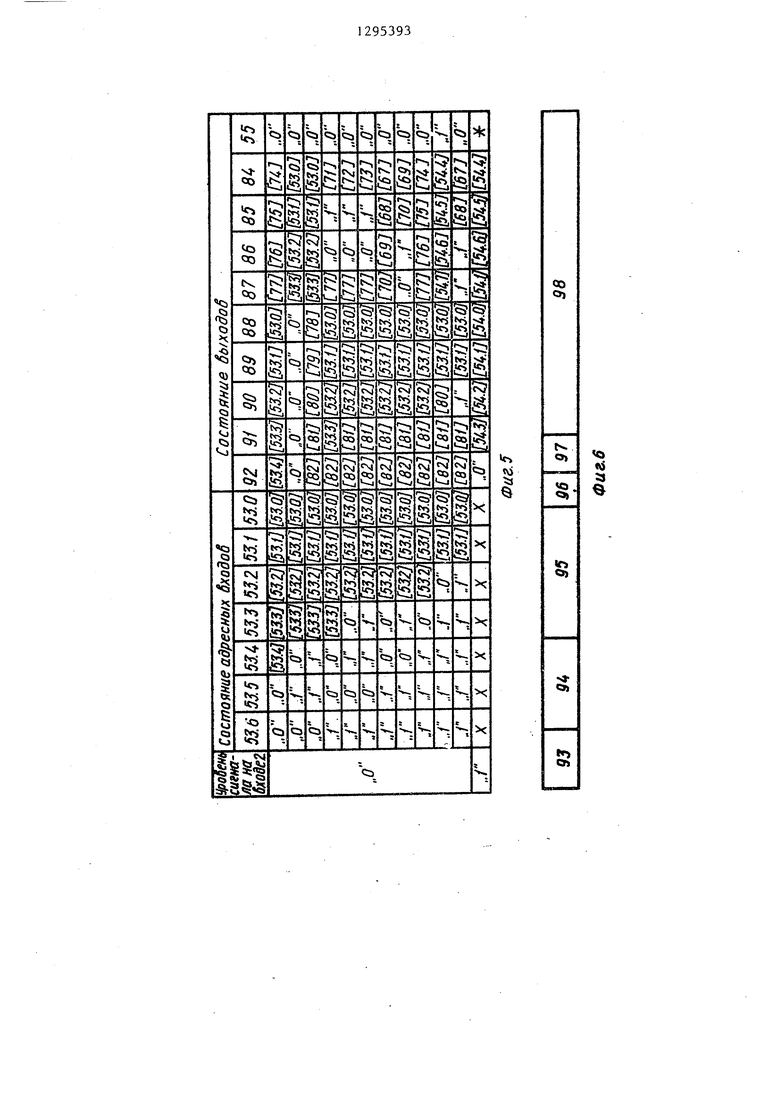

Схема определения следующего адреса (фиг. 4 и 5) имеет адресные входы 53.0 - 53.6, входы 54.0 - 54.7 команды, выход 55 записи в регистр 49 команд, с первого по девятый мультиплексоры 56-64, девять элементов 2И-ИЛИ 65, элемент И 66, входы 67 - 70, соответствующие вьгходам регистра 49 команд, входы 71 - 73 признаков, соответствздащие выходам триггеров 46 - 48, входы 74 - 82, соответствующие выходам регистра 51 адреса, вход 83 начальной установки, соответствующий входу 40 начальной установки на функциональной схеме формирователя 15 (фиг.З), и выходы 84 - 92.

В таблице (фиг.5), иллюстрирующей работу схемы 50 определения адреса следующей микрокоманды, символом о (1) обозначен уровень сигнала на адресном входе или на выходе схе- мы 50, символ X соответствует безразличному состоянию адресного входа. Символу соответствует единичный уровень в том случае, когда на адресных входах 53.3 - 53.6 схемы 50 присутствуют сигналы единичного уровня, а на адресном входе 53.2 - сиг- |нал нулевого уровня. В противном случае символу соответствует нулевой уровень. Символ . . . | обозначает уровень сигнала на соответствующем адресном входе или на выходе схемы 50, например 53.2 обозначает уровень сигнала на адресном входе 53.2.

Таблица (фиг.5) показывает зависимость состояний выходов схемы 50 определения адреса следующей микрокоманды от состояний ее адресных входов 53.0 - 53.6, состояния-сигнала на входе 83 начальной установки, состояний входов 54„О - 54.7 команды и состояний входов 67-82.

Формат микрокоманды (фиг.6) содержит шесть полей 93 - 98, Поля 93 и 94 включают группы разрядов микрокоманды, которьпу соответствзпот выходы управления адресным переходом блока 19 памяти микрокоманд, а поле 95 - группу разрядов микрокоманды, которой соответствует выход адресного поля блока 19, и предназначено дня формирования адреса следующей микро-

3

команды. Поле 96 включает разряд, котсЗрому соответствует первый разря выхода адресного поля блока 9, и предназначено для формирования адреса следующей микрокоманды, поле 97 разряд блокировки, которому соответствует выход признака режима блока 19, а поле 98 - группу разрядов, которым соответствуют выходы кода микроопераций блока 19 памяти микрокоманд.

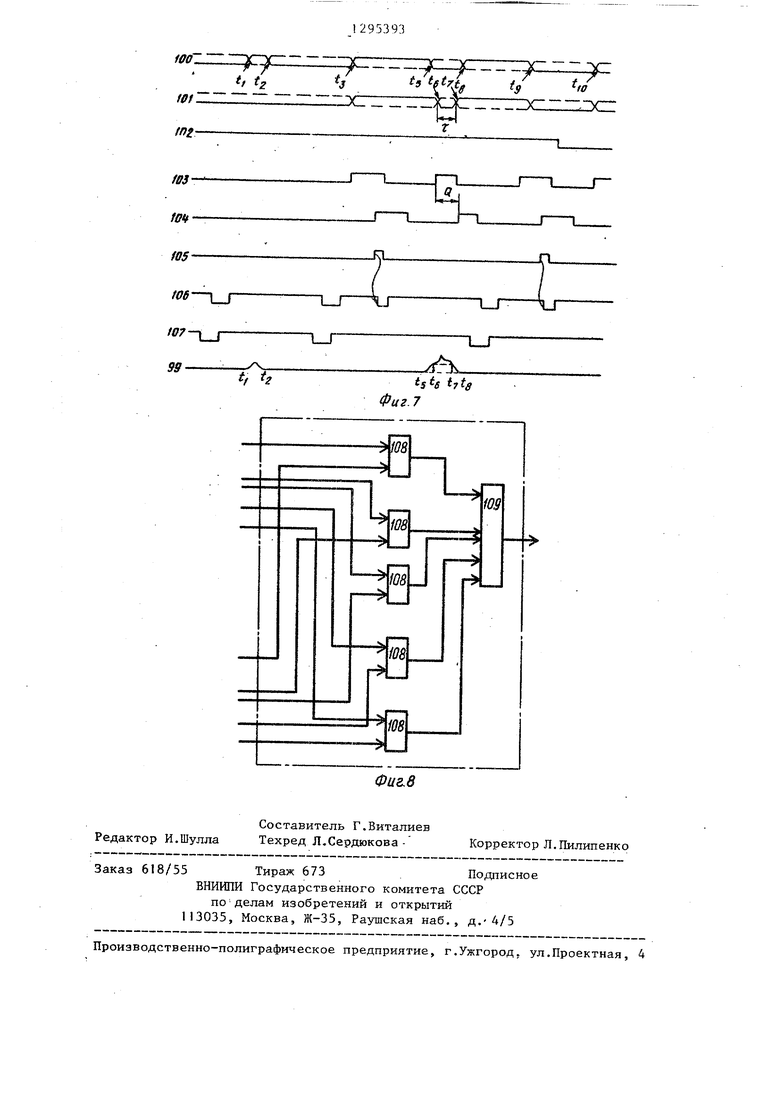

На фиг.7 приняты следующие обозначения: помеха 99, действующая на входе устройства, сигналы 100 на входах 1 - 3 устройства, сигналы 101 на выходах мультиплексоров 8 - 10, сигнал 102 на выходе признака режима блока 19, сигнал 103 на выходе схемы 16, сигнал 104 на выходе элемента 18.1, сигнал 105 на выходе элемента И 22; сигналы 106 и 107 с первого и второго выходов блока 20 синхронизации.

Схема сравнения (фиг.8) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 108 и элемент ИЛИ 109.

Устройство работает следующим образом.

Для приведения устройства в исходное состояние на вход 4 подается сигнал начальной установки, которым регистры 12 и 13 переводятся в нулевое состояние, и по которому блок 20 на- чинает вырабатьгеать серии тактовых импульсов 106 и 107. Кроме того, по сигналу начальной установки в формирователь 15 заносится первый исполнительный адрес микропрограммы, пос- тупающий на первьй информационный вход с выхода мультиплексора 10. Этот адрес появляется на выходах формирователя 15 с приходом фронта первого тактового импульса 106 с выхода блока 20.

По адресу, представленному на вы- входах формирователя ,15, происходит считьюание микрокоманды из блока 19 памяти микрокоманд.Труппы разрядов микрокоманды, которым соответствуют выходы управления адресным переходом .блока 19 (т.е. поля 93 и 94 в формате микрокоманды), предназначены для управления работой мультиплексоров 8 - 10 и формирователя 15 роответст- венно. Группа разрядов выхода адресного поля блока 19 и сигналы с выходов мультиплексоров 8 - 10 используются для формирования адреса следую

O

5

0

5

5

5

0

5

Ю

3934

щей микрокоманды. Разряд блокировки микрокоманды, которому соответствует выход управления режимом блока 19, предназначен для задания режима работы устройства во время исполнения текущей микрокоманды. В том случае, если он установлен в 1, устройству разрешается переход к следующей микрокоманде до окончания полного цикла исполнения текущей. Если же разряд установлен в о, устройство переходит к исполнению следующей микрокоманды только по окончании полного гциклЭ исполнения текущей.С соответст- вующих выходов блока 19 на выход 23 устройства передается операционная часть микрокоманды, осуществляющая воздействие на управляемую микропрограммным устройством систему.

Микрокоманды исполняются за один такт. Изменение режима работы устройства является следствием изменений уровней сигналов на его входах 1-3. Изменение уровней этих сигналов может быть вызвано воздействием помехи. Для того, чтобы исключить ложное сра- батьгоание устройства при вoздeйctвии помехи, в состав устройства вводят компараторы 5-7 уровней, а также элемент 18.1 и элемент И 22. Компараторы 5-7 уровней пропускают на свои выходы .сигналы, эдектрические уровни которых не ниже определенного порогового значения. Это пороговое значение выбирается равным активному уровню полезного сигнала, действующего на .соответствующем входе устройства. Таким образом, компараторы 5-7 уровней не пропускают в устройство помехи определенного класса, а именно: с максимальным уровнем, меньшим порогового значения.

Q

45

Элемент 18.1 и элемент И 22 устраняют влияние помехи, действующий уровень которой в течение времени с) «: 9 превьщ1ает пороговое значение соответствующего компаратора уровней. Здесь 0 - длительность задержки элемента 18.1 (фиг.7). Помеха действует на входы устройства в течение временных интервалов t,,t, t,.,tg. В течение временных интервалов ti,t, t5,t.j и t.tg уровень помехи не превосходит пороговое значение соответствующего компаратора уровней. В течение временного интервала Lt:,t735 ранного С, уровень помехи превосходит пороговое значение соответствующего компаратора уровней, и помеха проходит в устройство. Так как Q, то помеха не вызывает изменения режима работы устройства, В моменты времени t,t и t,Q происходят изменения полезных сигналов. Изменения, возникающие в моменты t и t, вызывают изменение режима работы устройства, а в момент t,o - нет, так как в последнем случае разряд блокировки блока 19 равен ,

Рассмотрим работу устройства при вьтолнении произвольной микрокоманды

По фронту тактового импульса 106 на выходах формирователя 15 формируется адрес, по которому происходит считывание микрокоманды из блока 19. В соответствии с управляющими сигналами на выходах управления адресным переходом блока 19 на выходах мультиплексоров 8-10 присутствует определенная комбинация входных сигналов .

В случае несовпадения этой комби- нации и кода, записанного в регистр 13 условий, схема 16 сравнения вырабатывает единичный уровень. Если это единичный уровень держится по времени меньше 0, то на выходе элемента И 22 присутствует нулевой уровень. Срабатывание схемы 16 вызьгоается помехой и режим работы устройства не изменяется. Если единичный уровень на выходе схемы 16 держится по вре- мени больше б, то на выходе элемента И 22 возникает единичный уровень, который поступает на вход записи регистра 13, ив него записьшается комбинация сигналов с выходов муль- типлексоров 8 - 10. Схема 16 выраба- тьтает сигнал нулевого уровня, который проходит на вход элемента И 22. Таким образом, если имеет место несовпадение кодов на первой и второй группах входов схемы 16, вызванное изменением полезных сигналов но не помехой, на выходе элемента И 22 вырабатьшается единичный импульс, длительность которого опреде ляется элементом 18.2.

Единичный импульс с выхода элемента И 22 проходит на выход элемента И 21 и поступает на вход управления режимом блока 20 -в том случае, если одновременно выполняются два условия; разряд блокировки имеет единичное значение и сигнал на выходе элемента И 17 имеет единичный уровень. Суть Первого условия в том, что микропрограммно разрешается переход к выполнению следующей микрокоманды до завершения полного цикла текущей. Второе условие означает, что оба тактовых сигнала 106 и 107 имеют единичный уровень.

Если на выходе элемента И 21 присутствует нулевой уровень, блок 20 синхронизации вырабатывает импульсы

106и 107 заданной частоты и длительности. В соответствии с кодовой комбинацией на управляющих входах мультиплексора 8 на его выходе присутствует либо один из входных сигналов, либо (при комбинации 00..О на управляющих входах) сигнал с первого разряда выхода адресного поля блока

19. Сигнал с выхода мультиплексора 8 поступает на первые информационные входы регистра I2 и мультиплексора 14. Задним фронтом тактового сигнала

107в регистр 12 осуществляется занесение данных, поступающих на его информационные входы.

Элемент ШШ 1 1 производит логическое суммирование значений сигналов на управляющих входах мультиплексора 8. Если на выходе элемента ИЛИ 11 присутствует единичньй уровень, то на выход мультршлексора 14 проходит информация с первого его входа, если на выходе элемента ИЛИ 11 - нулевой уровень, то на выход мультиплексора 14 поступает информация с второго его входа, т.е. с первого выхода регистра 12. Таким образом, до. прихода заднего фронта тактового импульса 107 в регистре 12 хранится информация об адресе текущей микрокоманды.

По единичному импульсу на входе управления режимом блок 20 формирует текущий тактовый сигнал 107 и временно снимает тактовый сигнал 106. Исполнение текущей микрокоманды окЪнче но, ее цикл был неполньм. В регистре 12 хранится информация об адресе микрокоманды, исполнявшейся до снятия тактового сигнала 106. Так как переходы по условию в устройстве осуществляются под воздействием входных сигналов устройства, то все, кроме первого, разряды регистра 12, которые не связаны с входными сигналами и поэтому не могут быть условиями перехода, используются для формирования адреса следующей микрокоманды.

Назначение элемента ИЛИ 11 и мультиплексора 14 состоит в том, чтобы пропустить на первую разрядную группу второго информационного входа формирователя 15 выбранный мультиплексо ром 8 входной сигнал, который мог измениться за время вьтолнения микрокоманды, или сигнал с первого выхода регистра 12, есЛи условием перехода не является изменение одного из вход ных сигналов, поступающих на вход мультиплексора 8.

После паузы блок 20 синхронизации вновь начинает вырабатывать тактовые импульсы 106, по переднему фронту первого из которых происходит формирование адреса следующей микрокоманды.

Рассмотрим работу блока 20 синхронизации (фиг.2).

Для приведения блока в исходное состояние на его вход 25 подается сигнал начальной установки, которым триггер 26 переводится в единичное состояние. Инверсный выход триггера 26, управляющий работой мультиплексоров 28 и 29, пропускает на их прямые выходы сигналы с их первых входов.

Генераторы 30-33 импульсов вы- рабатьшают тактовые сигнаге в том случае, если на их входах присутствуют сигналы единичного уровня. Таким образом, после появления сигнала начальной установки серии импульсов начинают вырабатьгоать генераторы 30 и 31 импульсов, так как на их входах присутствуют сигналы единичного уровня. Так как входы генераторов 32 и 33 импульсов связаны с инверсными выходами мультиплексоров 28 и 29 сот ответственно, на которых присутствуют сигналы нулевого уровня,то после сигнала начальной установки эти генераторы пассивны, а на их выходах - сигнатш нулевого уровня.

Сигналы с выходов генераторов 30 и 33, а также сигналы с выходов генераторов 31 и 32 логически сумми

Микропрограммное устройство уп ления , содержащее два мультиплекс условий, мультиплексор команды, м типлексор адреса, регистр адреса, регистр условий, формирователь ад сов микрокоманд, блок памяти микр команд, элемент ИЛИ, два элемента первый элемент задержки, схему ср 40 нения и блок синхронизации, приче управляющие входы первого и второ мультиплексоров условий, мультипл сора команды и вход управления пе ходом формирователя адресов микро манд подключены к одновременным в ходам прля управления адресом бло памяти микрокоманд, адресный вход торого соединен с выходом формиро теля адресов микрокоманд, первый и

руются на элeмeнtax ИЛИ 34 и 35 соот- формационный вход, вход признаков ветственно. С выходов элементов ИЛИ перехода, первая разрядная группа 34 и 35 сигналы передаются на выходы

второго информационного входа и ра рядные группы с второй по п-ю втор го информационного входа которого (где п - число разрядов адресного поля блока памяти микрокоманд) под ключегел соответственно к выходу мультиплексора команды, выходу вто рого мультиплексора условий, выход

36 и 37 блока соответственно.

В таком режиме блок 20 работает до появления импульса на входе 24 блока. С входа 24 блока импульс поступает на счетный вход триггера 26, в результате триггер 26 перебрасывается в нулевое состояние, тем са5

0

мым открывая передачу с вторых входов мультиплексоров 28 и 29 на их выходы. В итоге на инверсном выходе мультиплексора 29 появляется сигнал единичного уровня и с задержкой, определяемой элементом 27, после того появляется сигнал единичного уровня на инверсном выходе мультиплексора 28. Таким образом, с приходом первого единичного импульса на вход 24 блока в работе блока 20 синхронизации происходят, следующие изменения: прекращает вьфабатывать тактовые сигналы генератор 31 импульсов, начинает вы- рабатьгеать тактовые сигналы генератор 33 импульсов, затем с задержкой прекращает вырабатывать импульсы ге-: нератор 30 импульсов и начинает вырабатывать импульсы генератор 32 импульсов . I

В этом режиме блок 20 синхронизации работает до появления на его входе 24 следующего импульса. Далее блок 5 20 функционирует аналогично указанному. Сигналы с выходов всех генераторов 30 - 33 импульсов имеют ковые параметры.

ЗОФормула изобретения

Микропрограммное устройство управления , содержащее два мультиплексора условий, мультиплексор команды, мультиплексор адреса, регистр адреса, регистр условий, формирователь адресов микрокоманд, блок памяти микрокоманд, элемент ИЛИ, два элемента И, первый элемент задержки, схему срав- нения и блок синхронизации, причем управляющие входы первого и второго мультиплексоров условий, мультиплексора команды и вход управления переходом формирователя адресов микрокоманд подключены к одновременным выходам прля управления адресом блока памяти микрокоманд, адресный вход которого соединен с выходом формирователя адресов микрокоманд, первый ин

формационный вход, вход признаков перехода, первая разрядная группа

формационный вход, вход признаков перехода, первая разрядная группа

второго информационного входа и разрядные группы с второй по п-ю второго информационного входа которого (где п - число разрядов адресного поля блока памяти микрокоманд) под- ключегел соответственно к выходу мультиплексора команды, выходу второго мультиплексора условий, выходу .

91

мультиплексора адреса и выходу регистра адреса, управляющий вход мультиплексора аДреса соединен с выходом элемента ИЛИ, входы которого подключены к выходу поля управления адресом блока памяти микрокоманд, первая разрядная группа информационного входа регистра адреса соединена с выходом первого мультиплексора условий и первым входом мультиплексора адреса, второй вход которого соедине с выходом регистра адреса, вход синхронизации формирователя адресов микрокоманд подключен к первому выходу блока синхронизации и первому входу первого элемента И, второй вхоД которого соединен с вторым выходом блока синхронизации и входом синхронизации регистра адреса, разрядные группы с второй по п-ю информационного входа которого подключены соответственно к разрядньи группам с второго по п-ю выхода адресного поля блока памяти микрокоманд, первая разрядная группа выхода адресного поля блока памяти микропрограмм соединена с первым информационным входом первого мультиплексора условий, выход регистра условий подключен к первому входу схемы сравнения, выход которой соединен с входом первого элемента задержки, выход и первый вход второго злемента И подключен Соответственно к тактовому входу блока синхронизации и выходу признака блока памяти микрокоманд, второй вход второго элемента И соединен с выходом первого элемента И, Выход первого мультиплексора условий подключен к первому информационному входу регистра условий и первой разрядной группе второго входа схемы сравнения, вторая разрядная группа второго входа которой соединена с

93И)

вторым информадиокиым «ходом per Vicr- ра условий и выходом второго мультиплексора условий, выход мультиплексора команды подключен к третьему информационному входу регистра условий и третьей разрядной группе второго входа cxeNttr сравнения, входы начальной установки формирователя адресов микрокоманд, регистра адреса, регистра: условий и вход запуска блока синхронизации соединены с входом начальной установки устройства, а группа выходов коДа микрооперации блока памяти микрокоманд является выходом микрооперации устройства, отличающееся тем, что, с целью повьшения надежности работы устройства за счет стробирования уровней входных сигналов и их длительности, оно содержит три компаратора уровней, третий элемент И и второй элемент задержки, причем вход и выход первого компаратора уровней подключены к первому входу логических условий устройства и информационному входу первого мультиплексора условий, вход и выход второго компаратора уровней соединены соответственно с вторым входом логических условий устройства и информационным входом второго мультиплексора условий, вход и выход третьего компаратора уровней подключены соответственно к входу кода команды устройства и информационному входу мультиплексора команд, выход схемы сравнения соединен с первым входом третьего элемента И, второй вход которого подключен к выходу первого элемента задержки, выход третьего элемента И соединен с третьим входом второго элемента И и входом второго элемента задержки, выход которого подключен к входу син- хроиизации регистра условий.

36

37

Фа.2.

Фиг.3

N О

45 «S

;э %

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1260953A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1176328A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, а также терминальной аппаратуре. Целью изобретения является повышение надежности работы устройства за счет строби- рования уровней входных сигналов и их длительности. С этой целью в устройство, содержащее два мультиплексора 8 и 9 условий, мультиплексор 10 команды, мультиплексор 14 адреса, регистр 12 адреса, регистр 13 условий, формирователь 15 адресов микгро- команд, блок 19 памяти микрокоманд, элемент ИЛИ 1I, два элемента И 2I и 22, элементы 18.1 и 18.2 задержки, схему 16 сравнения и блок 20 синхронизации, введены три компаратора уровней, третий элемент И и второй - элемент задержки. 8 ил. S . (Л с

| Микропрограммное устройство управления | 1976 |

|

SU640294A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1176328A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-09-06—Подача