выходкоторого соединен с вторым входом второго элемента И и с входом синхронизации формирователя адресов микрокоманд, выход первого элемента И соединен с входом управления режимом блока синхронизации, выход первого мультиплексора соединен с первыми информационными входами регистра адреса и четвертого мультиплексора, второй информационный вход которого соединен с первым выходом регистра адреса, остальные выходы которого соединены с второго по П-й информационными входами второй группы формирователя адресов микрокоманд (где п- разрядность адреса блока памяти микрокомандJ, первьй информационный вход второй группы Которого соединен с выходом чет-вертого мультиплексора, с второго по п-й информационные входы регистра адреса соединены соответственно со второго по п-й адресные выходы блока памяти микрокоманд.

2. Устройство по п. 1, о т л ичающееся тем, что блок синхронизации содержит счетный триггер, элемент задержки, первый и второй мультиплексоры, первый, второй, третий и четвертый генераторы импульсов и первый и второй элементы ИЛИ, причем счетный вход счетного триггера является входом управления режимом блока, единичный выход счетного триггера подключен к первому информационному входу первого мультиплексора, к второму информационному входу второго мультиплексора и через элемент задержки соединен с вторым информационным входом первого мультиплексора и с первым информационным входом второго мультиплексора, инверсный выход которого соединен с входом запуска четвертого генератора импульсов, прямой выход второго мультиплексора подключен к входу запуска второго генератора импульсов, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является вторым выходом блока, второй.вход второго элемента ИЛИ подключен к выходу третьего генератора импульсов, вход запуска которого соединен с инверсным выходом первого мультиплексора, прямой выход которого подсоединен к входу запуска первого генератора импульсов, выход которого.подключен к первому входу первого элемента ИЛИ, выход которого является первым выходом блока, второй вход первого элемента ИЛИ подсоединен к выходу четвертого генератора импульсов, нулевой выход счетного триггера соединен с управляющими входами первого и второго мультиплексоров, вход установки в 1 счетного триггера является входом запуска блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1295393A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1260953A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

1. МИКРОПРОГРАММНОЕ УСТ- .РОЙСТВО УПРАВЛЕНИЯ, содержащее первьш, второй и третий мультиплексоры, блок памяти микрокоманд, формирователь адресов микрокоманд, причем управляющие входы мультиплексоров и входы управления адресным переходом формирователя адресов микрокоманд прдключены к соответствующим выходам поля управления адресом блока памяти микрокоманд, адресные входы которого соединены с выходами формирователя адресов микрокоманд, первая группа информационных входов которого соединена с группой выходов третьего мультиплексора, выход второго мультиплексора подключен к входу признаков перехода формирователя адресов микрокоманд, вход начальной установки которого подключен к входу начальной установки устройства, первый адресный вьгход блока памяти микрокоманд соединен с первым информационным входом первого мультиплексора, остапьны.е информационные входы которого являются первой группой входов SKSJlBOiiitiA условий устройства, группы информационных входов второго и третьего мультиплексоров являются соответственно второй группой входов условий устройства и группой входов кода команды устройства, группа выходов кода микрооперации блока памяти миК15окоманд является группой выходов устройства, отличающееся тем, что, с целью повЕлпения быстродействия устройства за счет сокращения времени реакции на изменение входных условий, оно дополнительно содержит четвертый мультиплексор, i регистр адреса, регистр условий, схему сравнения, первый и второй эле(Л менты И, элемент задержки, элемент С .ИЛИ и блок синхронизации, причем входы начальной установки регистра адреса, регистра условий и вход запуйка блока синхронизации подключены к входу начальной установки устройства, выходы первого, второго и М третьего мультиплексоров подключеОд ны к группе информационных входов 00 регистра условий и к первой групiNd пе входов схемы сравнения, вторая 00 группа входов схемы сравнения соединена с группой выходов регистра условий, вход записи которого соединен через элемент задержки с выходом схемы сравнения и с первым входом первого элемента И, второй и третий входы которого соединены соответственно с выходом признака режима блока памяти микрокоманд и с выходом второго элемента И, первый вход которого соединен с входом записи регистра адреса и с первым выходом блока синхронизации, второй

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, а также терминальной аппаратуре.

Целью изобретения является повышение быстродействия за счет сокращения времени реакции на изменение входных условий.

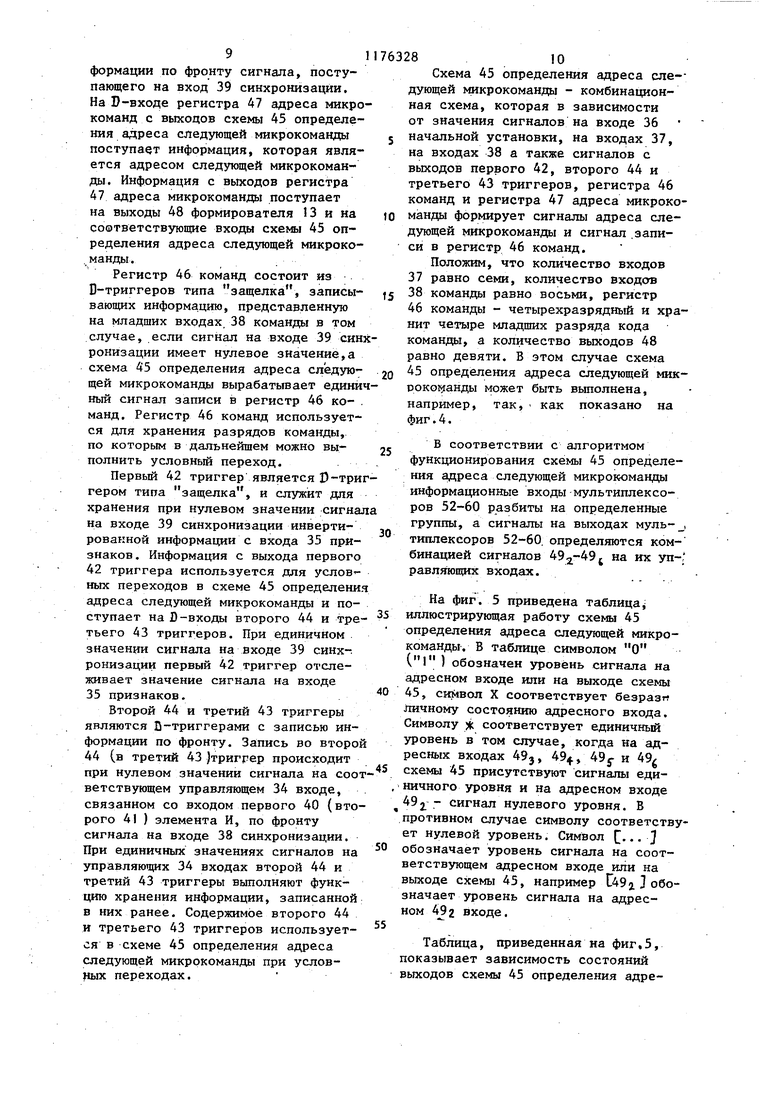

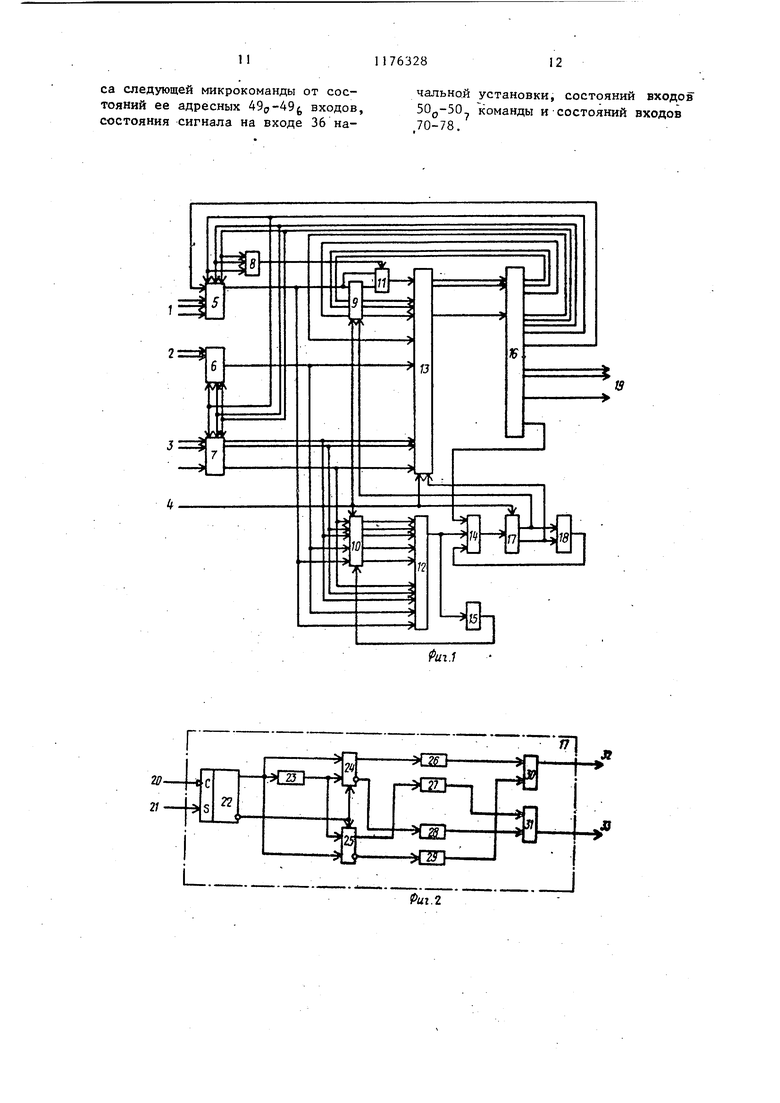

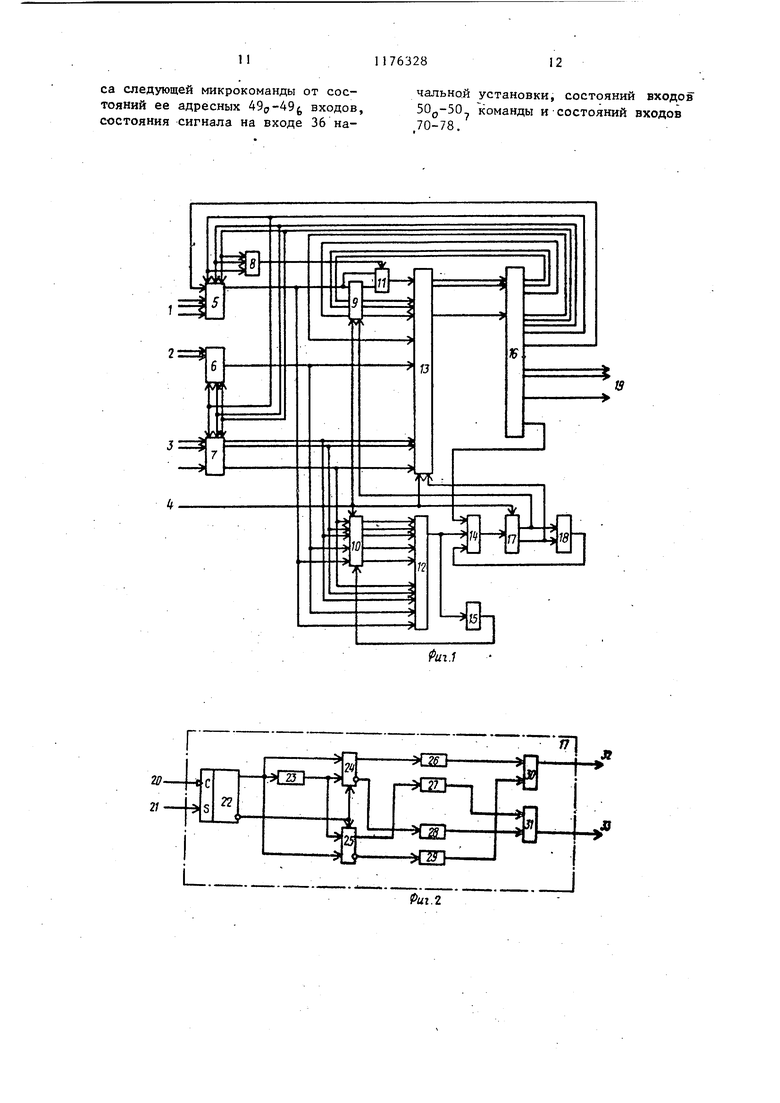

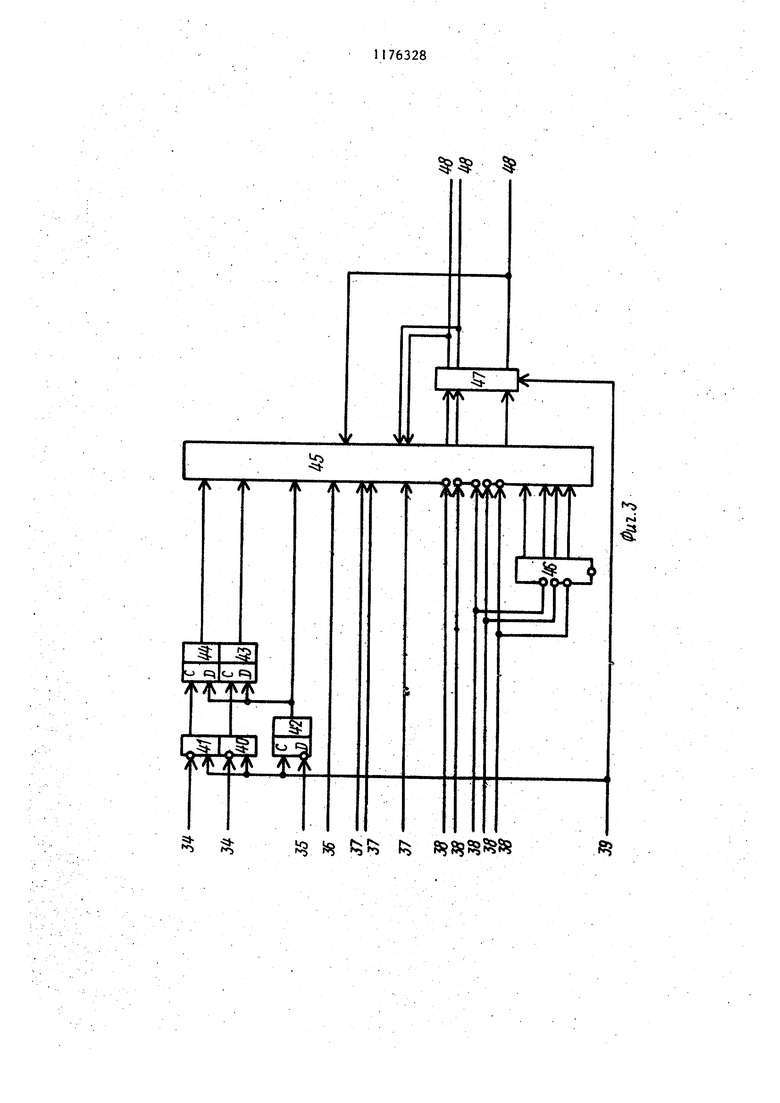

На фиг. 1 изображена функциональная схема микропрограммного устройства управления; на фиг. 2 - функцинальная схема блока синхронизации; на фиг. 3 - функциональная схема формирования адресов микрокоманд; на фиг. 4 - пример технической реализации схемы определения адреса следующей микрокоманды; на фиг. 5 таблица истинности схемы определения адреса следующей микрокоманды; на фиг. 6 - формат микрокоманды; на фиг. 7 - временные диаграммы, иллюстрирующие функционирование устройства.

Микропрограммное устройство управления содержит первую 1 и вторую 2 группы входов условий, группу 3 входов кода команды, вход 4 начальной установки, первый 5,второй 6 и третий 7 мультиплексоры, элемент ШШ 8, регистр 9 адреса, регистр 10 условий, четвертый 11 мультиплексор.

схему 12 сравнения, формирователь 13 адресов микрокоманд, первь й элемент И 14, элемент 15 задержки, бло ч 16 памяти микрокоманд, блок 17.синхронизации, второй элемент И 18, тру пу IS Выходов.

Блок синхронизации содержит вход 20 управления режимом,вход 21 запуска, счетный триггер 22, элемент 23 задержки, первый 24 и второй 25 мультиплексоры, первый 26, второй 27, третий 28 и четвертый 29 генераторы импульсов; первый 30 и второй 31 элементы ИЛИ и первый 32 и второй 33 выходы.

Формирователь адресов микрокоман содержит входы 34 управления адресным переходом, вход 35 признака перехода, вход 36 начальной установки первую 37 и вторую 38 группы информационных входов, вход 39 синхронизации, первый 40 и второй 41 элементы И, первый 42, третий 43 и второй 44 триггеры, блок 45 определения адреса следующей микрокоманды, регистр 46 команд, регистр 47 адреса и группу 48 выходов.

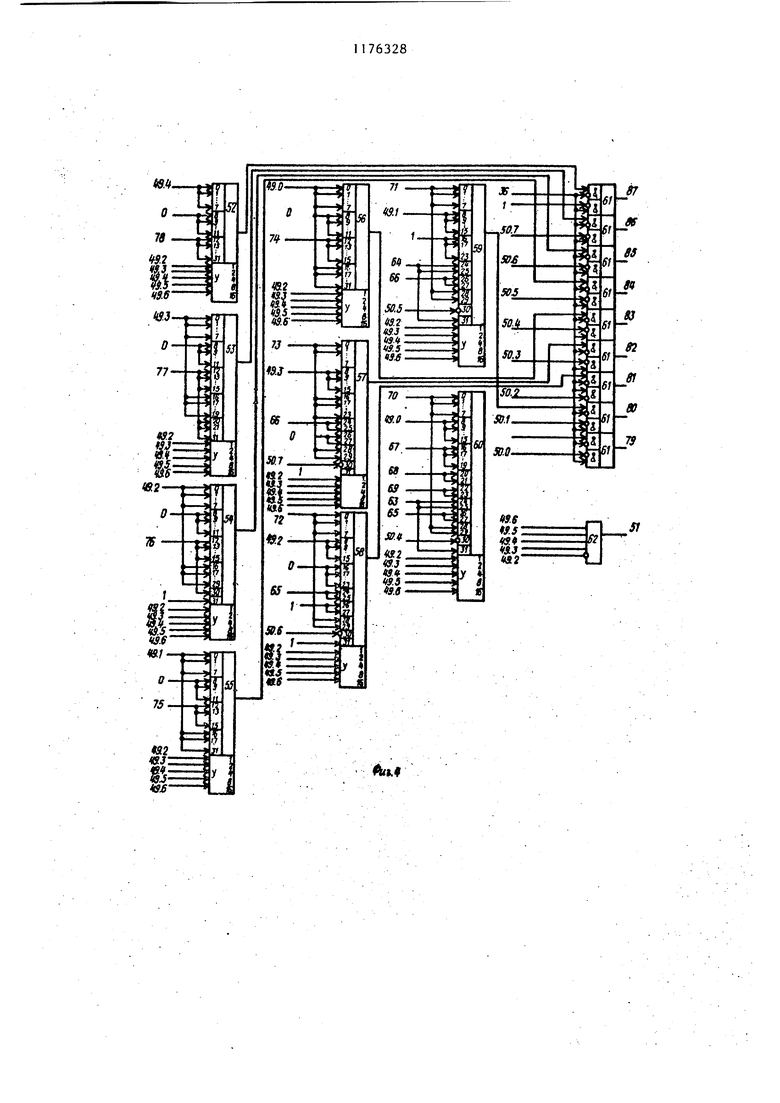

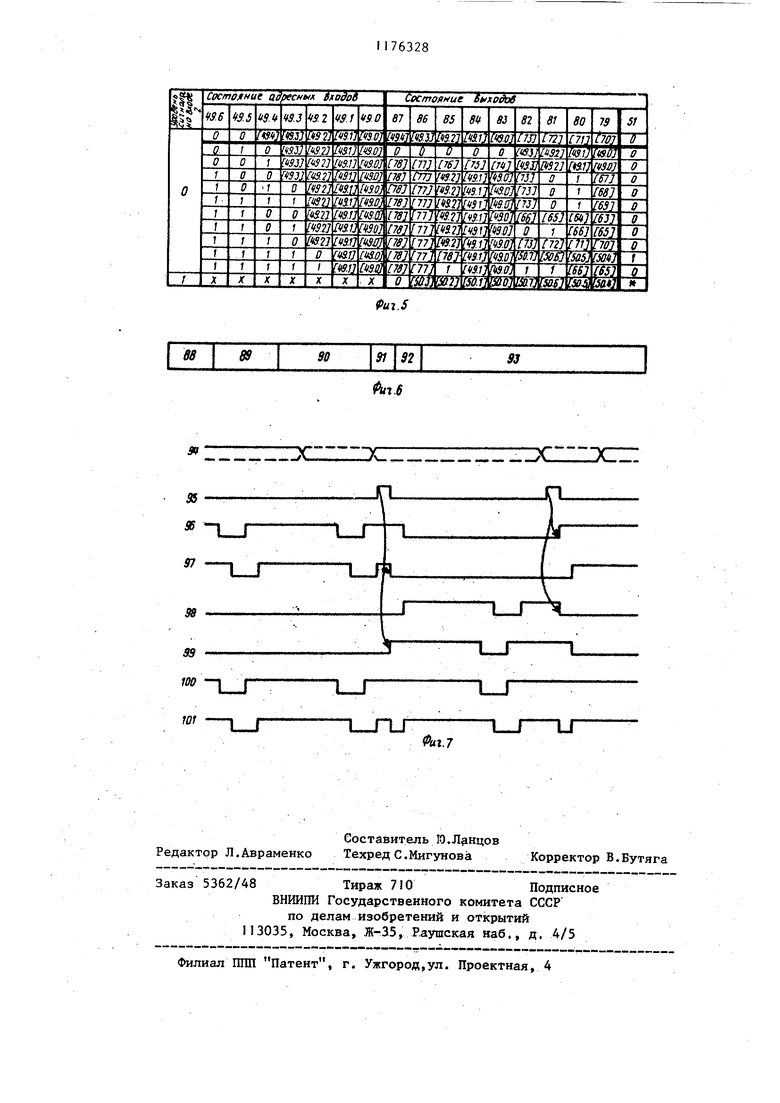

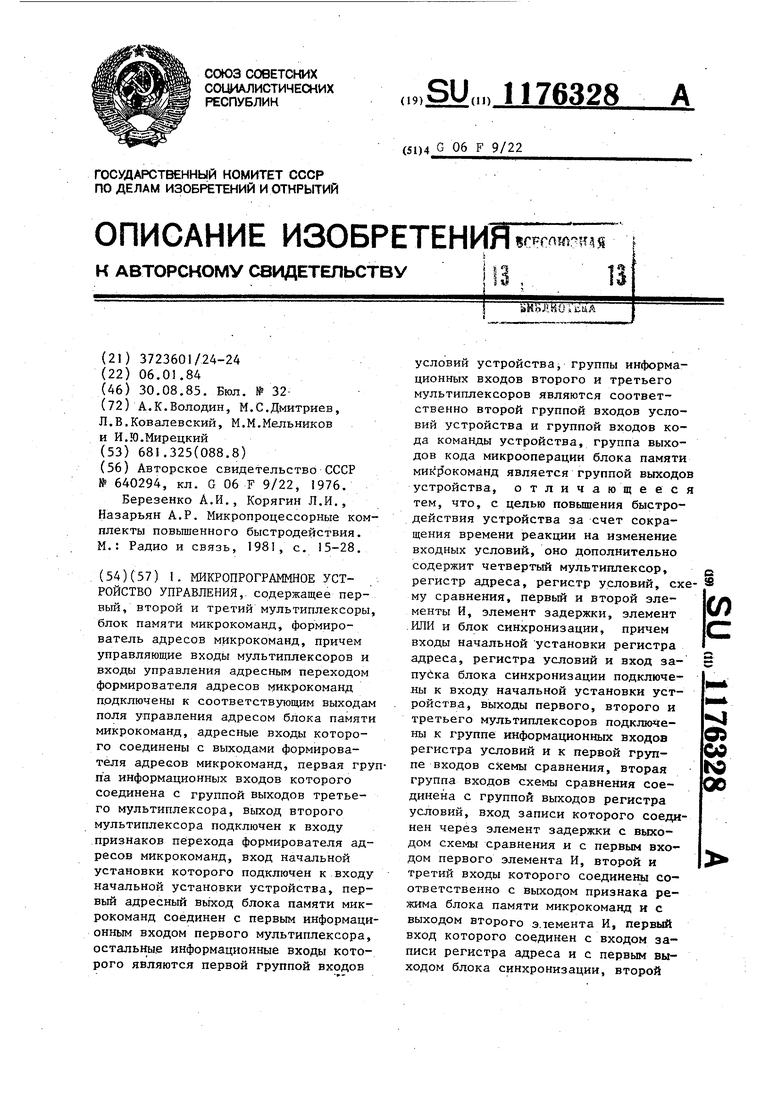

Блок определения следующего адреса содержит адресные входы 49Q49, входы команды, выход 51 записи в регистр 46 команд, с первого 52 по девятый 60 мультиплексоры, девять элементов 2И-ИЛИ 61, элемент И 62, входы 63, 64, 65 и 66, соответствующие выходам регистра 46 команд, входзы 67, 68, 69 признаков, соответствующие выходам триггеров 42-44, входы 70-78, соответствзтошие выходам регистра 47 адреса, выходы 79-87. Формат микрокоманды содержит 6 полей 88-93. Поля 88 и 89 включают группы разрядов микрокоманды, которым соответствуют выходы управления адресным переходом блока 16 памяти микрокоманд.

Поле 90 включает группу разрядов микрокоманды, которой соответствует труппа адресных выходов блока 16 и предназначено для формирования адреса следующей микрокоманды.

Поле 91 включает разряд,которому соответствует первый адресный выход блока 16, и предназначено для формирования адреса следующей микрокоманды. .

Поле 92 включает разряд блокировки, которому соответствует выход признака режима блока 16.

Поле 93 включает группу разрядов, которым соответствуют выходы кода микроопераций блока 16 памяти микрокоманд.

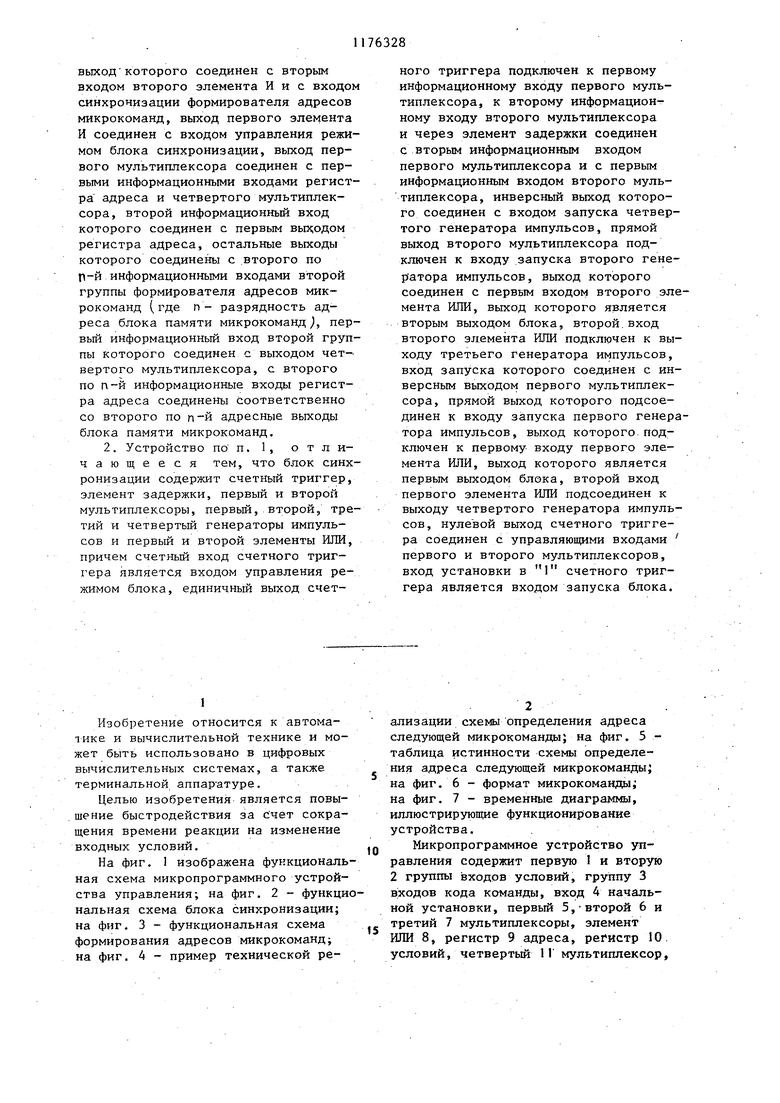

На фиг. 7 приняты следующие обозначения: 94 - сигналы на входах 1,-2,3 устройства; 95 - сигнал с выхода элемента И 14, 96-99 - сигналы с выходов первого 26, второго 27, третьего 28 и четвертого 29 генераторов импульсов; 100 и 101 - сигналы с первого и второго выходов блока синхронизации.

Устройство работает следующим образом.

Для приведения устройства в исходное состояние на его вход 4 подается сигнал начальной установки, которым регистры 9 адреса и 10 условий переводятся в нулевое состояние , и по которому блок 17 синхронизации начинает вырабатывать серии тактовых импульсов 100 и 101. Кроме того, по сигналу начальной установки в формирователь 13 адресов микрокоманд заносится первый исполнительный адрес микропрограммы, поступаюпщй на первые информационные входы с выходом мультиплексора 5. Этот адрес появляется на выходах формирователя 13 с приходом фронта -первого тактового импульса 101 с выхода блока 17 стгхронизации.

По адресу, представленному на выходах формирователя 13, происходит считывание микрокоманды из блока I6 памяти микрокоманд. Группы разрядов микрокоманды, которым соответствуют выходы управления адресным переходом блока 16 памяти микрокоманд, предназначены для управления работой первого 5, второго 6 и третьего 7 мультиплексоров и формирователя 13 соответственно. Группа адресных выходов блока 16 памяти микрокоманд и сигналы с выходов первого 5, второго 6 и третьего 7 мультиплексоров используются для формирования адреса следующей микрокоманды. Разряд блокировки микрокоманды, которому соответствует выход управления режимом блока 16 памяти микрокоманд предназначен для задания режима работы устройства вд время исполнения .текущей микрокоманды. В том случае, если он установлен в едницу, устройству разрешен переход к следующей микрокоманде до окончания полного цикла исполнения текущей. Еели же разряд установлен в нуль, устройство переходит к исполнению следующей микрокоманды только по окончании полного цикла исполнения текущей С соответствующих выходов блока 16 памяти микрокоманд на выходы I9 устройства передается операционная часть микрокоманды, осуществляющая воздействие на управляемую микропрограммным устройством систему.

Микрокоманды исполняются за один такт.

Рассмотрим работу устройства при выполнении произвольной микрокоманды

По фронту тактового импульса 101 на выходах формирователя 13 формируется адрес, по которому происходит считывание микрокоманды из блока 16 памяти микрокоманд. В соответствии с управляющими сигналами на выходах управления адресным переходом блока 16 .памяти микрокоманд на выходах первого 5, второго & и третьего 7 мультиплексоров присутствует определенная комби нация входных сигналов. В случае несовпадения этой комбинации и кода, записанного в регистр 10 условий, схема 12 сравнения вырабатывает единичный уровень, который с задержкой, определяемой элементом 15 задержки, поступает на вход записи регистра 10 условий, и в. него записывается комбинация сигналов с выходов первого 5, второго 6 и третьего 7 мультиплексоров. Схема 12 сравнения вырабатывает сигнал нулевого уровня. Таким образом, если имело место несовпадение кодов на первой и второй группах входов схемы 12 сравнения, она вырабатывает единичный импульс, длительность которого определяется элементом 15 задержки.

Единичный импульс с выхода схемы I2 сравнения проходит на выход элемента I4 И и поступает на вход управления режимом блока 17 синхронизации в том случае, если одновременно выполняются два условия: разряд блокировки микрокоманды имеет единичное значение, и сигцал на выходе элемента 18 И имеет единичный уровень. Суть первого условия в том, что микропрограммно разрешеи переход к выполнению следующей микрокоманды до завершения полного цикла текущей . Второе, условие означает, что оба тактовых сигнала 100 и 101 имеют единичный уровень

Если на выходе элемента 14 И присутствует нулевой уровень, блок 17 синхронизации вырабатывает импульсы 100 и 101 заданной частоты и длительности. В соответствии с кодовой комбинацией на управляющих входах первого 5 мультиплексора, на его выходе присутствует либо один их входных сигналов, либо (при комбинации 00...О на управляющ входах ) сигнал с первого адресного выхода блока 16 памяти микрокоманд. Сигнал с выхода первого 5 мультиплексора поступает на первые информционные входы регистра 9 адреса и четвертого 11 мультиплексора соответственно. Задним фронтом тактового сигнала I00 в регистр 9 адреса осуществляется занесение данных, представленных на его информационных входах.

Элемент 8 ИЛИ производит логическое суммирование значений сигналов на управляющих входах первого

5мультиплексора. Если на выходе элемента 8 ИЛИ присутствует единичный уровень, то на выход четвертого 11 мультиплексора проходит информация с первого его входа, если же нулевой уровень, то на выход четвертого I1 мультиплексора поступает информация со второго его входа, т.е. с первого выхода регистра

9 адреса.

Таким образом, до прихода заднег фронта тактового импульса 100 в регистре 9 адреса хранится информация

06адресе текущей микрокоманды.

По единичному импульсу на входе управления режимом блок 17 синхронизации формирует текущий тактовый сигнал 100 и временно снимает тактовый сигнал 101. Исполнение текуще микрокоманды окончено, ее цикл бьш неполным. В регистре 9 адреса хранися информация об адресе микрокоманды, исполнявшейся до снятия тактового сигнала 101. Так как переходы по условию в предлагаемом устройстве осуществляются под воздействием входных сигналов устройства, то все, кроме первого, разряды регистра 9 адреса, которые не связаны с входными сигналами и поэтому не могут быть условиями перехода, используются для формирования адреса следукице микрокоманды. Назначение элемента 8 ИЛИ и четвертого 1 I мультиплексора том, чтобы пропустить на первый ийформационный вход второй группы , формирователя 13 выбранный первым мультиплексором входной сигнал, который мог измениться за время выполнения микрокоманды, или сигнал с первого выхода регистра адреса, если условием перехода не является из менение одного из входных сигналов, поступающих на вход первого 5 мультиплексора. После паузы блок 17 синхронизаци вновь начинает выраба1ъшать тактовые импульсы 101, по переднему фрон ту.первого из которых происходит формирование адреса следугащей микро команды. Рассмотрим работу блока 17 синхронизации фиг. 2). Для приведения блока в исходное состояние на его вход 21 подается сигнал начальной установки, которым счетный триггер 22 переводится в ед ничное состояние. Нулевой выход сче ного триггера 22, управляющий работой первого 24 и второго 25 мультиплексоров, пропускает на их единичн выходы сигналы с их первых входов. Первый 26, второй 27, третий 28 и четвертый 29 генераторы импульсов вырабатывают тактовые сигналы в том случае, если на их входах присутствуют сигналы единичного уровня. Таким образом, после появления сигнала начальной установки серии импульсов начинают вырабатывать пер вый 26 и второй 27 генераторы импульсов, так как на их входах присутствуют сигналы единичного уровня Так как входы третьего 28 и четвертого 29 генераторов импульсов связаны с нулевыми выходами первого 24 и второго 25 мультиплексоров соответственно, на которых присутствуют сигнгшы нулевого уровня, то после сигнала начальной установки эти генераторы пассивны, а на их выходах - сигналы нулевого уровня. Сигналы с выходов первого 26 и четвертого 29, а также сигналы с выходов второго 27 и третьего 28 генераторов импульсов логически сум мируются на первом 30 и..втором 31 элементах ИЛИ соответственно. С 1вых дов первого 30 и второго 31 элементов ИЛИ сигналы передаются на выходы 32 и 33 блока соответственно. В таком режиме блок 17 синхрони- . зации работает до появления импульса на .входе 20 блока. С входа 20 блока импульс поступает на счетный вход счетного 22 триггера, в результате чего триггер перебрасьюается в нулевое состояние, тем самьо4 открывая передачу со вторых входов первого 24 и второго 25 муяьтиппек соров на нх выходы. В итоге на нулевом выходе второго 25 мультиплексора появляется сигнал единичного уровня, и с задержкой, определяемой элементом 23 задержки, после этого появляется сигнал единичного уровня на нулевом выходе первого 24 мультиплексора. Таким образом, с приходом первого единичного импульса на вход 20 блока, в работе блока I7 синхронизации происходят следующие изменения: прекращает вырабатывать тактовые сигналы второй 27 генератор импульсов и начинает вырабатывать тактовые сигналы четвертый 29 генератор импульсов, а затем с задержкой прекращает вырабатывать импульсы первый. |26 генератор импульсов и начинает вырабатывать импульсы третий 28 генератор импульсов. В этом режиме блок 17 синхронизации работает до появления на его входе 20 следующего импульса. Далее блок 17 синхронизации функционирует аналогично вышеописанному. Сигналы с выходоя всех генераторов 26-29 импульсов имеют одинаковые параметры. Формирователь 13 адресов микрокоманд может быть выполнен, например, как показано на фиг. 3. , Формирователь 13 выполняет следуюпще операции: прием начального адреса микропрограмм со входов 38 комагзды, управление последовательностью выбора микрокоманд из блока 16 памяти микрокоманд, хранение и анализ кода команды на регистре 46 команд, хранение двух признаков в триггерах 43 и 44 и условный переход по ним, непосредственную адресацию к блоку 16 памяти микрокоманд. Регистр 47 адреса микрокоманд состоит из D-триггеров с записью информации по фронту сигнала, поступающего на вход 39 синхронизации. На D-входе регистра 47 адреса микро команд с вькодов схемы 45 определения адреса следующей микрокоманды поступает информация, которая является адресом следующей микрокоманды. Информация с выходов регистра 47 адреса микрокоманды поступает на выходы 48 формирователя 13 и на соответствующие входы схемы 45 определения адреса следующей микрокоманды. Регистр 46 команд состоит из D-триггеров типа защелка, записывающих информацию, представленную на младших входах 38 команды в том случае, если сигнал на входе 39 син ронизации имеет нулевое значение,а схема 45 определения адреса следующей микрокоманды вырабатывает едини ный сигнал записи в регистр 46 команд. Регистр 46 команд используется для хранения разрядов команды, по которым в дальнейшем можно вы- полнить условный переход. Первый 42 триггер является J)-три гером типа защелка, и служит для хранения при нулевом значении сигна на входе 39 синхронизации инвертированной информации с входа 35 признаков. Информация с выхода первого 42 триггера используется для услов ных переходов в схеме 45 определени адреса следующей микрокоманды и поступает на D-входы второго 44 и тре тьего 43 триггеров. При единичном значении сигнала на входе 39 синх-. ронизации первый 42 триггер отслеживает значение сигнала на входе 35 признаков. Второй 44 и третий 43 триггеры являются D-триггерами с записью информации по фронту. Запись во второ 44 (в третий 43 )триггер происходит при нулевом значении сигнала на соо ветствующем управляющем 34 входе, связанном со входом первого 40 (вто рого 41 ) элемента И, по фронту сигнала на входе 38 синхронизации. При единичных значениях сигналов на управляющих 34 входах второй 44 и третий 43 триггеры выполняют функцию хранения информации, записанной в них ранее. Содержимое второго 44 и третьего 43 триггеров используется в схеме 45 определения адреса следующей микрокоманды при условных переходах. Схема 45 определения адреса еле-дующей микрокоманды - комбинационная схема, которая в зависимости от значения сигналов на входе 36 начальной установки, на входах 37, на входах 38 а также сигналов с выходов первого 42, второго 44 и третьего 43 триггеров, регистра 46 команд и регистра 47 адреса микрокоманды формирует сигналы адреса следующей микрокоманды и сигнал .записи в регистр 46 команд. Положим, что количество входов 37равно семи, количество входов 38команды равно восьми, регистр 46 команды - четырехразрядный и хранит четыре младших разряда кода команды, а количество выходов 48 равно девяти. В этом случае схема 45 определения адреса следующей микроко1;1анды может быть вьшолнена, например, так, как показано на фиг.4. В соответствии с алгоритмом функционирования схемы 45 определения адреса следующей микрокоманды информационные входы мультиплексоров 52-60 разбиты на определенные группы, а сигналы на выходах муль-, типлексоров 52-60. определяются комбинацией сигналов на их уп-, равлятощих входах. На фиг. 5 приведена таблицаj иллюстрирующая работу схемы 45 определения адреса следующей микрокоманды. В таблице символом О (1 ) обозначен уровень сигнала на адресном входе или на выходе схемы 45, символ X соответствует безразгг Личному состоянию адресного входа. Символу yif. соответствует единичный уровень в том случае, когда на адресных входах 49з, 494, 495- и 49 схемы 45 присутствуют сигналы единичного уровня и на адресном входе 49 - сигнал нулевого уровня. В противном случае символу соответствует нулевой уровень. Символ С-J обозначает уровень сигнала на соответствующем адресном входе или на выходе схемы 45, например C495i J обозначает уровень сигнала на адресном входе. Таблица, приведенная на фиг,5, показывает зависимость состояний выходов схемы 45 определения адреса следующей микрокоманды от состояний ее адресных 49о-49(, входов, состояния сигнала на входе 36 начальной установки, состояний входов 50р-50 команды и-состояний входов

.70-78.

Риг.г

s

DL.

| Микропрограммное устройство управления | 1976 |

|

SU640294A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Березенко А.И., Корягин Л.И., Назарьян А.Р | |||

| Микропроцессорные комплекты повьшенного быстродействия | |||

| М.: Радио и связь, 1981, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1985-08-30—Публикация

1984-01-06—Подача