Изобретение относится к вычислительной технике, в частности к уст- i ройствам задержки дискретных-сигналов, и может быть использовано при построении синхронизируюп(их блоков вьшислительных устройств.

Целью изобретения является рас- пшрение области применения устройства за счет получения нескольких значений задержки на одном временном интервале,

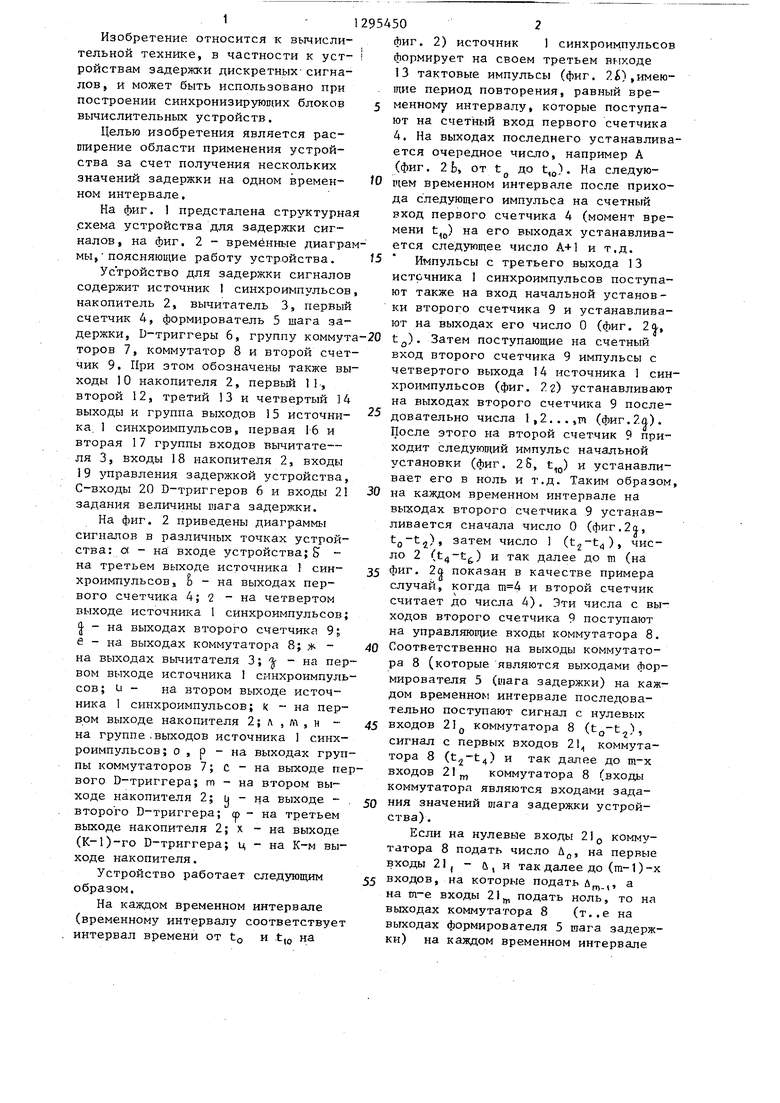

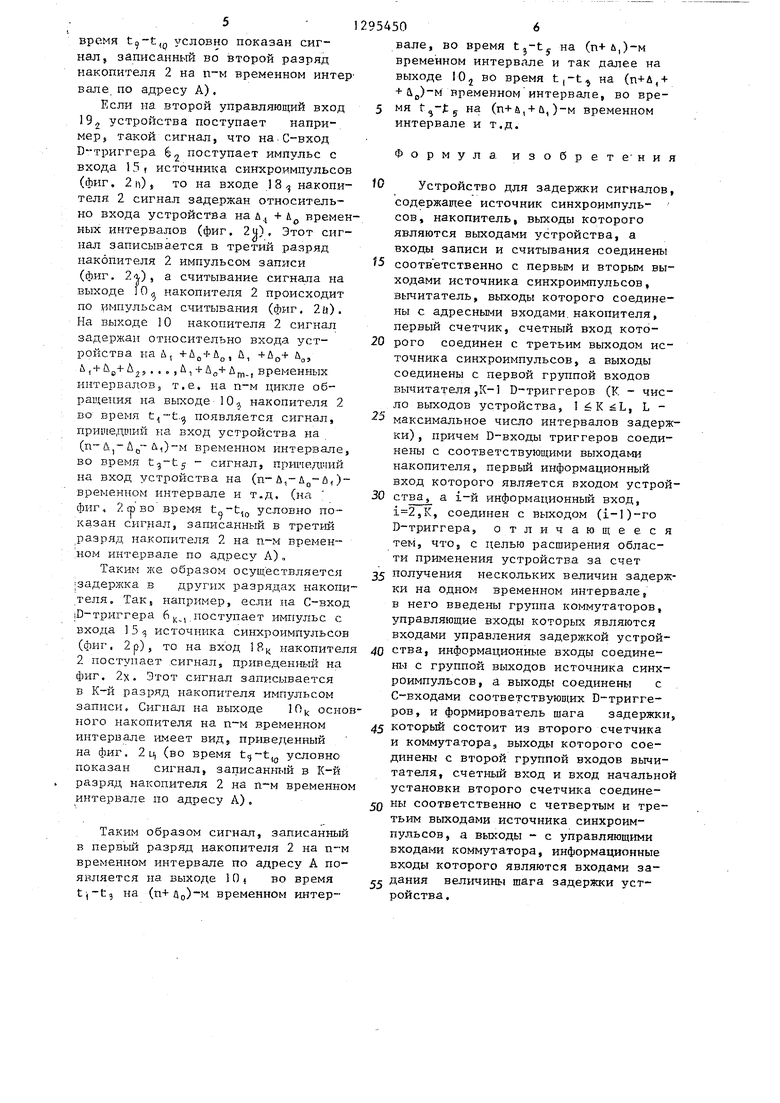

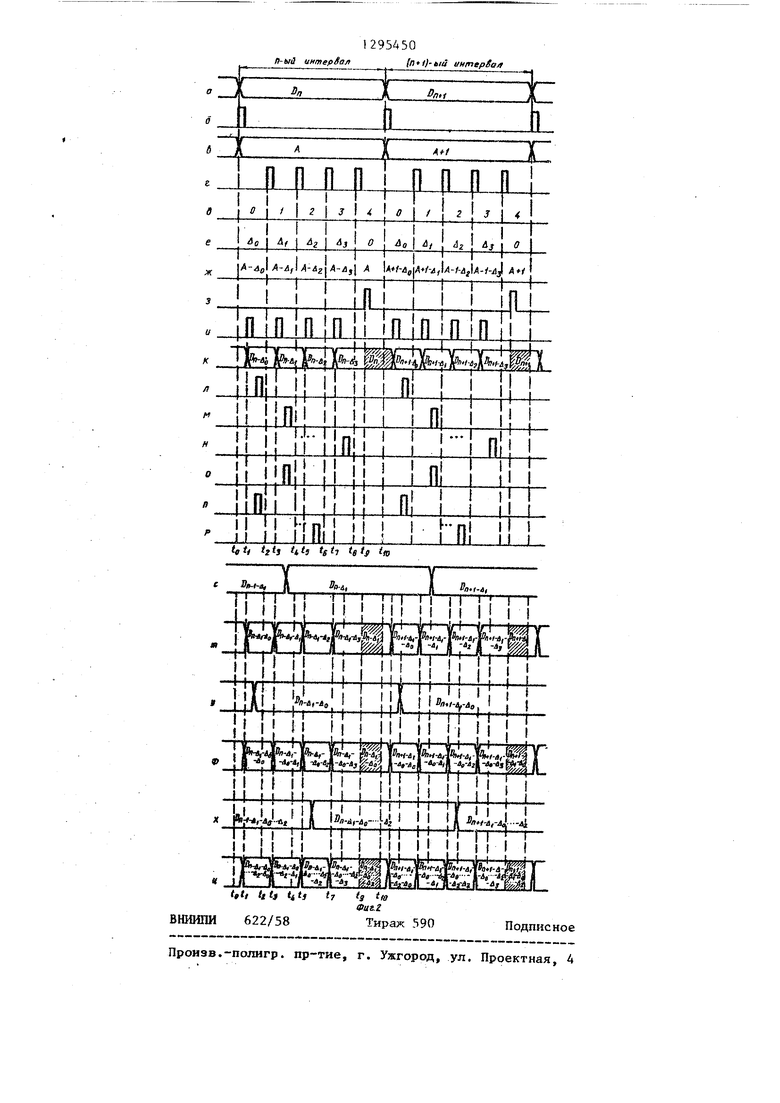

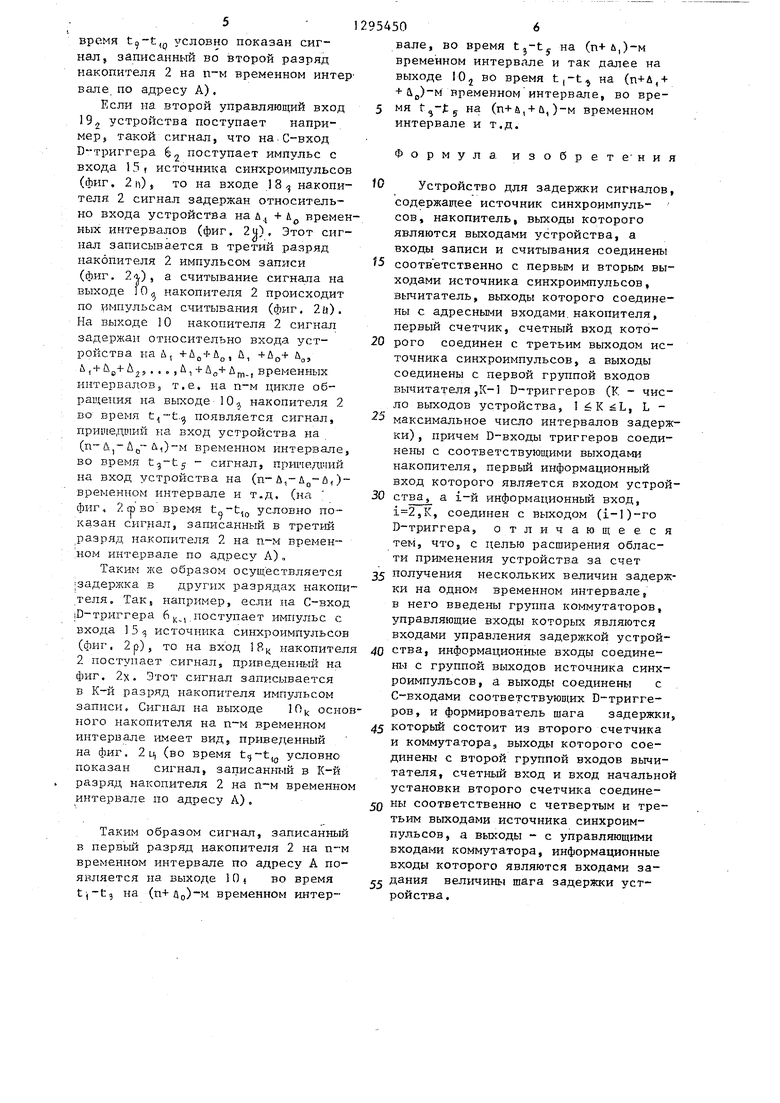

На фиг. 1 предсталена структурная схема устройства для задержки сигналов , на фиг. 2 - временные диаграм

мы, поясняющие работу устройства.

Устройство для задержки сигналов содержит источник I синхроимпульсов, накопитель 2, вычитатель 3, первый счетчик 4, формирователь 5 шага задержки, D-триггеры 6, группу коммута торов 7, коммутатор 8 и второй счетчик 9. При этом обозначены также выходы 0 накопителя 2, первый 1 Ь, второй 12, третий 13 и четвертый 14 выходы и группа выходов 15 источника. 1 синхроимпульсов, первая 16 и вторая 17 группы входов вычитате- ля 3, входы 18 накопителя 2, входы 19 зшравления задержкой устройства, С-входы 20 D-триггеров 6 и входы 21 задания величины шага задержки.

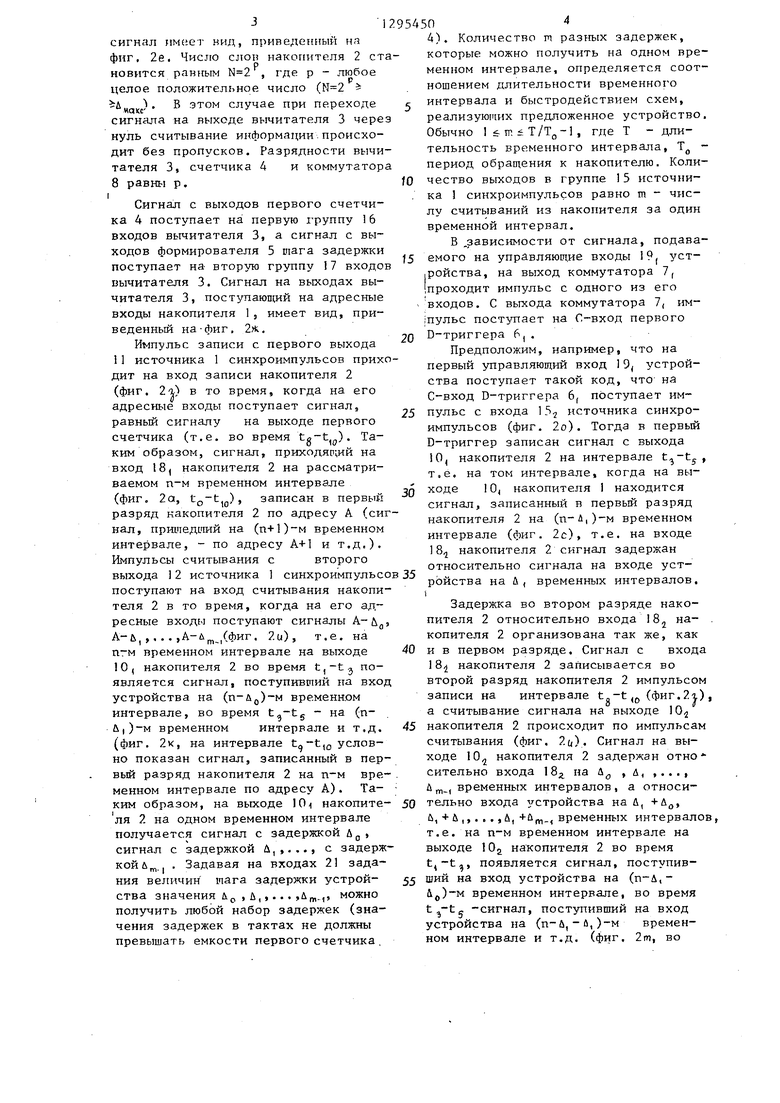

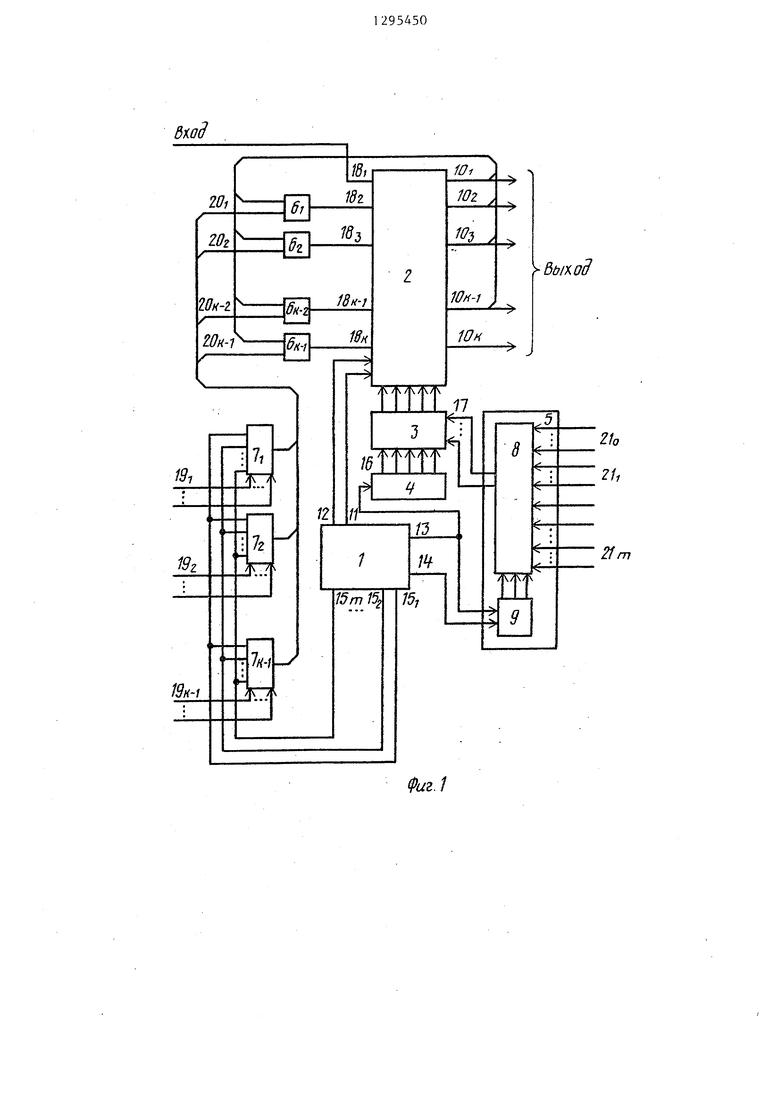

На фиг. 2 приведены диаграммы сигналов в различных точках устройства: 01 - на входе устройства; S на третьем выходе источника 1 синхроимпульсов , & - на выходах первого счетчика 4; 2 - на четвертом выходе источника 1 синхроимпульсов; J - на выходах второго счетчика 9; S - на выходах коммутатора 8; ;к - на выходах вычитателя 3; J- - на первом выходе источника 1 синхроимпульсов; U - на втором выходе источника 1 синхроимпульсов; k - на пер

вом выходе накопителя 2; л , м, н - на группе.выходов источника 1 синхроимпульсов ; о , р - на выходах группы коммутаторов 7; с - на выходе певого D-триггера; m - на втором выходе накопителя 2; и - на выходе - второго D-триггера; ср - на третьем выходе накопителя 2; ч - на выходе (K-l)-ro D-триггера; ц - на К-м выходе накопителя.

Устройство работает следующим образом.

На каждом временном интервале (временному интервалу соответствует интервал времени от to и .t,o на

5

0

0

фиг. 2) источник 1 синхроимпульсов формирует на своем третьем выходе 13 тактовые импульсы (фиг. 2),имеющие период повторения, равный временному интервалу, которые поступают на счетный вход первого счетчика 4. На выходах последнего устанавливается очередное число, например А (фиг. 2 Ь, от t до t,). На следующем временном интервале после прихода следующего импульса на счетный вход первого счетчика 4 (момент времени ) на его выходах устанавливается следующее число А+1 и т.д.

Импульсы с третьего выхода 13 источника 1 синхроимпульсов поступают также на вход начальной установки второго счетчика 9 и устанавливают на выходах его число О (фиг. 2, t). Затем поступающие на счетный вход второго счетчика 9 импульсы с четвертого выхода 14 источника 1 синхроимпульсов (фиг. 2г) устанавливают на выходах второго счетчика 9 после- довательно числа l,2...,in (фиг.2й). После этого на второй счетчик 9 приходит следуюп(ий импульс начальной установки (фиг. 25, t,) и устанавливает его в ноль и т.д. Таким образом, на каждом временном интервале на выходах второго счетчика 9 устанавливается сначала число О (фиг.2а, -t), затем число 1 (), чис -0

ло

2 () и так далее до m (на

фиг. 2а показан в качестве примера случай, когда и второй счетчик считает до числа 4). Эти числа с выходов второго счетчика 9 поступают на управляющие входы коммутатора 8.

Соответственно на выходы коммутатора 8 (которые являются выходами формирователя 5 (шага задержки) на каждом временном интервале последовательно поступают сигнал с нулевых

входов 21д коммутатора 8 (), сигнал с первых входов 21 коммутатора 8 ) и так далее до т-х входов 21 коммутатора 8 (входы коммутатора являются входами задаНИЛ значений пгага задержки устройства).

Если на нулевые входы 21 коммутатора 8 подать число Д, на первые входы 21, - U , и так далее до (т-1) -х

входов, на которые подать ,, а на т-е входы 21 подать ноль, то на выходах коммутатора 8 (т..е на выходах формирователя 5 шага задержки) на каждом временном интервале

фиг, 2е. Число слов наконителя 2 стновится ранным , где р - любое целое положительное число ( - .) В этом случае при переходе

WCJKC

сигнала на выходе вычитателя 3 чере нуль считывание информации.происходит без пропусков. Разрядности вычитателя 3, счетчика 4 и коммутатор

8 равны р. I

Сигнал с выходов первого счетчика 4 поступает на первую группу 16 входов вычитателя 3, а сигнал с выходов формирователя 5 шага задержки поступает на- вторую группу 17 входо вычитателя 3. Сигнал на выходах вычитателя 3, поступающий на адресные входы накопителя 1, имеет вид, приведенный на-фиг. 2ж,

Импульс записи с первого выхода 11 источника 1 синхроимпульсов прихдит на вход записи накопителя 2 (фиг, 2г) в то время, когда на его адресные входы поступает сигнал, равный сигналу на выходе первого счетчика (т,е, во время tg-t,). Таким образом, сигнал, приходяг;ий на вход 18, накопителя 2 на рассматриваемом п-м временном интервале (фиг, 2а, ), записан в первый

разряд накопителя 2 по адресу А (синал, пришедший на (п+1)-м временном интервале, - по адресу А+1 и т,д.). Импульсы считывания с второго выхода 12 источника 1 синхроимпульс поступают на вход считывания накопителя 2 в то время, когда на его адресные ВХОДЕ поступают сигналы А-Ь| ,, , . ,А-((фиг, 2и), т,е. на п-м временном интервале на выходе 10, накопителя 2 во время tj-tj появляется сигнал, поступивший на вход устройства на (п-йд)-м временном интервале, во время - на (п- Л))-м временном интервале и т.д. (фиг, 2к, на интервале Ц-t,o условно показан сигнал, записанный в первый разряд накопителя 2 на п-м вре- манном интервале по адресу А). Та- КИМ образом, на выходе 10 накопите- ля 2 на одном временном интервале получается сигнал с задержкой д, сигнал с задержкой U,,,.., с задержкой и ., , Задавая на входах 21 зада- тага задержки устрой

т. I

ния величин ства значения Лр , U,,... ,л„.,, можно получить любой набор задержек (значения задержек в тактах не должны превышать емкости первого счетчика

35 40 45

0

которые можно получить на одном временном интервале, определяется соотношением длительности временног о с интервала и быстродействием схем, реализующих предложенное устройство. Обычно 1 .1. - T/TQ-I , где Т - длительность временного интервала, Т - период обращения к накопителю, КолиfO чество выходов в группе 15 источни- . ка 1 синхроимпульсов равно m - числу считываний из накопителя за один временной интервал.

В .зависимости от сигнала, подава15 емого на управляющие входы 19, устройства, на выход коммутатора 7, проходит импульс с одного из его - входов, С выхода коммутатора 7, им- , пульс поступает на С-вход первого

20 D-триггера 6, .

Предположим, например, что на первый управляющий вход 19 устройства поступает такой код, что на С-вход D-триггера 6, поступает им25 пульс с входа 5 источника синхроимпульсов (фиг. 2о). Тогда в первый D-триггер записан сигнал с выхода 10, накопителя 2 на интервале , т.е. на том интервале, когда на выjg ходе 10, накопителя 1 находится сигнал, записанный в первый разряд накопителя 2 на (п-Л|)-м временном интервале (фиг, 2с), т.е, на входе 18 накопителя 2 сигнал задержан относительно сигнала на входе устройства на U, временных интервалов, i

Задержка во втором разряде накопителя 2 относительно входа 18 на- . копителя 2 организована так же, как и в первом разряде. Сигнал с входа 18 накопителя 2 записывается во второй разряд накопителя 2 импульсом записи на интервале t.-t ,( (фиг.2г) , а считывание сигнала на выходе 10 накопителя 2 происходит по импульсам считывания (фиг, 2(,). Сигнал на выходе 10 накопителя 2 задержан отно сительно входа 18, на Д.

г о

U „., временных интервалов, а относительно входа з стройства на Л, +Лд, U, U I,, ,., U, +й., временных интервалов, т.е. на п-м временном интервале на выходе 1Oj накопителя 2 во время t,-t, появляется сигнал, поступив- 5 ший на вход устройства на (п-д,- йд)-м временном интервале, во время -сигнал, поступивший на вход устройства на (п-й,-й,)-м временном интервале и т.д. (фиг, 2т, во

время ,p условно показан сигнал, записанный во второй разряд накопителя 2 на временном интер вале, по адресу А).

Если на второй управляющий вход 19, устройства поступает напри-, мер, такой сигнал, что на-С-вход В-триггера 82 поступает импульс с входа 15f источника синхроимпульсов (фиг, 2 и), то на входе 18 накопителя 2 сигнал задержан относительно входа устройства на д,, + л временных интервалов (фиг, 2ц), Этот сигнал записывается в третий разряд накопителя 2 импульсом записи (фиг, 2г), а считывание сигнала на выходе 10 накопителя 2 происходит по импульсам считывания (фиг. 2и). На выходе 10 накопителя 2 сигнал задержан относительно входа устройства на U, +Ло+й„, U, +Д(,+ й„, u,+ ug+Д, . . „ , U, + До+Д, временных интервалов3 т,е, на п-м цикле об- раьцеиия на выходе 10, накопителя 2

во время . появляется сигнал, пришед111ий на вход устройства на (,-До й,)-м временном интервале, во время - сигнал, пршчедхчий на вход устройства на (п-U,-Дц-й,) временном интервале и т.д. (на фиг, 2 m во время to-t,g условно показан сигнал, записанный в третий разряд накопителя. 2 на п-м времен- ном интервале по адресу А)„

Таким же образом осуществляется ;задерл ка в других разрядах накопителя. Так, например, если на С-вход iD-триггера 6 ц, .поступает импульс с входа 5 источника синхроимпульсов (фиг. 2р)5 то на вход 18 накопителя 2 поступает сигнал, приведен {ый на фиг. 2х. Этот сигнал записывается в К-й разряд накопителя импульсом записи. Сигпал на выходе l(, основного накопителя на п-м временном интервале имеет вид, приведенный на фиг. 2ц (во время , условно показан сигнал, записанный в К-й разряд накопителя 2 на п-м временном интервале по адресу А),

Таким образом сигнал, записанный в первый разряд накопителя 2 на п-м временном интервале по адресу А появляется на выходе 10. во время t-,-t, на (п+ао)-м временном интер

12954506

вале, во время на (п+й,)-м временном интервале и так далее на выходе lOj во время t,-t на (п+Д,+ + йд)-м временном интервале, во вре- 5 мя на (n+u, + u,)-M временном интервале и т,д.

Формула изобрете ния

Устройство для задержки сигналов, содержащее источник синхроимпульсов, накопитель, выходы которого являются выходами устройства, а входы записи и считывания соединены

соответственно с первым и вторым выходами источника синхроимпульсов, вычитатель, выходы которого соединены с адресными входами.накопителя, первый счетчик, счетный вход которого соединен с третьим выходом источника синхроимпульсов, а выходы соединены с первой группой входов вычитателя,К-1 D-триггеров (К - число выходов устройства, 1 6 К L, L - максимальное число интервалов задержки) , причем D-входы триггеров соеди- нень с соответствующими выходами накопителя, первьй информационный вход которого является входом устрой- ства, а i-й информационный вход, ,К, соединен с выходом (i-l)-ro D-триггера,, отличающееся тем, что, с целью расширения области применения устройства за счет получения нескольких величин задержки на одном временном интервале, в него введены группа коммутаторов, управляющие входы которых являются входами управления задержкой устройства, информационные входы соединены с группой выходов источника синхроимпульсов, а выходы соединены с С-входами соответствующих D-триггеров, и формирователь шага задержки, которьй состоит из второго счетчика и коммутатора,, выходы которого соединены с второй группой входов вычитателя, счетный вход и вход начальной установки второго счетчика соедине- ны соответственно с четвертым и третьим выходами источника синхроимпульсов, а выходы - с управляющими входами коммутатора, информационные входы которого являются входами за- дания величины шага задержки устройства ,

ВшкоЗ

21т

t,ti tftj , tfti tgtf ia

Г

. . . A

Ti I I 11 I

Uffil

.WttdC, JL

I i

fl,-i.

йАГЙ1СгЕЖ

УФЩ л i п т I t Ii I I и I till

lit J t M ; t ( I 1 I

Ml

I I

f I

I 1

I I

I . i ГП П г

-AJ

M III i i I

bkirik- - щ KU,il8 LHM - «. г

- «-«- ««iWie i , a,--- b, ,.-.-j-i, I n t Шя ft щ-ж

ипч-л,

I jT i I I {

ffil

tdC, JL

i-tf-тч-л,

M

Jlji | ||.

I I

I I

-AJ

tft, tfti tft, If ВНИИПИ 622/58

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

(3 ife .г

Тирак 590

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для сжатия данных | 1987 |

|

SU1522268A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Устройство для статистической обработки результатов измерений по скользящей выборке | 1984 |

|

SU1223250A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Арифметическое устройство | 1984 |

|

SU1229754A1 |

Изобретение относится к вычислительной технике, в частности к устройствам задержки дискретных сигналов, и может быть использовано при построении синхронизирующих блоков вычислительных устройств. Целью изобретения является расширение области применения устройства за счет получения нескольких значений задержки на одном временном интервале. Поставленная цель достигается тем, что в известное устройство введены группа коммутаторов и формирователь тага задержки, состоящий из коммутатора и второго счетчика. Введенные блоки служат для установления как количества различных задержек на каждом временном интервале, так и значений этих задержек. 2 ил.

| УСТРОЙСТВО для ВЫБОРКИ АДРЕСА В ПОСТОЯННОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 0 |

|

SU357590A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Радиотелеграфный регенеративный приемник | 1923 |

|

SU824A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-01—Подача