(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения состязаний в синхронизируемых дискретных блоках | 1985 |

|

SU1298750A1 |

| Устройство для обнаружения сбоев синхронизируемой цифровой системы | 1984 |

|

SU1176332A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля состояния цифровых объектов | 1983 |

|

SU1180900A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО АНАЛИЗА СХЕМ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 1968 |

|

SU218521A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков. Отличительной особенностью устройства является то, что оно позволяет контролировать динамические состязания контролируемой последовательности. Целью изобретения является расширение функциональных возможностей за счет контроля информации во время импульса и паузы синхроимпульсов. Поставленная цель достигается за счет введения элементов НЕ 8, 9, элементов ИЛИ 10 - 13, счетчиков 16 - 18, сумматоров 19. 20, 21. 6 ил.

о

00

Оч

Ј

00

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков.

Целью изобретения является расширение функциональных возможностей за счет контроля информации во время импульса и паузы синхроимпульсов.

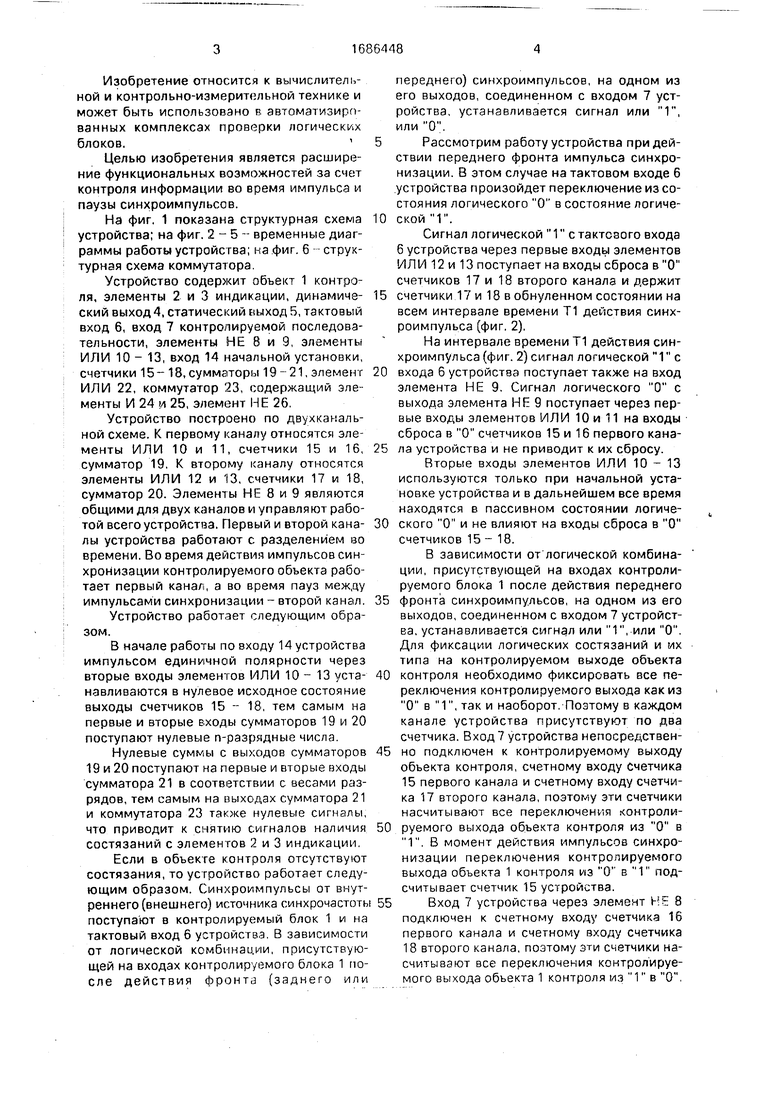

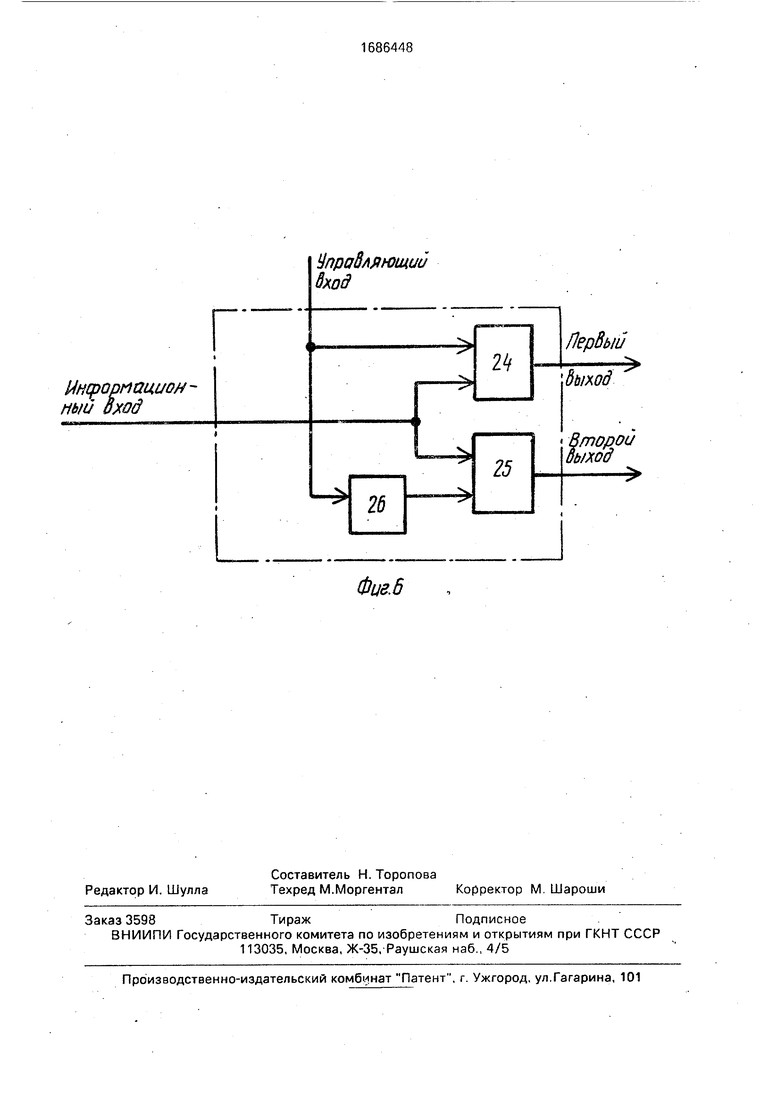

На фиг. 1 показана структурная схема устройства; на фиг. 2 - 5 - временные диаграммы работы устройства; на фиг. 6 - структурная схема коммутатора.

Устройство содержит объект 1 контроля, элементы 2 и 3 индикации, динамиче- ский выход 4, статический выход 5, тактовый вход 6, вход 7 контролируемой последовательности, элементы НЕ 8 и 9, элементы ИЛИ 10 - 13, вход 14 начальной установки, счетчики 15- 18,сумматоры 19 -21, элемент ИЛИ 22, коммутатор 23, содержащий элементы И 24 и 25, элемент НЕ 26.

Устройство построено по дв хканаль- ной схеме. К первому каналу относятся эле менты ИЛИ 10 и 11, счетчики 15 и 16, сумматор 19. К второму каналу относятся элементы ИЛИ 12 и 13, счетчики 17 и 18, сумматор 20. Элементы НЕ 8 и 9 являются общими для двух каналов и управляют работой всего устройства. Первый и второй кана- лы устройства работают с разделением во времени. Во время действия импульсов синхронизации контролируемого объекта работает первый канал, а во время пауз между импульсами синхронизации - второй канал.

Устройство работает следующим образом.

В начале работы по входу 14 устройства импульсом единичной полярности через вторые входы элементов ИЛИ 10 - 13 уста- навливаются в нулевое исходное состояние выходы счетчиков 15 - 18. тем самым на первые и вторые входы сумматоров 19 и 20 поступают нулевые n-разрядные числа.

Нулевые суммы с выходов сумматоров 19 и 20 поступают на первые и вторые входы сумматора 21 в соответствии с весами разрядов, тем самым на выходах сумматора 21 и коммутатора 23 также нулевые сигналы. что приводит к снятию сигналов наличия состязаний с элементов 2 и 3 индикации.

Если в объекте контроля отсутствуют состязания, то устройство работает следующим образом. Синхроимпульсы от внутреннего (внешнего) источника синхрочастоты поступают в контролируемый блок 1 и на тактовый вход 6 устройства. В зависимости от логической комбинации, присутствующей на входах контролируемого блока 1 после действия фронта (заднего или

переднего) синхроимпульсов, на одном из его выходов, соединенном с входом 7 устройства, устанавливается сигнал или 1, или О.

Рассмотрим работу устройства при действии переднего фронта импульса синхронизации. В этом случае на тактовом входе 6 устройства произойдет переключение из состояния логического О в состояние логической 1.

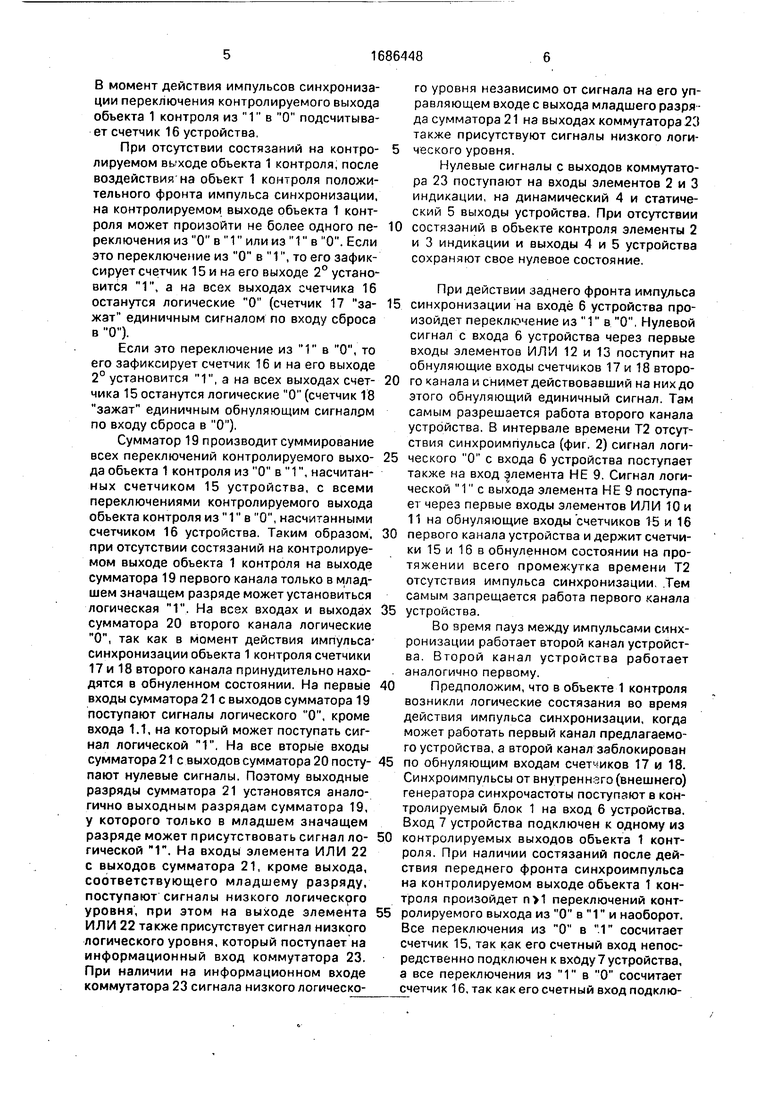

Сигнал логической 1 с тактового входа 6 устройства через первые входы элементов ИЛИ 12 и 13 поступает на входы сброса в О счетчиков 17 и 18 второго канала и держит счетчики 17 и 18 в обнуленном состоянии на всем интервале времени Т1 действия синхроимпульса (фиг. 2).

На интервале времени Т1 действия синхроимпульса (фиг. 2) сигнал логической 1 с входа 6 устройства поступает также на вход элемента НЕ 9. Сигнал логического О с выхода элемента НЕ 9 поступает через первые входы элементов ИЛИ 10 и 11 на входы сброса в О счетчиков 15 и 16 первого канала устройства и не приводит к их сбросу.

Вторые входы элементов ИЛИ 10 - 13 используются только при начальной установке устройства и в дальнейшем все время находятся в пассивном состоянии логического О и не влияют на входы сброса в О счетчиков 15 - 18.

В зависимости от логической комбинации, присутствующей на входах контролируемого блока 1 после действия переднего фронта синхроимпульсов, на одном из его выходов, соединенном с входом 7 устройства, устанавливается сигнал или 1, или О. Для фиксации логических состязаний и их типа на контролируемом выходе объекта контроля необходимо фиксировать все переключения контролируемого выхода как из О в 1, так и наоборот. Поэтому в каждом канале устройства присутствуют по два счетчика. Вход 7 устройства непосредственно подключен к контролируемому выходу объекта контроля, счетному входу счетчика 15 первого канала и счетному входу счетчика 17 второго канала, поэтому эти счетчики насчитывают все переключения контролируемого выхода объекта контроля из О в 1 В момент действия импульсов синхронизации переключения контролируемого выхода объекта 1 контроля из О в 1 подсчитывает счетчик 15 устройства.

Вход 7 устройства через элемент 4е. 8 подключен к счетному входу счетчика 16 первого канала и счетному входу счетчика 18 второго канала, поэтому эти счетчики насчитывают все переключения контролируемого выхода объекта 1 контроля из 1 в О

В момент действия импульсов синхронизации переключения контролируемого выхода объекта 1 контроля из 1 в О подсчитывает счетчик 16 устройства.

При отсутствии состязаний на конгро- лируемом выходе объекта 1 контроля, после воздействий на объект 1 контроля положительного фронта импульса синхронизации, на контролируемом выходе объекта 1 контроля может произойти не более одного пе реключения из О в 1 или из 1 в О, Если это переключение из О в 1, то его зафиксирует счетчик 15 и на его выходе 2° установится 1, а на всех выходах счетчика 16 останутся логические О (счетчик 17 за- жат единичным сигналом по вход/ сброса в О).

Если это переключение из 1 в О, то его зафиксирует счетчик 16 и на его выходе 2° установится 1, а на всех выходах счет- чика 15 останутся логические О (счетчик 18 зажат единичным обнуляющим сигналом по входу сброса в О).

Сумматор 19 производит суммирование всех переключений контролируемого выхо- да объекта 1 контроля из О в 1, насчитанных счетчиком 15 устройства, с всеми переключениями контролируемого выхода объекта контроля из 1 в О, насчи энными счетчиком 16 устройства. Таким образом, при отсутствии состязаний на контролируемом выходе объекта 1 контроля на выходе сумматора 19 первого канала только в младшем значащем разряде может установиться логическая 1. На всех входах и выходах сумматора 20 второго канала логические О, так как в момент действия импульса- синхронизации объекта 1 контроля счетчики 17 и 18 второго канала принудительно находятся в обнуленном состоянии. На первые входы сумматора 21с выходов сумматора 19 поступают сигналы логического О, кроме входа 1.1, на который может поступать сигнал логической 1. На все вторые входы сумматора 21 с выходов сумматора 20 посту- лают нулевые сигналы. Поэтому выходные разряды сумматора 21 установятся аналогично выходным разрядам сумматора 19, у которого только в младшем значащем разряде может присутствовать сигнал ло- гической 1. На входы элемента ИЛИ 22 с выходов сумматора 21, кроме выхода, соответствующего младшему разряду, поступают сигналы низкого логического уровня, при этом на выходе элемента ИЛИ 22 также присутствует сигнал низкого логического уровня, который поступает на информационный вход коммутатора 23 При наличии на информационном входе коммутатора 23 сигнала низкого логического уровня независимо от сигнала на его управляющем входе с выхода младшего разря да сумматора 21 на выходах коммутатора 23 также присутствуют сигналы низкого логического уровня.

Нулевые сигналы с выходов коммутатора 23 поступают на входы элементов 2 и 3 индикации, на динамический 4 и статический 5 выходы устройства. При отсутствии состязаний в объекте контроля элементы 2 и 3 индикации и выходы 4 и 5 устройства сохраняют свое нулевое состояние.

При действии заднего фронта импульса синхронизации на входе 6 устройства произойдет переключение из 1 в О. Нулевой сигнал с входа 6 устройства через первые входы элементов ИЛИ 12 и 13 поступит на обнуляющие входы счетчиков 17 и 18 второго канала и снимет действовавший на них до этого обнуляющий единичный сигнал. Там самым разрешается работа второго канала устройства. В интервале времени Т2 отсутствия синхроимпульса (фиг. 2) сигнал логического О с входа 6 устройства поступает также на вход элемента НЕ 9. Сигнал логической 1 с выхода элемента НЕ 9 поступа- ei через первые входы элементов ИЛИ 10 и 11 на обнуляющие входы счетчиков 15 и 16 первого канала устройства и держит счетчики 15 и 16 в обнуленном состоянии на протяжении всего промежутка времени Т2 отсутствия импульса синхронизации Тем самым запрещается работа первого канала устройства.

Во время пауз между импульсами синхронизации работает второй канал устройства. Второй канал устройства работает аналогично первому.

Предположим, что в объекте 1 контроля возникли логические состязания во время действия импульса синхронизации, когда может работать первый канал предлагаемого устройства, а второй канал заблокирован по обнуляющим входам счет-иков 17 и 18. Синхроимпульсы от внутреннего (внешнего) генератора синхрочастоты поступают в контролируемый блок 1 на вход 6 устройства. Вход 7 устройства подключен к одному из контролируемых выходов объекта 1 контроля. При наличии состязаний после действия переднего фронта синхроимпульса на контролируемом выходе объекта 1 контроля произойдет переключений контролируемого выхода из О в 1 и наоборот. Все переключения из О в Г сосчитает счетчик 15, так как его счетный вход непосредственно подключен к входу 7 устройства, а все переключения из 1 в О сосчитает счетчик 16. так как его счетный вход подключен к входу 7 устройства через инвертирующий элемент НЕ 8 устройства.

Сумматор 19 произведет суммирование всех переключений контролируемого выхода объекта 1 контроля из О в 1 и из 1 в О, посчитанных соответственно счетчиками 15 и 16. На выходах сумматора 19 установится двоичное число, равное количеству переключений из О в 1 и из 1 в О контролируемого выхода объекта 1 контроля. Если произошли статические состязания, то на выходе сумматора 19 установится четное двоичное число, причем в младшем значащем разряде О. Если произошли динамические состязания, то количество переключений контролируемого объекта контроля нечетное, на выходе сумматора 19 установится нечетное двоичное число, причем в младшем значащем разряде 1.

Двоичное число, равное количеству переключений контролируемого выхода объекта контроля, с выходов сумматора 19 поступает на первые входы сумм&тора 21 и суммируется на сумматоре 21 с нулевым двоичным числом, поступающим на вторые входы сумматора 21 с выходов сумматора 20 второго канала (выходы сумматора 20 находятся в нулевом состоянии, так как в момент действия синхроимпульса счетчики 17 и 18 второго канала постоянно обнулены). В результате на выходе сумматора 21 устанавливается такое же двоичное п-разрядное число, какое установилось на выходе сумматора 19 первого канала. Двоичное число, установившееся на выходах сумматора 21. равно количеству переключений контролируемого выхода объекта контроля из О в 1 и наоборот.

При статических состязаниях нулевой сигнал, установившийся в младшем значащем разряде на первом выходе сумматора 21, поступает на управляющий вход коммутатора 23. Так как при состязаниях количество переключений контролируемого выхода объекта контроля . то на выходах сумматора 19, кроме первого выхода, соответствующего младшему разряду, а следовательно, -и на аналогичных выходах сумматора 21 установится такое двоичное число, в котором присутствует 1 хотя бы в одном из разрядов 2,3,4п. Следовательно, хотя бы на одном из входов элемента ИЛИ 22 присутствует 1, которая переводит выход элемента ИЛИ 22 в 1. На информационный вход коммутатора 23 поступает 1 с выхода элемента ИЛИ 22. Так как на управляющем входе коммутатора 23 при статических состязаниях устанавливается О, а на информационном входе 1, то это приводит к включению элемента 3 индикации и появлению 1 на выходе 5 устройства. Сигнал на выходе 5 устройства используется для остановки источника синхронизации объекта 1 контроля и создания условий для поиска причин, вызвавших статические состязания,

При динамических состязаниях устройство работает аналогично с тем лишь отличием, что на управляющем входе коммутатора 23 устанавливается 1 с выхода младшего разряда сумматора 21. Это приводит к включению элемента 2 индикации и появлению 1 на выходе 4 устройства. Сигнал на выходе 4 устройства используется

для остановки источника синхронизации объекта 1 контроля и создания условий для поиска причин, вызвавших динамические состязания в объекте контроля.

При возникновении в объекте 1 контроля состязаний в период времени Т2 (фиг. 2) пауз между синхроимпульсами работа первого канала блокируется, а работа второго канала разрешается. При этом второй канал работает аналогично первому.

На фиг. 2 на интервале времени Ti действия синхроимпульса работает первый канал устройства, а в промежутках между синхроимпульсами работает второй канал устройства. Интервалы анализа TAI, Тд2

предлагаемого устройства равны соответственно интервалам Т1 и Т2 и сдвинуты один относительно другого только на время срабатывания первых счетных разрядов счетчиков первого и второго канала устройства.

- На фиг. 3 приведены временные диаграммы сигналов в следующих точках: на входе 6 устройства, входе 7 устройства, выходе 4, выходе 5. При этом алгоритм работы контролируемого выхода объекта

контроля заключается в переключении контролируемого выхода (на входе 7 устройства) в момент времени ti из О в 1 после действия n-го фронта синхронизации. В данном примере отсутствуют состязания

и выходы 4 и 5 предлагаемого устройства вместе с элементами 2 и 3 индикации нахо дятся в пассивном состоянии.

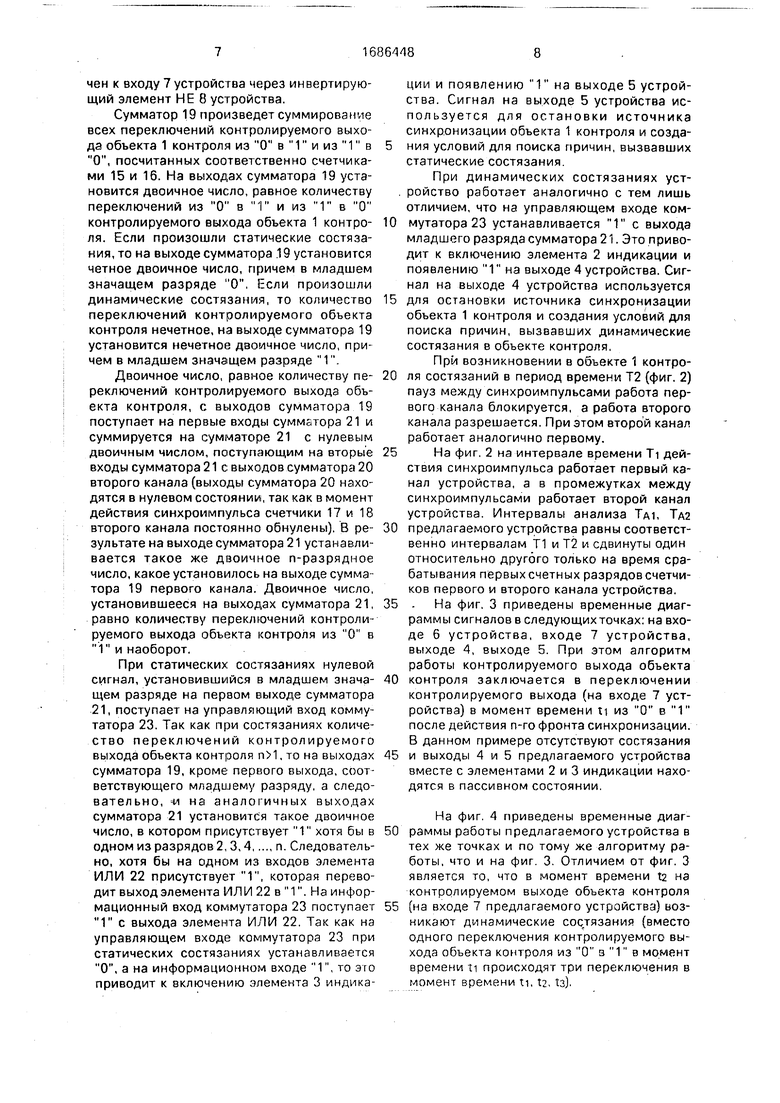

На фиг. 4 приведены временные диаг- 0 раммы работы предлагаемого устройства в тех же точках и по тому же алгоритму работы, что и на фиг 3, Отличием от фиг. 3 является то, что в момент времени t2 на контролируемом выходе объекта контроля 5 (на входе 7 предлагаемого устройство) возникают динамические состязания (вместо одного переключения контролируемого выхода объекта контроля из О э 1 в момент времени ti происходят три переключения в момент времени ti, 12. 1з)

В момент времени t2 происходит переключение (второе) выхода 5 предлагаемого устройства из О в 1, по которому осуществляется (при необходимости) блокировки синхрогенератора объекта контроля, в результате чего на объект контроля и на вход 6 предлагаемого устройства п+1-го фронта синхронизации не поступит. В момент времени гз состязания заканчиваются последним переключением контролируемого выхода объекта контроля (входа 7 предлагаемого устройства) из О в 1 и становится ясным, что произошли динамические состя- , так как количество переключений контролируемого выхода нечетное, при этом выход 4 устройства находится в активном состоянии и включен элемент 2 индикации.

После момента времени тз выход 5 и элемент 3 индикации в пассивном состоянии. В данном примере осуществляется блокировка синхронизации объекта контроля, так как работа контролируемого выхода объекта контроля не соответствует алгоритму работы (фиг. 3),

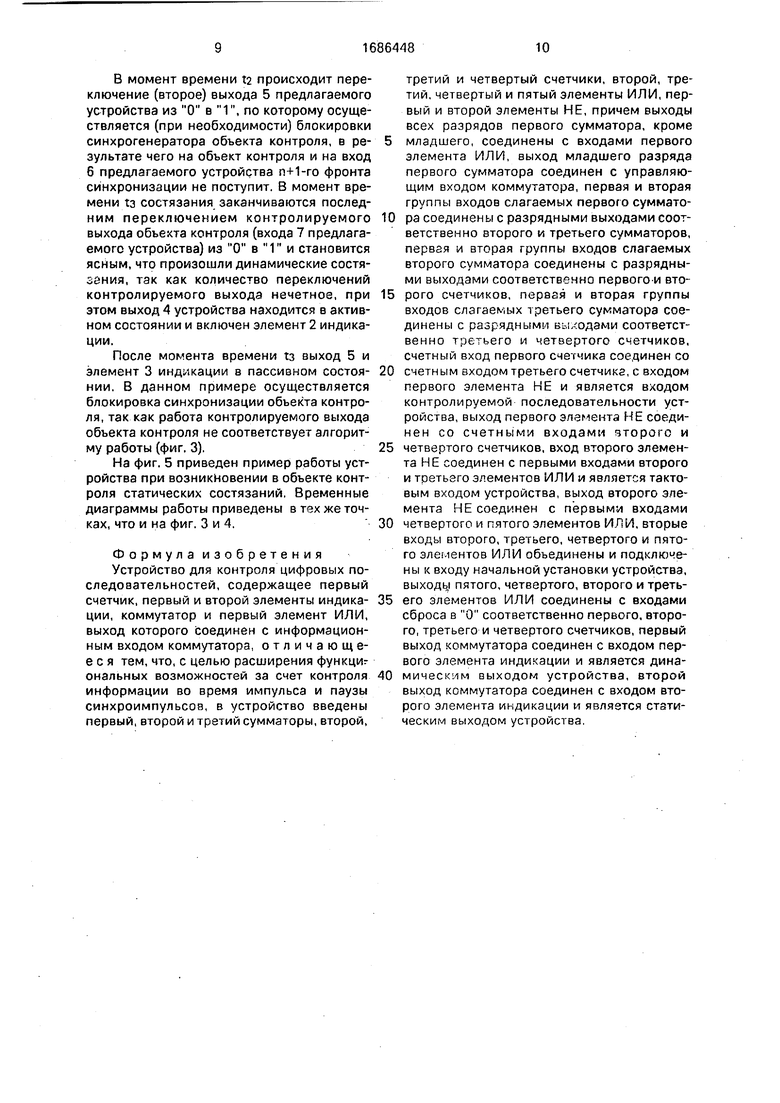

На фиг. 5 приведен пример работы устройства при возникновении в объекте контроля статических состязаний. Временные диаграммы работы приведены в т°х же точках, что и на фиг. 3 и 4.

Формула изобретения Устройство для контроля цифровых последовательностей, содержащее первый счетчик, первый и второй элементы индикации, коммутатор и первый элемент ИЛИ, выход которого соединен с информационным входом коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля информации во время импульса и паузы синхроимпульсов в устройство введены первый, второй и третий сумматоры, второй,

третий и четвертый счетчики, второй, третий, четвертый и пятый элементы ИЛИ, первый и второй элементы НЕ, причем выходы всех разрядов первого сумматора, кроме 5 младшего, соединены с входами первого элемента ИЛИ, выход младшего разряда первого сумматора соединен с управляющим входом коммутатора, первая и вторая группы входов слагаемых первого суммато0 ра соединены с разрядными выходами соответственно второго и третьего сумматоров, первая и вторая группы входов слагаемых второго сумматора соединены с разрядными выходами соответственно первого и вто5 рого счетчиков, первая и вторая группы входов слагаемых третьего сумматора соединены с разрядными в.; одами соответственно третьего и чятрертогс сметчиков, счетный вход первого счетика соединен со

0 счетным входом третьего счетчика, с входом первого элемента НЕ и является входом контролируемой последовательности устройства, выход первого эгкзмента НЕ соединен со счетными входами второго и

5 четвертого счетчиков, вход второго элемента НЕ соединен с первыми входами второго и третьего элементов ИЛИ и является тактовым входом устройства, выход второго эпе- мента НЕ соединен с первыми входами

0 четвертого и пятого элементов И ПИ, вторые входы второго, третьего, четвертого и пятого элементов ИЛИ объединены и подклю е- ны к входу начальной установки устройства, выходы пятого, четвертого, второго и треть5 его элементов ИЛИ соединены с входами сброса в О соответственно перьсго, второго, третьего и четвертого счетчиков, первый выход коммутатора соединен с входом первого элемента индикации и является дина0 мическим выходом устройства, второй выход коммутатора соединен с входом второго элемента иьдикэции и является статическим выходом устройства

Фиг. 6

| Устройство для обнаружения сбоев синхронизируемых дискретных блоков | 1983 |

|

SU1125628A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для обнаружения состязаний в синхронизируемых дискретных блоках | 1985 |

|

SU1298750A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-10-23—Публикация

1989-07-11—Подача