113

Изобретение относится к измерительной технике и может быть использовано в системах обработки информации.

Целью изобретения является расширение динамического диапазона измеряв мых частот.

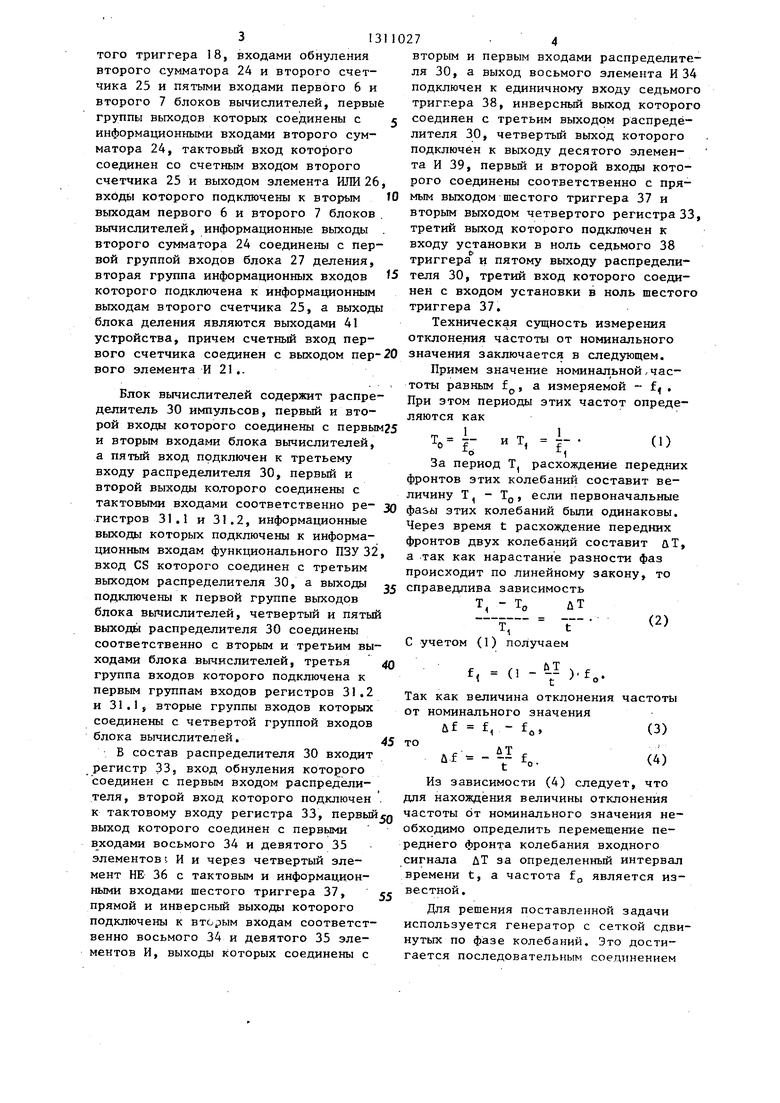

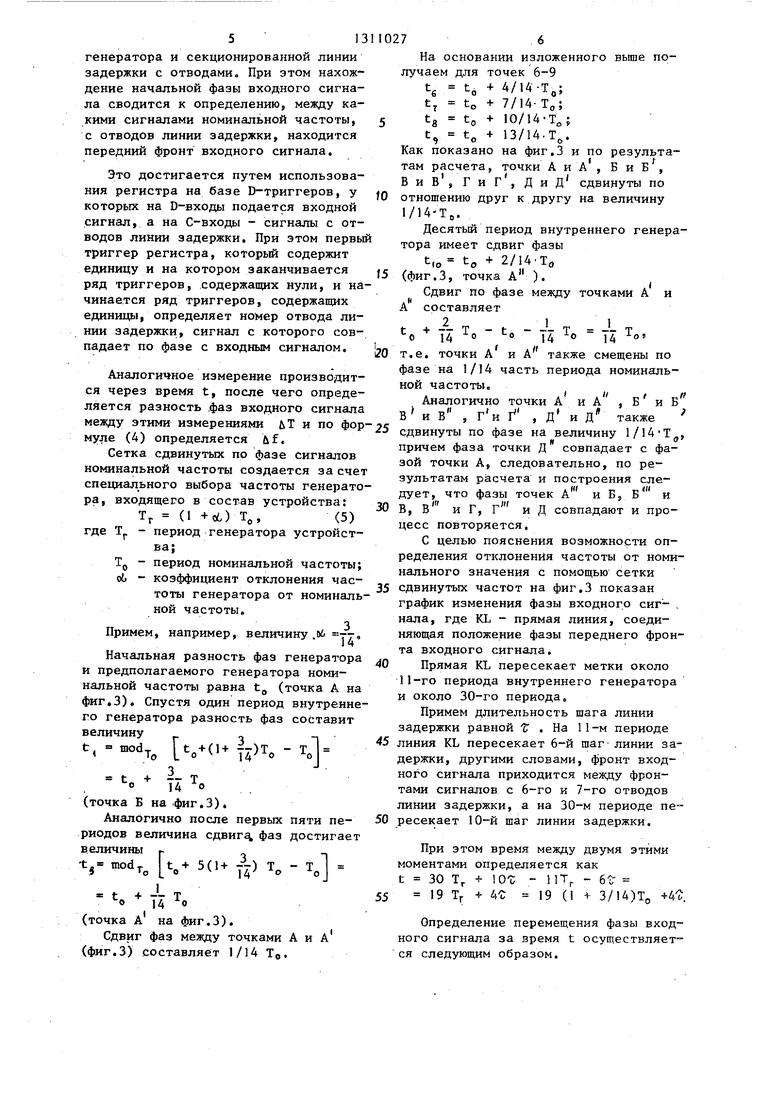

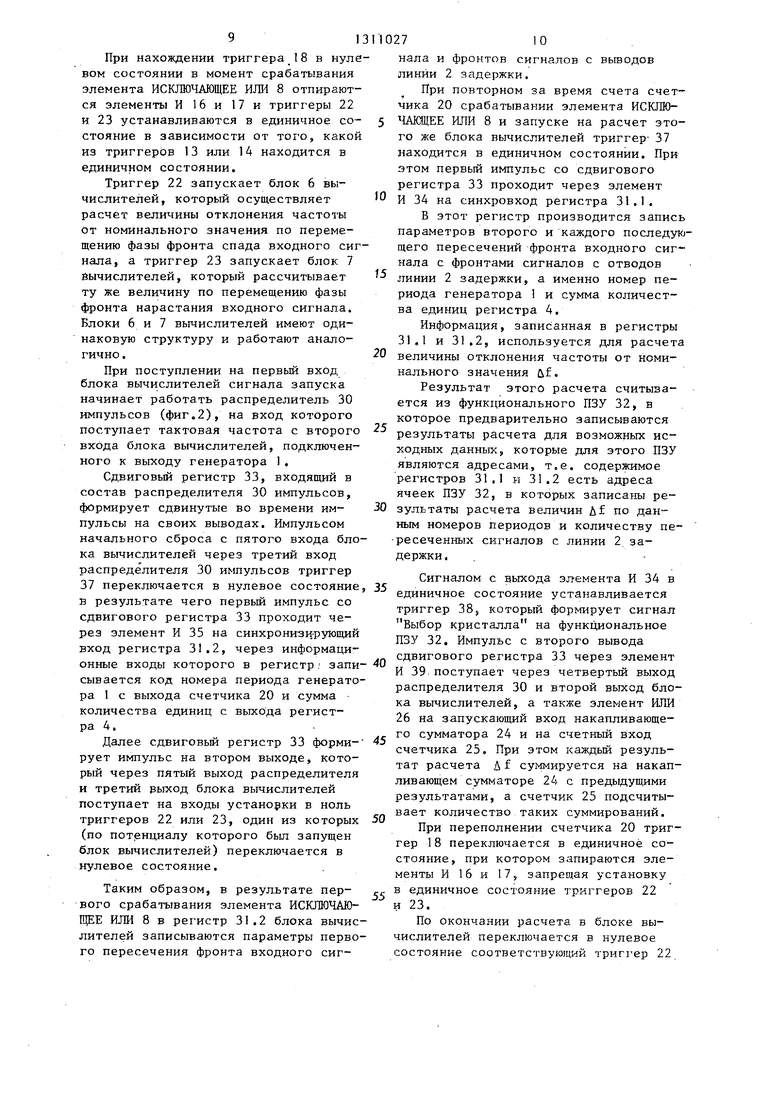

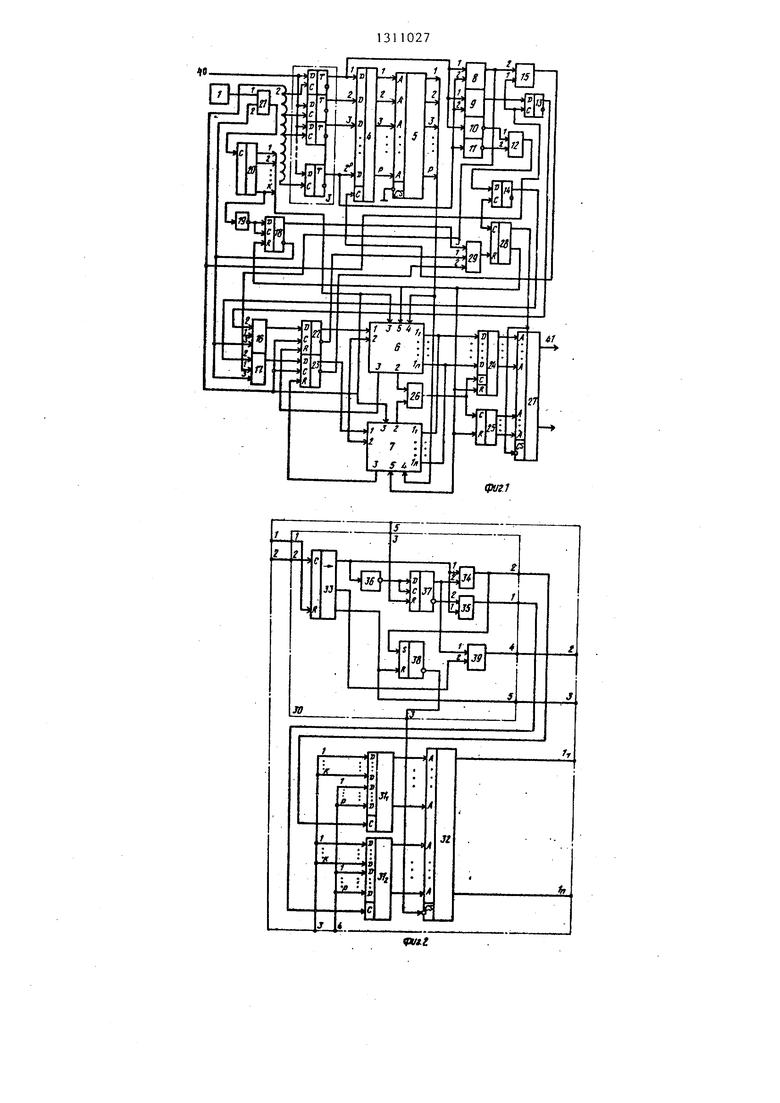

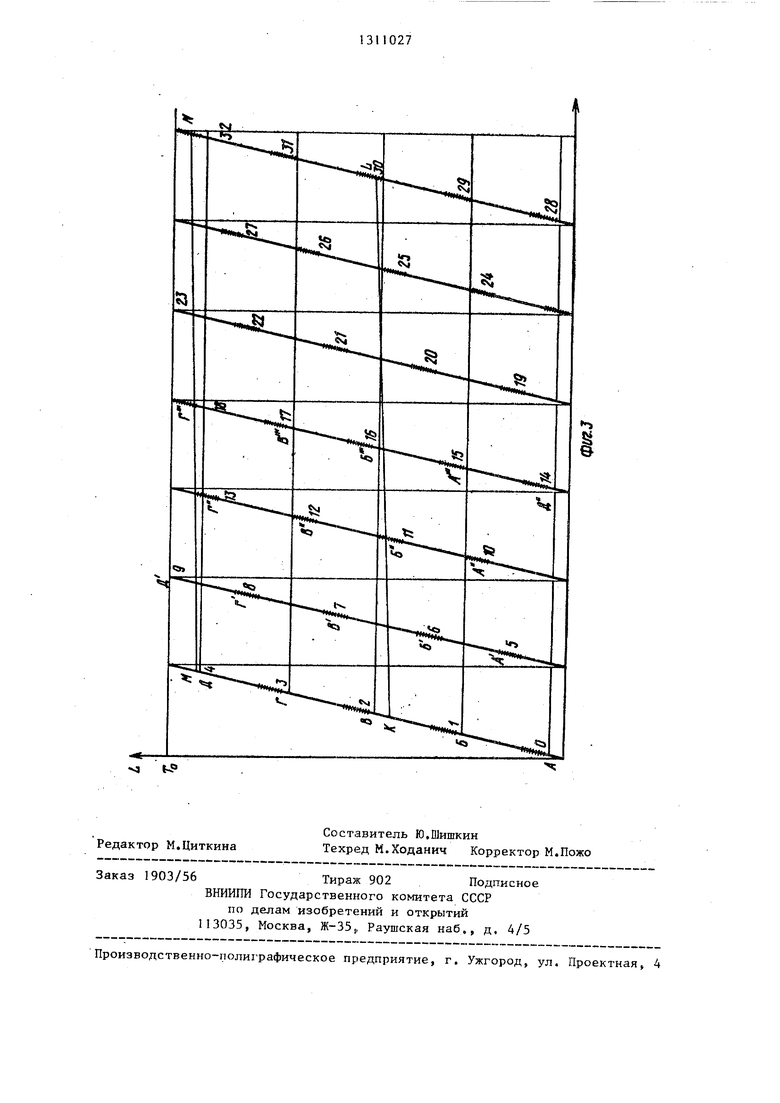

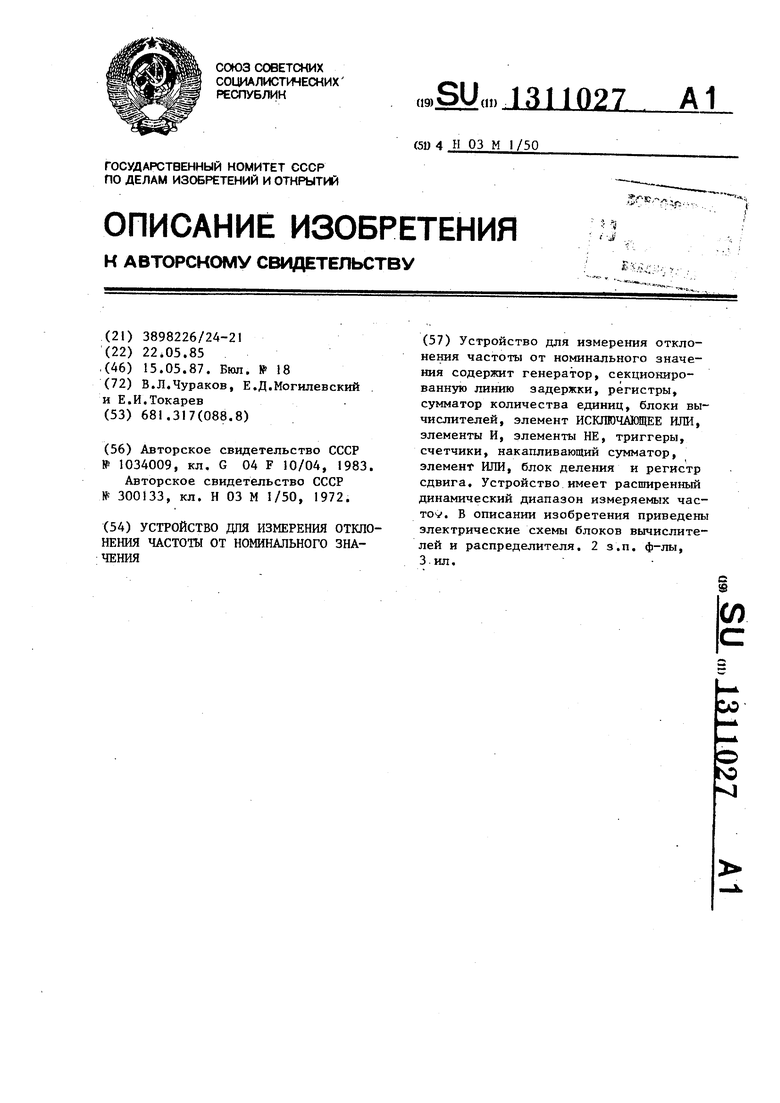

На фиг,1 представлена функциональная схема устройства измерения отклонения частоты от номинального зиа чения; на фиг.2 - функциональная схема блока вычислителей; на фиг.3 - диаграмма перемещения фаз генератора и входного сигнала в зависимости от времени.

Устройство содержит генератор 1 ,, секционированную линию 2 задержки, регистры 3 и 4, сумматор 5 количества единиц, блоки 6 и 7 вычислителей, элемент ИСКПЮЧАЩЕЕ ИЛИ 8, элемент И 9, элементы НЕ 10 и 11, элемент И 12, триггеры 13 и 14, элементы И 15- 17, триггер 18, элемент НЕ 19, счетчик 20, элемент И 21, триггеры 22 и 23, накапливающий сумматор 24, счетчик 25, элемент ИЛИ 26, блок 27 деления, регистр 28 сдвига, элемент И 29,

. Блоки 6 и 7 вычислителей (фиг.2) содержат распределитель 30 импульсов регистры 31.1 и 31.2, .функциональное ПЗУ 32. В состав распределителя 30

-, выход которого подключен к D-входу второго триггера 14, прямой выход которого соединен с вторым входом пятого элемента И 17, третьи входы четвертого 16 и пятого 17 элементов И подключены к второму входу первого элемента И 21 и инверсному выходу пятого триггера 18, D- и С--входы которого соединены с выходом третьего элемента НЕ 19, вход которого подклювходят сдвиговый регистр 33, элемент НЕ 36, триггер 37, элементы.И 34 и35,„ выходу старшего разряда перво- триггер 38 .и элемент-И 39, входная о счетчика 20, информационные выходы 40 и выходная 41 шины устройства. Выход генератора 1 соединен с первыми входами первого 21 и второго 15 элементов И, тактовыми входами первого Q 13, второго 14, третьего 22 и четвер- торого 23 триггеров, с вторыми входами первого 6 и второго 7 блоков вычислителей, с тактовым входом регистра 28 сдвига и входом секционирован-

50

ной линии 2 задержки, выводы секций которой подключены к.тактовым входам триггеров 3 регистра, информационные D-ВХОДЫ которых соединены между собой и подключены к входной шине 40 устройства, а прямые выходы соединены с информационными входами 4 ре- гистра, информационные выходы которого подключены к информационным входам первого сумматора 5, вход CS Выбор кристалла которого соединен с шиной уровня О, а информационные выходы подключены к группе четвертых входов первого 6 и второго 7 блоков вычискоторого соединены с третьей группой- входов первого 6 и второго 7 блоков вычислителей, Третьи выходы первого 6 и второго ,7 блоков вычислителей подключены к. входам установки в О соответственно третьего 22 и четвертого 23 триггеровS D-входы которых соединены с выходами соответственно четвертого 16 и пятого 17 элементов И, прямые выкоды третьего 22 и четвертого 23,триггеров подключены к первым входам соответственно первого 6 и второго 7 блоков вычислителей, а инверсные выходы третьего 22 и четвертого 23 триггеров соединены соответственно с первым и вторым входами элемента И 29, третий вход которого подключен к прямому вьгкоду пятого триггера 18, а выход элемента И 29 соединен с входом обнулеш-;я perHCTpia 28, первьй выход которого подключен к входу CS блока 27 деления, а второй соединен с входом установки в О пя

Ю

f5

10272

лителёй, причем прямой вьтод первого соединенного с первым выводом линии задержки триггера регистра 3 соединен с первыми входами элемента ИСКЛЮЧАЮ5 ЩЕЕ ИЛИ 8, третьего элемента И 9 и входом первого элемента НЕ 10, а прямой выход последнего триггера регистра 3 подключен к вторым входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, третьего элемента И 9 и входу второго элемента НЕ 11, выход элемента ИСКЛЮЧШЦЕЕ ИЛИ 8 соединен с вторьм входом второго элемента И 15 и первыми входами четвертого 16 и пятого 17 элементов И, а выход второго элемента И 15 подключен к тактовому входу регистра 4, выход третьего .элемента И 9 соединен с D-входом первого триггера 13, прямой выход которого подключен к второму входу четвертого элемента И 16, выходы первого 10 и второго 11 ментов НЕ соединены соответственно с первым и вторым входами элемента И 12,

-, выход которого подключен к D-входу второго триггера 14, прямой выход которого соединен с вторым входом пятого элемента И 17, третьи входы четвертого 16 и пятого 17 элементов И подключены к второму входу первого элемента И 21 и инверсному выходу пятого триггера 18, D- и С--входы которого соединены с выходом третьего элемента НЕ 19, вход которого подклю20

30

„ выходу старшего разряда перво- о счетчика 20, информационные выходы Q

выходу старшего разряда перво- о счетчика 20, информационные выходы

которого соединены с третьей группой- входов первого 6 и второго 7 блоков вычислителей, Третьи выходы первого 6 и второго ,7 блоков вычислителей подключены к. входам установки в О соответственно третьего 22 и четвертого 23 триггеровS D-входы которых соединены с выходами соответственно четвертого 16 и пятого 17 элементов И, прямые выкоды третьего 22 и четвертого 23,триггеров подключены к первым входам соответственно первого 6 и второго 7 блоков вычислителей, а инверсные выходы третьего 22 и четвертого 23 триггеров соединены соответственно с первым и вторым входами элемента И 29, третий вход которого подключен к прямому вьгкоду пятого триггера 18, а выход элемента И 29 соединен с входом обнулеш-;я perHCTpia 28, первьй выход которого подключен к входу CS блока 27 деления, а второй соединен с входом установки в О пятого триггера 18, входами обнуления второго сумматора 24 и второго счетчика 25 и пятыми входами первого 6 и второго 7 блоков вычислителей, первые группы выходов которых соединены с 5 информационными входами второго сумматора 24, тактовый вход которого соединен со счетным входом второго счетчика 25 и выходом элемента ИЛИ 26, входы которого подключены к вторым to выходам первого 6 и второго 7 блоков . вычислителей, информационные выходы . второго сумматора 24 соединены с первой группой входов блока 27 деления, вторая группа информационных входов 5 которого подключена к информационным выходам второго счетчика 25, а выходы блока деления являются выходами 41 устройства, причем счетный вход первторым и первым входами распредел ля 30, а выход восьмого элемента подключен к единичному входу седь триггера 38, инверсный выход кото соединен с третьим выходом распре лителя 30, четвертый выход которо подключён к выходу десятого элеме та И 39, первьш и второй входы ко рого соединены соответственно с п мым выходом шестого триггера 37 и вторым выходом четвертого регистр третий выход которого подключен к входу установки в ноль седьмого 3 триггера и пятому выходу распреде теля 30, третий вход которого сое нен с входом установки в ноль шес триггера 37,

Техническая сущность измерения отклонения частоты от номинальног

вого счетчика соединен с выходом пер-20 значения заключается в следующем.

Примем значение номи

тоты равным fр, а измер

При этом периоды ляются как 1

т „т j. f i f

За период Т, расхожд фронтов этих колебаний

30

личину

Т, Тд, если пе фазы этих колебаний был Через время t расхожден фронтов двух колебаний а так как нарастание ра происходит по линейному справедлива зависимость

Т. йТ

с учетом (1) получаем

вого элемента И 21 ,.

Блок вычислителей содержит распределитель 30 импульсов, первый и второй входы которого соединены с первым25 и вторым входами блока вычислителей, а пятый вход подключен к третьему входу распределителя 30, первьй и второй выходы ко.торого соединены с тактовыми входами соответственно регистров 31.1 и 31.2, информационные выходы которых подключены к информационным входам функционального ПЗУ 32, вход CS которого соединен с третьим выходом распределителя 30, а выходы ,5 подключены к первой группе выходов блока вычислителей, четвертый и пятый выхода распределителя 30 соединены соответственно с вторым и третьим выходами блока вьмислителей, третья 40 группа входов которого подключена к первым группам входов регистров 31.2 и 31.1, вторые группы входов которых соединены с четвертой группой входов блока вычислителей.

В состав распределителя 30 входит регистр 33, вход обнуления которого соединен с первым входом распределителя, второй вход которого подключен

к тактовому входу регистра 33, первый л частоты от номинального выход которого соединен с первыми входами восьмого 34 и девятого 35 элементов t И и через четвертый элемент НЕ 36 с тактовым и информационными входами шестого триггера 37, 55 прямой и инверсный выходы которого подключены к вторым входам соответственно восьмого 34 и девятого 35 элементов И, выходы которых соединены с

этих ч

(, - /

)

-{ f

Так как величина отклон от номинального значения

45 то

uf f - f

.. - -« f

о

Из зависимости (4) сл для нахождения величины

обходимо определить пер реднего фронта колебания сигнала ДТ за определе времени t, а частота f вестной.

Для решения поставле используется генератор нутых по фазе колебаний гается последовательным

вторым и первым входами распределителя 30, а выход восьмого элемента И 34 подключен к единичному входу седьмого триггера 38, инверсный выход которого соединен с третьим выходом распределителя 30, четвертый выход которого подключён к выходу десятого элемента И 39, первьш и второй входы которого соединены соответственно с прямым выходом шестого триггера 37 и вторым выходом четвертого регистра 33, третий выход которого подключен к входу установки в ноль седьмого 38 триггера и пятому выходу распределителя 30, третий вход которого соединен с входом установки в ноль шестого триггера 37,

Техническая сущность измерения отклонения частоты от номинального

Примем значение номинал ьной.частоты равным fр, а измеряемой

При этом периоды ляются как 1

т „т j. f i f

За период Т, расхождение передних фронтов этих колебаний составит ве- f j-i

этих частот опреде(1)

личину

Т, Тд, если первоначальные фазы этих колебаний были одинаковы. Через время t расхождение передних фронтов двух колебаний составит и Т, а так как нарастание разности фаз происходит по линейному закону, то справедлива зависимость

Т. йТ

(2)

с учетом (1) получаем

(, - /

),

-{ f о

Так как величина отклонения от номинального значения

то

uf f - f

.. - -« f

о

(3) (4)

частоты от номинального

Из зависимости (4) следует, что для нахождения величины отклонения

значения необходимо определить перемещение переднего фронта колебания входного сигнала ДТ за определенный интервал времени t, а частота f является известной.

Для решения поставленной задачи используется генератор с сеткой сдвинутых по фазе колебаний. Это достигается последовательным соедт1нением

513

генератора и секционированной линии задержки с отводами При этом нахождение начальной фазы входного сигнала сводится к определению, между какими сигналами номинальной частоты, с отводов линии задержки, находится передний фронт входного сигнала.

Это достигается путем использования регистра на базе D-триггеров, у которых на D-ВХОДЫ подается входной сигнал, а на С-входы - сигналы с отводов линии задержки При этом первый триггер регистра, который содержит единицу и на котором заканчивается ряд триггеров, содержащих нули, и начинается ряд триггеров, содержащих единицы, определяет номер отвода линии задержки, сигнал с которого совпадает по фазе с входным сигналом.

Аналогичное измерение производится через время t, после чего определяется разность .фаз входного сигнала между этими измерениями ЛТ и по формуле (4) определяется Af.

Сетка сдвинутых по фазе сигналов номинальной частоты создается за счет специального выбора частоты генератора, входящего в состав устройства:

Тг (1 +oi.) Т„, (5) где Т - период генератора устройства;

T(j - период номинальной частоты; Ы - коэффициент отклонения частоты генератора от номинальной частоты.

3 Примем, например, величину .(Л :у-.

Начальная разность фаз генератора и предполагаемого генератора номинальной частоты равна tj, (точка А на фиг.З). Спустя один период внутреннего генератора разность фаз составит величину .

t, mod. t,(l+ |-)Т, -

Ч

-Т 14 о

(точка Б на фиг.З).

Аналогично после первых риодов величина сдвигу фаз величины

±. mod

Г

То L

Ч- 5(Н у -) Т,

1

74 0

(точка А на фиг.З).

Сдвиг фаз между точками (фиг.З) составляет 1/14 TO

76

На основании изложенного выше получаем для точек 6-9 tg t + 4/14-Т„; t, to + 7/14-TO tg to + 10/14-Т„; t, t + 13/14.T,.

Как показано на фиг.З и по результатам расчета, точки А и А , Б и Б , Ви в , Г и г , Д и Д сдвинуты по отношению друг к другу на величину 1/14-Т,.

Десятый период внутреннего генератора имеет сдвиг фазы

t,o to + 2/14 То (фиг.З, точка А ).

Сдвиг по фазе между точками А и А составляет

21 1

1- + -- Т - t- - - Т - т 0 14 о 14 о 14 °

т.е. точки А и А также смещены по фазе на 1/14 часть периода номинальной частоты.

Аналогично точки А и А , Б и Б В и в , г и , д и д также

сдвинуты по фазе на величину 1/14 Т, причем фаза точки Д совпадает с фазой точки А, следовательно, по результатам расчета и построения следует, что фазы точек А и Б, Б и

В, в и Г, г и Д совпадают и процесс повторяется,

С целью пояснения возможности определения отклонения частоты от номинального значения с помощью сетки

сдвинутых частот на фиг.З показан график изменения фазы входного сиг- . нала, где KL - прямая линия, соединяющая положение фазы переднего фронта входного сигнала.

Прямая KL пересекает метки около 11-го периода внутреннего генератора и около 30-го периода.

Примем длительность шага линии задержки равной t . На 11-м периоде

линия KL пересекает 6-й шаг линии за- держки, другими словами, фронт вход- ног О сигнала приходится между фронтами сигналов с 6-го к 7-го отводов линии задержки, а на 30-м периоде пересекает 10-й шаг линии задержки.

При этом время между двумя этими моментами определяется как

t 30 т + 101; - iiTr - ег-

19 Тг + А-г 19 (1 + 3/14)Т(, +4 .

Определение перемещения фазы входного сигнала за время t осуществляется следующим образом.

713

Определяется фаза первой точки на 11-м периоде. При этом через 5 периодов фаза увеличивается на 1/14-1

о

за один период на S/IA T, Так как

11-й период можно записать как , то сдвиг фазы первой точки без учета ; смещения за счет отводов линии задержки равен

iT, t, -ь 2 - т Т

+ тт т.

а с учетом сдвига до 6-го отвода линии задержки этот сдвиг фаз в результате равен

м, йт, -f 6t t + f т„ + бг .

Расчет фазы второй точки производится аналогично, только дополнительно принимается во внимание то, что 14 периодов внутреннего генератора сохраняют сигналу первоначальную фазу.

Тридцатый период равен 30 2 14+2, следовательно

л т f- +7 Т (- + т i о - 14 о + 14 0С учетом смещения до 11 отвода линии задержки получаем

йт дт; + 11 t + т, + п-гг

Результирующее перемещение фазы входного сигнала за время t равно

йТ ЛТ - ЛТ, Y Т + 5 .

Подстановка полученных значений U Т и t в формулу (4) позволяет определить величину uf отклонения частоты от номинального значения.

Аналогичный расчет можно произвести применительно к заднему фронту входного сигнала, график изменения фазы которого приведен в виде прямой MN на фиг.3.

Устройство для измерения отклонения частоты от номинального значения работает следующим образом.

Измерение отклонения частоты от номинального значения осуществляется на определенном отрезке времени t, длительность которого определяется временем переполнения счетчика 20.

Период следования импульсов генератора 1 выбирается в соответствии с формулой (5).

Входной сигнал поступает на информационные входы D-триггеров регистра

78

3, на синхронизирующие входы которых поступают импульсы генератора 1 с отводов линии задержки 2.

Регистр) 3 фиксирует попадание ка- кого-либо фронта входного сигнала между фронтами сигналов, формируемых на отводах линии задержки 2.

Для обеспечения фиксации состояния крайних триггеров регистра 3 анализируются-элементом ИСКЛЮЧАЮЩЕЕ РШИ 8, который формирует сигнал на выходе при противоположных значениях уровней входных сигналов, кроме того, на триггерах 13 и 14 запоминается состояние

крайних триггеров регистра 3 до их неравнозначности.

Если до несовпадения оба крайних триггера регистра 3 находились в единице, то отперт элемент И 9 и в триггер 13 записывается единица; если же крайние триггеры регистра 3 находились в нулевом состоянии, то отпирается элемент И 12 и единица записывается в триггер 14.

Следовательно, если триггер 13 находится в единичном состоянии и на выходе элемента ИСКЛЮЧАКЩЕЕ ИЛИ 8 еди- ничный уровень сигнала, это значит, что зафиксирован фронт спада входного

сИ1 нала, а если в единичном состоянии находится триггер 14, то фиксируется фронт нарастания входного сигнала.

При срабатываний элемента ИСКЛЮЧАКЩЕЕ ИЛИ 8 через элемент И 15 осуществляется запись информации в регистр 4, за счет чего фиксируется состояние регистра 3 в момент нахождения одного из фронтов входного сигнала между фронтами сигналов, поступивших

с отводов линии задержки 2. Состояние триггеров регистра 4 анализируется сумматором 5 количества единиц (кото- рый может быть выполнен, например, на базе микросхем ПЗУ типа К 556РТ7).

Сумматор формирует на выходе двоичный код, значение которого равно количеству единиц в регистре 4.

Сумма единиц в регистре 4 необхо- дима для определения коэффициента при величине Т .

Счетчик 20 подсчитывает и оцифря- ет количество периодов генератора 1. При переполнении счетчика 20 триггер 18 устанавливается в единичное состояние и устройство отрабатывает результирующее значение отклонения частоты от номинального значения на определенном отрезке времени.

91

При нахождении триггера 18 в нулевом состоянии в момент срабатывания элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 отпираются элементы И 16 и 17 и триггеры 22 и 23 устанавливаются в единичное состояние в зависимости от того, какой из триггеров 13 или 14 находится в единичном состоянии.

Триггер 22 запускает блок 6 вычислителей, который осуществляет расчет величины отклонения частоты от номинального значения по перемещению фазы фронта спада входного сигнала, а триггер 23 запускает блок 7 вычислителей, который рассчитывает ту же величину по перемещению фазы фронта нарастания входного сигнала. Блоки 6 и 7 вычислителей имеют одинаковую структуру и работают аналогично .

При поступлении на первый вход блока вычислителей сигнала запуска начинает работать распределитель 30 импульсов (фиг.2), на вход которого поступает тактовая частота с второго входа блока вычислителей, подключенного к выходу генератора 1.

Сдвиговый регистр 33, входящий в состав распределителя 30 импульсов, формирует сдвинутые во времени импульсы на своих выводах. Импульсом начального сброса с пятого входа блока вычислителей через третий вход распреде лителя 30 импульсов триггер 37 переключается в нулевое состояние в результате чего первый импульс со сдвигового регистра 33 проходит через элемент И 35 на синхронизирующий вход регистра 31.2, через информационные входы которого в регистр; записывается код номера периода генератора 1 с выхода счетчика 20 и сумма количества единиц с выхода регистра 4 .

Далее сдвиговьй регистр 33 формирует импульс на втором выходе, который через пятый выход распределителя и третий выход блока вычислителей поступает на входы установки в ноль триггеров 22 или 23, один из которых (по потенциалу которого был запущен блок вычислителей) переключается в нулевое состояние.

Таким образом, в результате первого срабатывания элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 в регистр 31.2 блока вычислителей записываются параметры первого пересечения фронта входного сиг102710

нала и фронтов сигналов с вьшодов линии 2 задержки.

При повторном за время счета счетчика 20 срабатывании элемента ИСКЛЮ- 5 ЧАЩЕЕ ИЛИ 8 и запуске на расчет этого же блока вычислителей триггер- 37 находится в единичном состоянии. При этом первый импульс со сдвигового регистра 33 проходит через элемент И 34 на синхровход регистра 31,1.

В этот регистр производится запись параметров второго и каждого последующего пересечений фронта входного сигнала с фронтами сигналов с отводов линии 2 задержки, а именно номер периода генератора 1 и сумма количества единиц регистра 4.

Информация, записанная в регистры 31,1 и 31.2, используется для расчета 0 величины отклонения частоты от номинального значения uf.

Результат этого расчета считывается из функционального ПЗУ 32, в которое предварительно записываются результаты расчета для возможных исходных данных, которые для этого ПЗУ являются адресами, т.е. содержимое регистров 31.1 и 31,2 есть адреса ячеек ПЗУ 32, в которых записаны ре- 0 зультаты расчета величин uf по данным номеров периодов и количеству пе- ресеченных сигналов с линии 2 задержки .

5

Сигналом с выхода эл емента И 34 в единичное состояние устанавливается триггер 38, который формирует сигнал Выбор кристалла на функциональное ПЗУ 32. Импульс с второго вывода сдвигового регистра 33 через элемент И 39 поступает через четвертый выход распределителя 30 и второй выход блока вычислителей, а также элемент ИЛИ 26 на запускающий вход накапливающе- го сумматора 24 и на счетный вход счетчика 25. При этом каждый результат расчета Д f суммируется на накапливающем сумматоре 24 с предьщущими результатами, а счетчик 25 подсчитывает количество таких суммирований.

При переполнении счетчика 20 триггер 18 переключается в единичное состояние, при котором запираются элементы И 16 и 17, запревдая установку в единичное состояние триггеров 22 и 23.

По окончании расчета в блоке вычислителей переключается в нулевое состояние соответствующий триггер 22

или 23, в результате чего элемент И 29 отпирается и запускается регистр 28 сдвига. Импульсом с первого вывода регистра 28 сдвига срабатывает блок 27 деления, который осуществляет деление содержимого накапливающег сумматора 24 на содержимое счетчика 25, т.е. осуществляется усреднение результатов расчета путем их суммирования и деления на количество произведенных расчетов.

Блок 27 деления может быть вьтол- нен на ПЗУ, причем выходы накапливающего сумматора 24 счетчика 25 являются адресными входами ПЗУ, а управляющий сигнал регистра сдвига 28 - входом Выбора кристалла.

0 гистра соединен с первыми входами элемента ИСКЛЮЧАЩЕЕ ИЛИ,, третьего элемента И и входом первого элемента НЕ, а прямой выход последнего триггера первого регистра подключен к вто- 5 рым входам элемента ИСКЛЮЧАЩЕЕ PfflH, третьего элемента И и входу второго элемента НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом

Импульс со второго вывода регистра сдвига 28 обнуляет накапливающий второго элемента И и первыми входами

матор 24 и счетчик 25, а также устанавливает в нулевое состояние триггер IВ устройства и триггер 3 распределителя 30.

25

При этом устройство оказывается в исходном состоянии и готово для осуществления дальнейших измерений.

Формула изобретения

1. Устройство для измерения отклонения частоты от номинального значения, содержащее первый элемент И, выход которого соединен со счетным входом первого счетчика, отличающееся тем, что, с целью расширения динамического диапазона измеряемых частот, в него.дополнительно введены генератор импульсов, секционированная линия задержки, два регистра, два сумматора, два блока вычислителей, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, шесть элементов И, три элемента НЕ, пять триггеров, счетчикj элемент 1ШИ, блок деления, регистр сдвига, выход генератора импульсов соединен с первыми входами первого .и второго эле-, ментов И, :тактовыми входами первого, .второго, третьего и четвертого триггеров, с вторыми входами первого и

30

четвертого и пятого- элементов И, а выход второго элемента И подключен к тактовому входу второго регистра, выход третьего элемента И соединен с D-входами первого триггера, прямой выход которого подключен к второму входу четвертого элемента И, выходы первого и второго элементов НЕ соединены соответственно с первым и вторым входами шестого элемента И, выход которого подключен к D-входу второго триггера, прямой выход которого соеди нен с BTOpBiM входом пятого элемента И третьи входы четвертого и пятого элементов И подключены к второму входу первого элемента И и инверсному выходу пятого триггера, D- и С-входы которого соединены с выходом третьего эле-. мента НЕ, вход которого подключен к вьпсоду старшего разряда первого счетчика, информационные выходы которого соединены с третьей группой входов первого и второго блоков вычислителей третьи выходы первого и второго блоков вычислителей подключены к входам установки в О соответственно третьего и четвертого триггеров, D-входы которых соединены с выходами соот- ветственн о четвертого и пятого элементов И, прямые выходы третьего и четвертого триггеров подключены к первым входам соответственно первого и второго блоков вычислителей, а инверсные выходы третьего и четвертого

40

45

50

четвертого и пятого- элементов И, а выход второго элемента И подключен к тактовому входу второго регистра, выход третьего элемента И соединен с D-входами первого триггера, прямой выход которого подключен к второму входу четвертого элемента И, выходы первого и второго элементов НЕ соединены соответственно с первым и вторым входами шестого элемента И, выход которого подключен к D-входу второго триггера, прямой выход которого соеди нен с BTOpBiM входом пятого элемента И, третьи входы четвертого и пятого элементов И подключены к второму входу первого элемента И и инверсному выходу пятого триггера, D- и С-входы которого соединены с выходом третьего эле-. мента НЕ, вход которого подключен к вьпсоду старшего разряда первого счетчика, информационные выходы которого соединены с третьей группой входов первого и второго блоков вычислителей третьи выходы первого и второго блоков вычислителей подключены к входам установки в О соответственно третьего и четвертого триггеров, D-входы которых соединены с выходами соот- ветственн о четвертого и пятого элементов И, прямые выходы третьего и четвертого триггеров подключены к первым входам соответственно первого и второго блоков вычислителей, а инверсные выходы третьего и четвертого

50

второго блоков вычислителей, с тактовым входом первого регистра сдвига и входом секционированной линии задержки, выводы секций которой подключены к тактовым входам триггеров ре- триггеров соединены соответственно с

первым и вторым входами шестого элемента И, третий вход которого подключен к прямому выходу пятого триггера, а выход шестого элемента И соединен

гистра, информационные D-входы кото- :рых соединены между собой и подключены к входной шине устройства,а прямые . .выходы соединены с информационными

входами второго регистра, информационные выходы которого подключены к информационным входам первого сумматора, вход CS которого соединен с

шиной уровня логического нуля, а ин- формационные выходы подключены к группе четвертых входов первого и второго блоков вычислителей, причем прямой выход первого триггера первого регистра соединен с первыми входами элемента ИСКЛЮЧАЩЕЕ ИЛИ,, третьего элемента И и входом первого элемента НЕ, а прямой выход последнего триггера первого регистра подключен к вто- рым входам элемента ИСКЛЮЧАЩЕЕ PfflH, третьего элемента И и входу второго элемента НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом

второго элемента И и первыми входами

второго элемента И и первыми входами

четвертого и пятого- элементов И, а выход второго элемента И подключен к тактовому входу второго регистра, выход третьего элемента И соединен с D-входами первого триггера, прямой выход которого подключен к второму входу четвертого элемента И, выходы первого и второго элементов НЕ соединены соответственно с первым и вторым входами шестого элемента И, выход которого подключен к D-входу второго триггера, прямой выход которого соединен с BTOpBiM входом пятого элемента И, третьи входы четвертого и пятого элементов И подключены к второму входу первого элемента И и инверсному выходу пятого триггера, D- и С-входы которого соединены с выходом третьего эле-. . мента НЕ, вход которого подключен к вьпсоду старшего разряда первого счетчика, информационные выходы которого соединены с третьей группой входов первого и второго блоков вычислителей, третьи выходы первого и второго блоков вычислителей подключены к входам установки в О соответственно третьего и четвертого триггеров, D-входы которых соединены с выходами соот- ветственн о четвертого и пятого элементов И, прямые выходы третьего и четвертого триггеров подключены к первым входам соответственно первого и второго блоков вычислителей, а инверсные выходы третьего и четвертого

триггеров соединены соответственно с

с входом обнуления регистра сдвига,- первый выход которого подключен к входу CS блока деления, а второй соединен с входом установки в ноль пятого триггера, входами обнуления второго сумматора и второго счетчика и пятыми входами первого и второго блоков вычислителей, первые группы выходов которого соединены с информационными входами второго сумматора, тактовый вход которого соединен со счетным входом второго счетчика и выходом элемента ИЛИ, входы которого подключены к вTOpbiM выходам первого и второго блоков вычислителей, информаци- онные выходы второго сумматора соеди- нень с первой группой входов блока деления, вторая группа информационных входов которого подключена к информационным выходам второго счетчи- ка, а выходы блока деления являются выходами устройства,

2. Устройство rib п., о т л и - ч ающе е ся тем, что блок вычис- лителей содержит распределитель импульсов, два регистра и функциональное ПЗУ, причем первый и второй входы расг/ределителя импульсов соединены с первым и вторым входами блока вы- числителей, пятый вход которого подключен к третьему входу распределителя, первый и второй выходы которого соединены с тактовыми входами соответственно пятого и шестого регистров информационные выходы которых подключены к информационным входам функхдао- напьного ПЗУ, вход CS которого соединен с третьим выходом распределителя а выходы подключены к первой группе выходов блока вычислителей, четвертый и пятый выходы распределителя соединены соответственно с вторым и третьим выходами блока вычислителей, третья группа входов которого подключена к первым группам входов пятого и шестого регистров, вторые группы входов которых соединены с четвертой группой входов блока вычислителей.

3, Устройство по п.1, о т л и - чающееся тем, что в состав распределителя входят регистр сдвига элемент НЕ два триггера и три эле- мента НЕ, причем вход обнуления регистра сдвига соединен с первым входом распределителя, второй вход которого подключен к taKTOBOMy входу регистра сдвига, первый выход которого соединен с первыми входами восьмого и девятого элементов И и через четвертый элемент НЕ с тактовым и информационным входами шестого триггера, прямой и инверсный выходы которого подключены к вторым входам соответственно восьмого и девятого элементов И выходы которых; соединены с вторым и первым выходами распределителя, а выход восьмого элемента И подключен к единичному входу седьмого триггера, инверсный выход которого соединен с третьим выходом распределителя, четвертый выход которого подключен к выходу десятого элемента И, первый и .второй входы которого соединены соответственно с прямым выходом шестого триггера и вторым выходом регистра сдвига, третий выход которого подключен к входу установки в О седьмого триггера и пятому выходу распределителя, третий вход которого соединен с входом установки в О шестого триггера.

Фиг7

-vfl 14

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Устройство для автоматической подстройки частоты | 1984 |

|

SU1298912A1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для измерения временных интервалов | 1982 |

|

SU1034009A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

Устройство для измерения отклонения частоты от номинального значения содержит генератор, секционированную линию задержки, регистры, сумматор количества единиц, блоки вычислителей, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И, элементы НЕ, триггеры, счетчики, накапливающий сумматор, элемент ИЛИ, блок деления и регистр сдвига. Устройство имеет расширенный динамический диапазон измеряемых час- TOV. В описании изобретения приведены электрические схемы блоков вычислителей и распределителя. 2 з.п. ф-лы, 3 ил.

Редактор М.Циткина

Составитель Ю.Шишкин

Техред М.Ходамич Корректор М.Пожо

Заказ 1903/56Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35„ Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для измерения временных интервалов | 1982 |

|

SU1034009A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ПРЕОБРАЗОВАТЕЛЬ «ЧАСТОТА-КОД» | 0 |

|

SU300133A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-15—Публикация

1985-05-22—Подача