. Изобретение относится к автоматике и может быть использовано в системах передачи цифровой информации.

Цель изобретения - повышение помехоустойчивости преобразования.

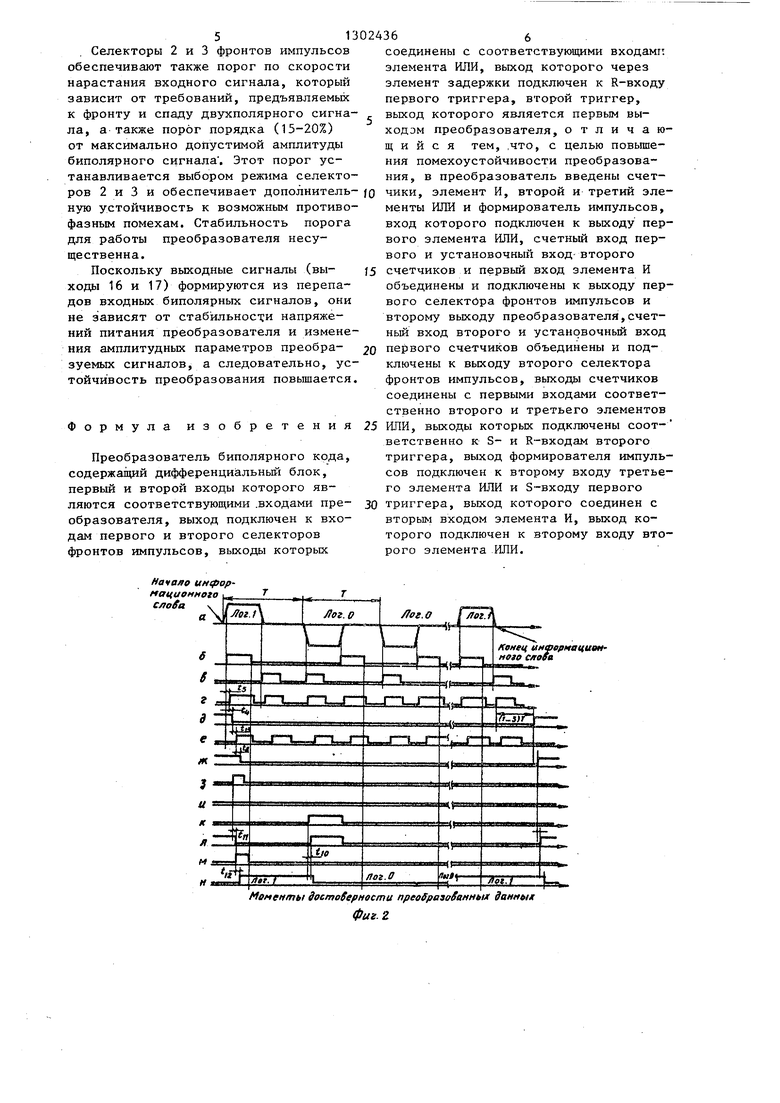

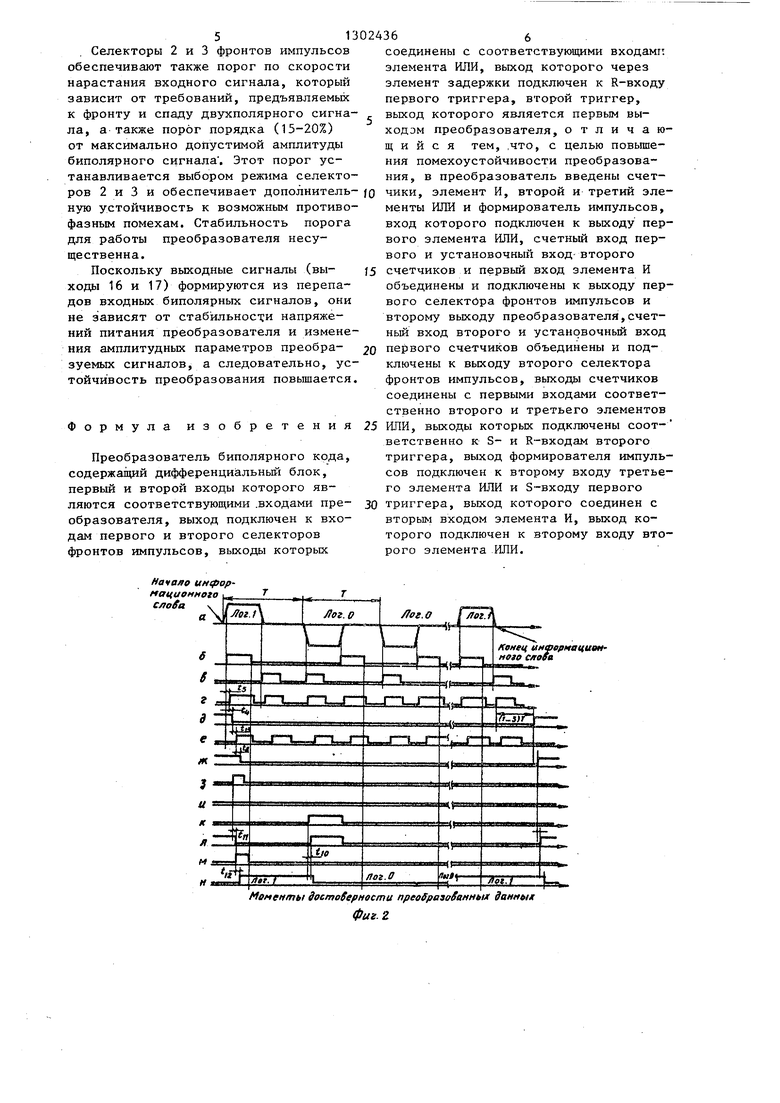

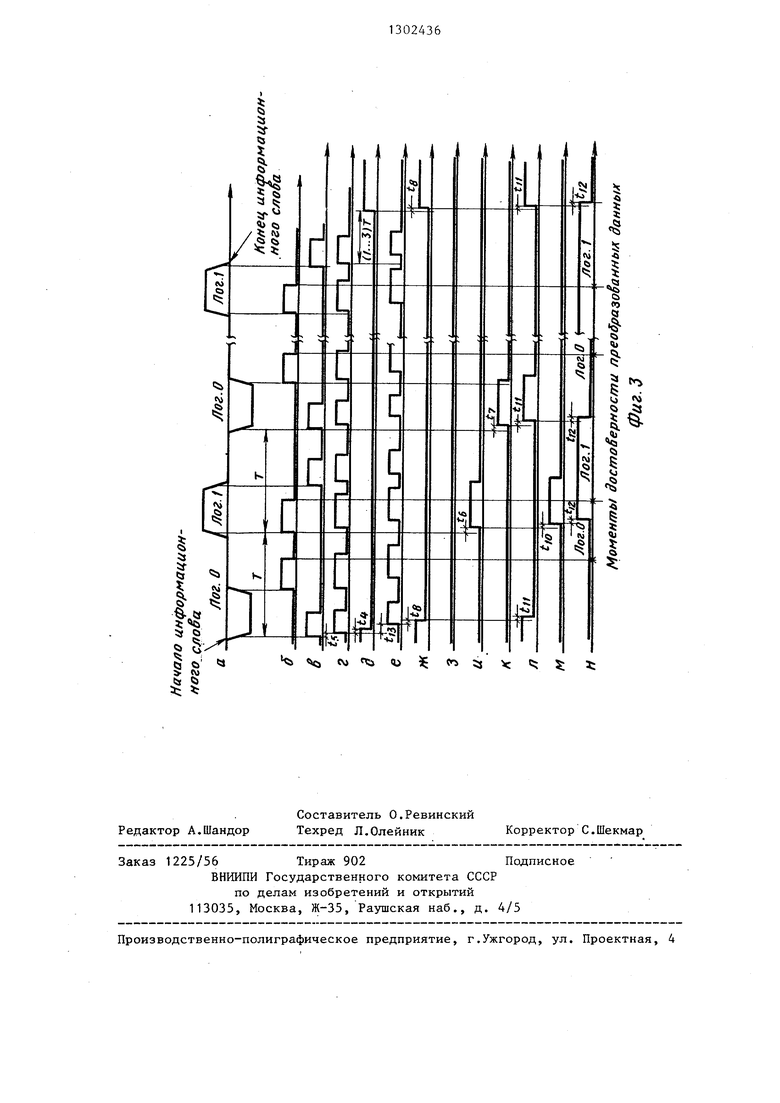

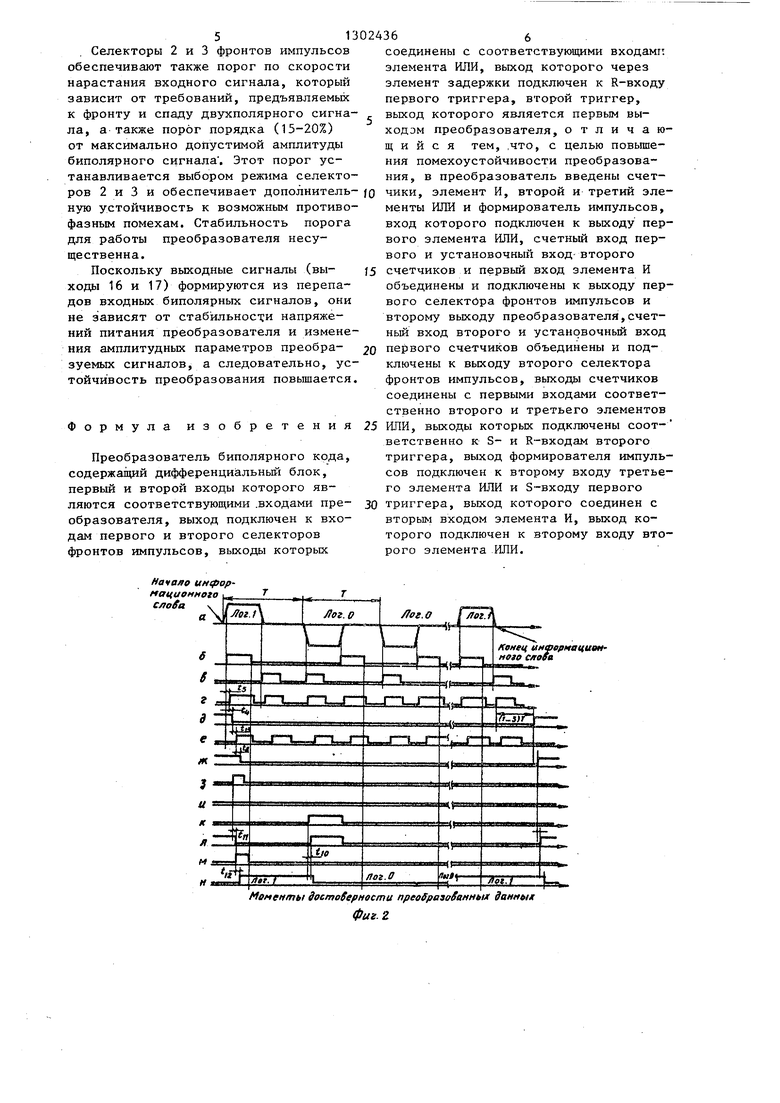

На фиг.1 представлена функциональная схема преобразователя; на фиг.2 и 3 - временные диаграммы, поясняющие его работу.

Преобразователь биполярного кода содержит дифференциальный блок 1, первый 2 и второй 3 селекторы фронтов импульсов, формирователь 4 импульсов, первый элемент ИЛИ 5, первы 6 и второй 7 счетчики, первый триггер 8, элемент И 9, второй 10 и третий 11 элементы ИЛИ, второй триггер 12, элемент 13 задержки. На фиг.1 обозначены первый 14 и второй 15 входы, первый 16 и второй 17 выходы.

Дифференциальный блок 1 выполнен на дифференциальном усилителе, что обеспечивает по сравнению с трансформаторным каскадом повышение входного сопротивления.

На. фиг.2 и 3 обозначено: а - сигналы на первом входе 14 преобразователя; б - сигналы.на выходе первого селектора 2 фронтов импульсов (выход 17); в - сигналы на .выходе второго селектора 3 фронтов импульсов; г - сигналы на выходе первого элемента ИЛИ 5; д - сигнал на выходе формирователя 4 импульсов; е - сигналы на выходе элемента 13 задержки; ж - сигнал на выходе первого триггера 8; 3 - сигнал на выходе элемента И 9; и, к - сигналы на выходах соответственно первого и второго счетчиков 6 и 7; л, м - сигналы соответственно на R- и S-входах второго триггера 12; н - сигналы на выходе второго триггера 12 (выход 16),

ющий выход триггера 8 в состоянии ло- Преобразователь работает следующим 45 гической- 1, и задерживает переклюобразом.

Сигналы биполярного кода поступа-- ют на входы 14 и 15 преобразователя в общем случае в виде последовательности п-разрядных слов, отделенных одно от другого временным интервалом в m периодов Т частоты передачи бит информации, во время которого напряжения обоих сигналов двухполярного кода равно в идеальном случае нулю.

Таким образом, передача одного информационного слова занимает временной интервал пТ, а интервал между словами - тТ, где m - положительные, an 50

чение этого триггера 8 настолько, чтобы первый импульс с выхода элемента ИЛИ 5 успел пройти через открытый элемент И 9 и при этом имел бы длительность, достаточную для срабатывания триггера 12.

Формирователь 4 импульсов служит для выявления момента окончания пере- 55 дачи информационного слова. По окончании п-разрядного входного слова после того, как на выходе элемента ШШ 5 появится нулевой уровень, формирователь 4 импульсов через время

положительные и целые числа. В диф- фере щисшьном блоке 1 происходит взаимное вычитание входных сигналов, позволяющее подавать синфазные помехи,

которые могут оказаться во входном сигнале. Далее сигнал поступает на входы селектород 2 и 3 фронтов импульсов, импульсы на выходах которых формируютсяj соответственно, по положительному и отрицательному фронтам входного сигнала. Длительность формируемых на их выходах импульсов устанавливается в зависимости от быстродействия элементной базы, на которой реализуется преобразователь.

Длительность импульса на выходе второго селектора 3 должна обеспечивать устойчивое срабатывание счетчиков 6 и 7 и триггера 12, а на выходе

первого селектора 2, формирующего тактовые импульсы на выходе 17, еще и превышать время распространения сигнала по пути: вход элемента ИЛИ 5 - выход триггера 12. Таким выбором длительности тактовых импульсов обеспе- чивается устойчивая привязка их спада к сигналу на выходе 16, что существенно для последующей обработки преобразованных сигналов, например,

для преобразования последовательных данных в параллельные.

Импульсы с выхода первого селектора 2 фронтов импульсов запускают формирователь 4 импульсов и через

элемент 13 задержки поступают на R- вход триггера 8, устанавливая на его выходе логический О.

При этом элемент 13 задержки выполняет две функции: задерживает появление импульса на R-входе триггера 8 до тех пор, пока не сработает формирователь 4 импульсов .и не исчезнет уровень на S-входе, удержива

чение этого триггера 8 настолько, чтобы первый импульс с выхода элемента ИЛИ 5 успел пройти через открытый элемент И 9 и при этом имел бы длительность, достаточную для срабатывания триггера 12.

Формирователь 4 импульсов служит для выявления момента окончания пере- 55 дачи информационного слова. По окончании п-разрядного входного слова после того, как на выходе элемента ШШ 5 появится нулевой уровень, формирователь 4 импульсов через время

(1-3)Т вырабатывает на своем выходе уровень логической 1, который устанавливает на выходе триггера 8 уровень логической 1, а на выходе триггера 12 - уровень логического О. В этом состоянии триггеры 8 и 12 удерживаются до. тех пор, пока на входы 14 и 15 преобразователя не придет очередное информационное слово.

Если в начале очередного информа- JQ ционного слова передается логическая 1, то первый импульс появляется на выходе первого селектора 2 фронтов импульсов (фиг.2), который вырабатывает выходной импульс по положитель- f5 ному фронту входного сигнала. Этот импульс, проходя через элемент ИЛИ 5, запускает формирователь 4 импульсов, и через открытый элемент 9 и элемент

ИЛИ 10 устанавливает на выходе триг- 20 гера 12 уровень логической 1. На выходе формирователя 4 импульсов с задержкой по отношению к входному импульсу формируется уровень логическо

35

го О. При этом триггер 8 по S-BXO- 25 (3 или.2) формируется подряд два им- ду и триггер 12 по R-входу оказывают- пульса. Эти импульсы располагаются ся отпущенными.,между двумя соседними импульсами усЧерез время, определяемое элемен- тановки, которые формируются по соот- том 13 задержки, этот же импульс появляется на R-входе триггера 8, устанавливая на его выходе уровень логического О, который запирает элемент И 9 и блокирует прохождение импульсов через него. Поскольку логический О на выходе формирователя 4 импульсов сохраняется до конца преобразуемого слова, то и элемент И 9 заперт все это время. Управление триггером 12 после приема первого бита информационного слова осуществляется 40 гический.0 (1), то изменения сос- счетчиками 6 и 7 через элементы ИЛИ тояния триггера 12 не происходит, 10 и 11.

Если в начале информационного слова передается логический О, то первым на выходе блока 1 появляется от- 45 де не может появиться прдряд два им- ридательный фронт импульса, по кото- пульса и, следовательно, на выходе рому на выходе второго селектора 3 счетчика 7 (6) не появляется актив- формируется импульс. Этот импульс ньй логический сигнал, приводящий к через элемент ИЛИ 5 запускает форми- изменению состояния триггера 12. На рователь 4 импульсов, а через элемент50 выходе триггера 12 сохраняется ло- 13 задержки устанавливает на выходе гический уровень, который образовался триггера 8 логический уровень, запрещающий прохождение импульсов через элемент И 9. Кроме того, этот импульс устанавливает в начальное состояние 55 счетчик 6 и увеличивает на единицу число в счетчике 7. Поскольку после окончания предыдущего информационветствующему фронту на выходе селек- 30 тора 2 или 3. При этом на выходе счетчика 7 (6) появляется активный логический уровень, который через элемент ИЛИ 11 (10) устанавливает триггер 12 в состояние логического О (1).

Если во входной информации не происходит изменений в передаваемьрс данных, т.е. непрерывно в течение нескольких бит информации передается лопоскольку между двумя соседними импульсами, приходящими на вход установки счетчика 7 (6), на счетном вхопри приеме предыдущего бита информации.

Выходные преобразованные данные достоверны в моменты окончания импульсов на выходе первого селектора 12 фронтов импульсов. При этом длительность импульсов входных сигналов может быть любой.

ноге слова триггер 12 был установлен ср1гналом с выхода формирователя 4 импульсов в состояние логического О, то его состояние не изменяется, а на выходе сохраняется логический О.

После приема первого бита информационного слова управление триггером 12 осуществляется счетчиками 6 и 7, которые формируют управляющие сигналы в моменты изменения входной информации с логического О на 1 - счетчик 6, ас логической 1 на О счетчик 7. На выходах счетчиков 6 и 7 происходит изменение логического состояния, если между соседними импульсами установки придет два счетных импульса .

Если во входной информации происходит изменение передаваемых данных

0 на 1 (с 1

на

с логического

О), то на выходе дифференциальног 5 блока 1 образуется подряд друг за другом два одинаковых фронта (фиг.З). На выходе соответствующего селектора

35

тановки, которые формируются по соот- 40 гический.0 (1), то изменения сос- тояния триггера 12 не происходит,

ветствующему фронту на выходе селек- 30 тора 2 или 3. При этом на выходе счетчика 7 (6) появляется активный логический уровень, который через элемент ИЛИ 11 (10) устанавливает триггер 12 в состояние логического О (1).

Если во входной информации не происходит изменений в передаваемьрс данных, т.е. непрерывно в течение нескольких бит информации передается лотановки, которые формируются по соот- гический.0 (1), то изменения сос- тояния триггера 12 не происходит,

де не может появиться прдряд два им- пульса и, следовательно, на выходе счетчика 7 (6) не появляется актив- ньй логический сигнал, приводящий к изменению состояния триггера 12. На выходе триггера 12 сохраняется ло- гический уровень, который образовался

поскольку между двумя соседними импульсами, приходящими на вход установки счетчика 7 (6), на счетном входе не может появиться прдряд два им- пульса и, следовательно, на выходе счетчика 7 (6) не появляется актив- ньй логический сигнал, приводящий к изменению состояния триггера 12. На выходе триггера 12 сохраняется ло- гический уровень, который образовался

при приеме предыдущего бита информации.

Выходные преобразованные данные достоверны в моменты окончания импульсов на выходе первого селектора 12 фронтов импульсов. При этом длительность импульсов входных сигналов может быть любой.

Селекторы 2 и 3 фронтов импульсов обеспечивают также порог по скорости нарастания входного сигнала, который зависит от требований, предъявляемых к фронту и спаду двухполярного сигнала, а также порог порядка (15-20%) от максимально допустимой амплитуды биполярного сигнала . Этот порог устанавливается выбором режима селекторов 2 и 3 и обеспечивает дополнитель ную устойчивость к возможным противофазным помехам. Стабильность порога для работы преобразователя несущественна.

Поскольку выходные сигналы (выходы 16 и 17) формируются из перепадов входных биполярных сигналов, они не зависят от стабильнос1;и напряжений питания преобразователя и изменения амплитудных параметров преобразуемых сигналов, а следовательно, устойчивость преобразования повышается

-

Формула изобретения

Преобразователь биполярного кода, содержащий дифферендиальный блок, первый и второй входы которого являются соответствующими .входами преобразователя, выход подключен к входам первого и второго селекторов фронтов импульсов, выходы которых

Начало инфор- нацио c/iofa

Моменты SocmofepHocmu прео6разо1анн а данных фиг. 2.

соединены с соответствующими входамп элемента ИЛИ, выход которого через элемент задержки подключен к R-входу первого триггера, второй триггер, выход которого является первым выходом преобразователя, отличающийся тем, ,что, с целью повышения помехоустойчивости преобразования, в преобразователь введены счет- fO чики, элемент И, второй и третий элементы ИЛИ и формирователь импульсов, вход которого подключен к выходу первого элемента ИЛИ, счетный вход первого и установочный вход-второго

15 счетчиков и первый вход элемента И объединены и подключены к выходу первого селектора фронтов импульсов и второму выходу преобразователя,счет- ньй вход второго и устаиовочньй вход

20 первого счетчиков объединены и подключены к выходу второго селектора фронтов импульсов, выходы счетчиков соединены с первыми входами соответственно второго и третьего элементов

25 ИЛИ, выходы которых подключены соот- ветственно к S- и R-входам второго триггера, выход формирователя импульсов подключен к второму входу третьего элемента ИЛИ и S-входу первого

30 триггера, выход которого соединен с вторым входом элемента И, выход которого подключен к второму входу второго элемента ИЛИ.

Редактор А.Шандор

Составитель О.Ревинский Техред Л.Олейник

Заказ 1225/56 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1453598A1 |

| Устройство магнитной записи-воспроизведения импульсных сигналов | 1983 |

|

SU1068985A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| Устройство для передачи и приема данных | 1986 |

|

SU1383430A2 |

| Селектор сигналов | 1989 |

|

SU1732451A1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Устройство для передачи и приема данных | 1988 |

|

SU1583954A1 |

| Устройство для передачи и приема данных | 1984 |

|

SU1196936A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

Изобретение относится к автоматике. Его использование в системах передачи цифровой информации позволяет повысить помехоустойчивость преобразования. Преобразователь биполярного кода содержит дифференциальный блок 1, селекторы 2, 3 фронтов импульсов, элемент ИЛИ 5, триггеры 8, 12 и элемент 13 задержки. Введение формирователя 4 импульсов, счетчиков . 6, 7, элемента И 9, элементов ИЛИ 10, 11 обеспечивает работу преобразователя с импульсами любой длительности независимо от стабильности питающих напряжений и от изменений амплитудных параметров входного сигнала.3 ил. iplti.i

| Устройство для приема биимпульсного сигнала | 1979 |

|

SU782171A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Преобразователь кода | 1982 |

|

SU1051708A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-07—Публикация

1985-06-27—Подача