Изобретение относится к стековым запо- мииаюн1,им устройствам.

Цель изобретения - расширение области применения устройства за счет записи и чтения данных в начало массива.

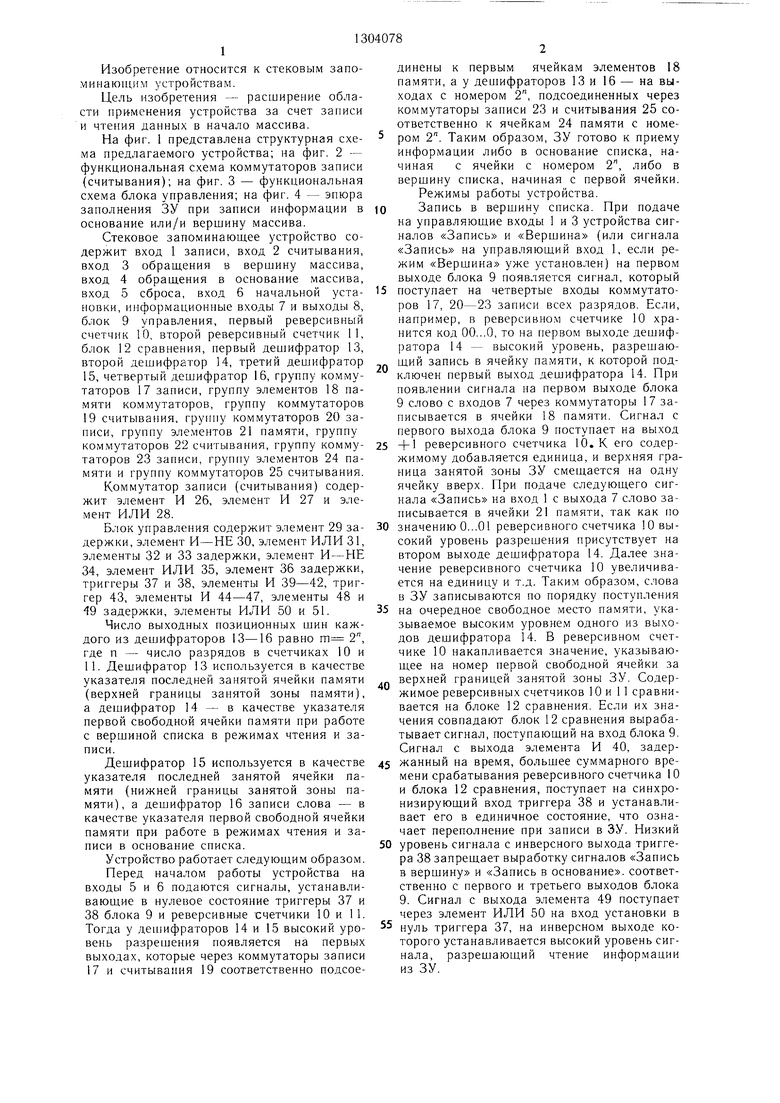

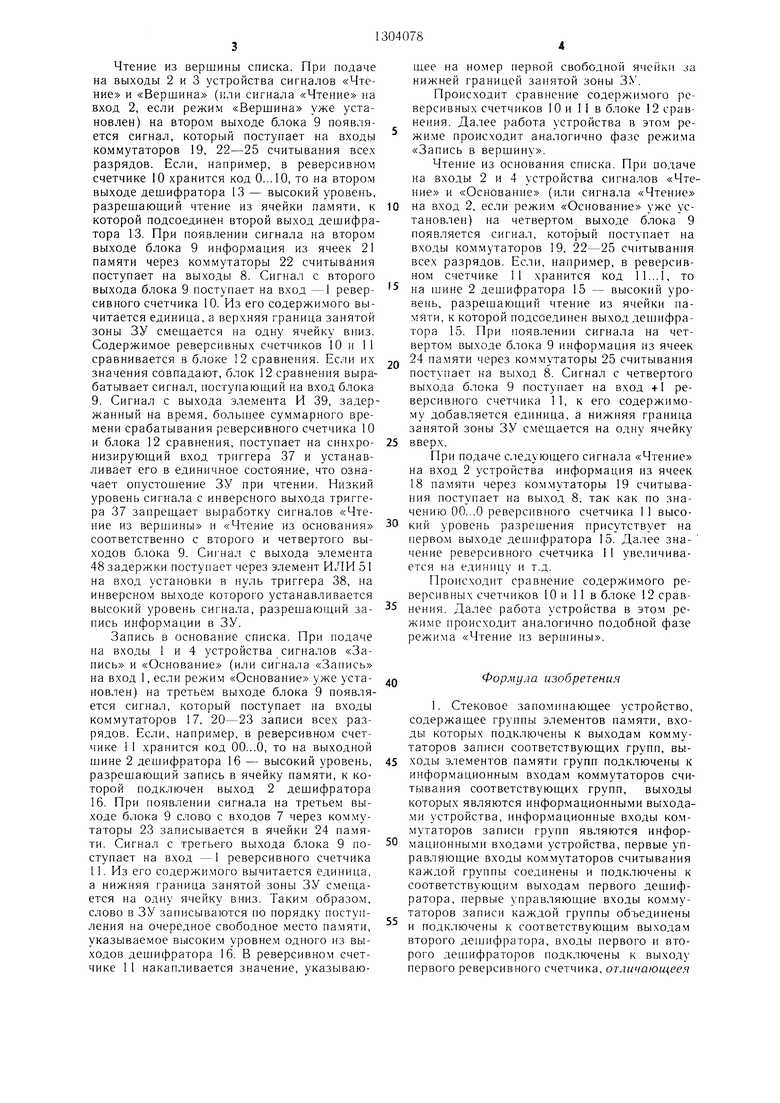

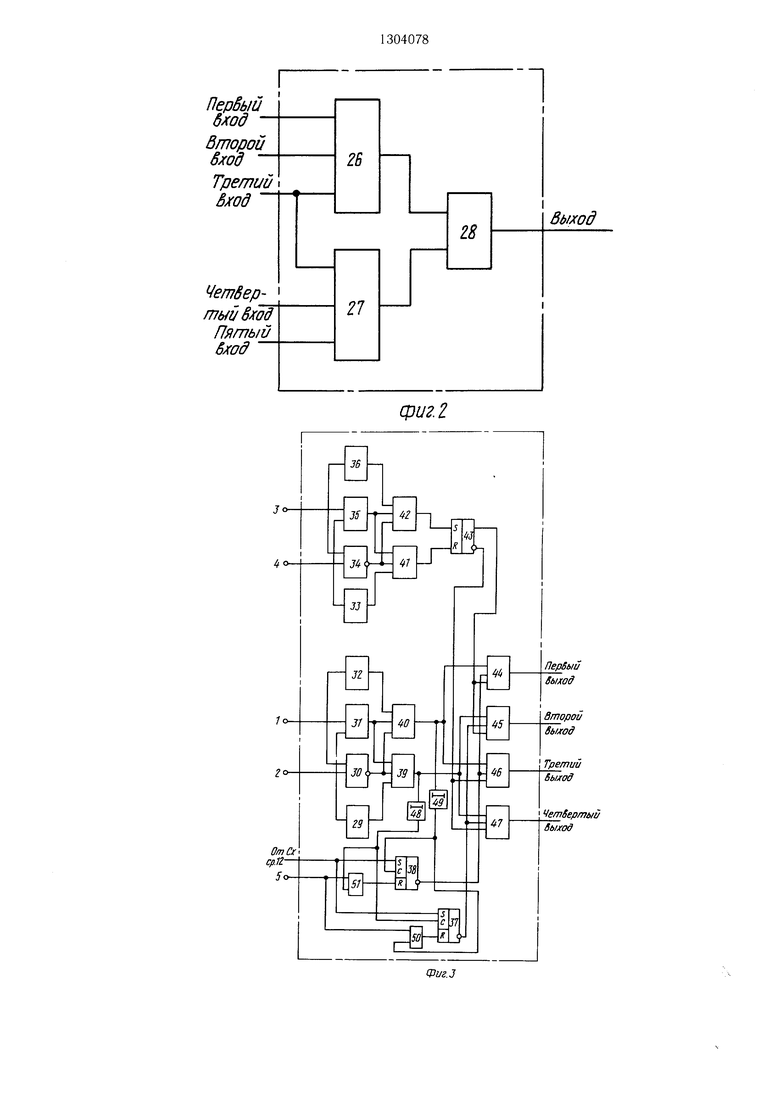

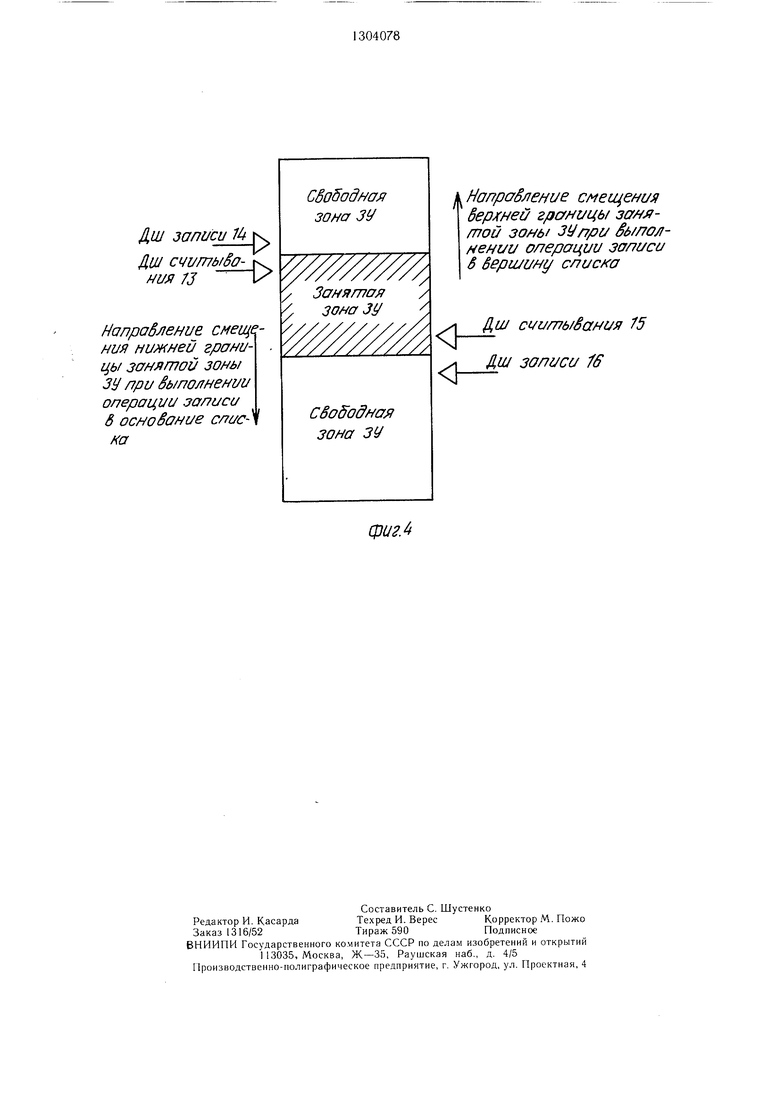

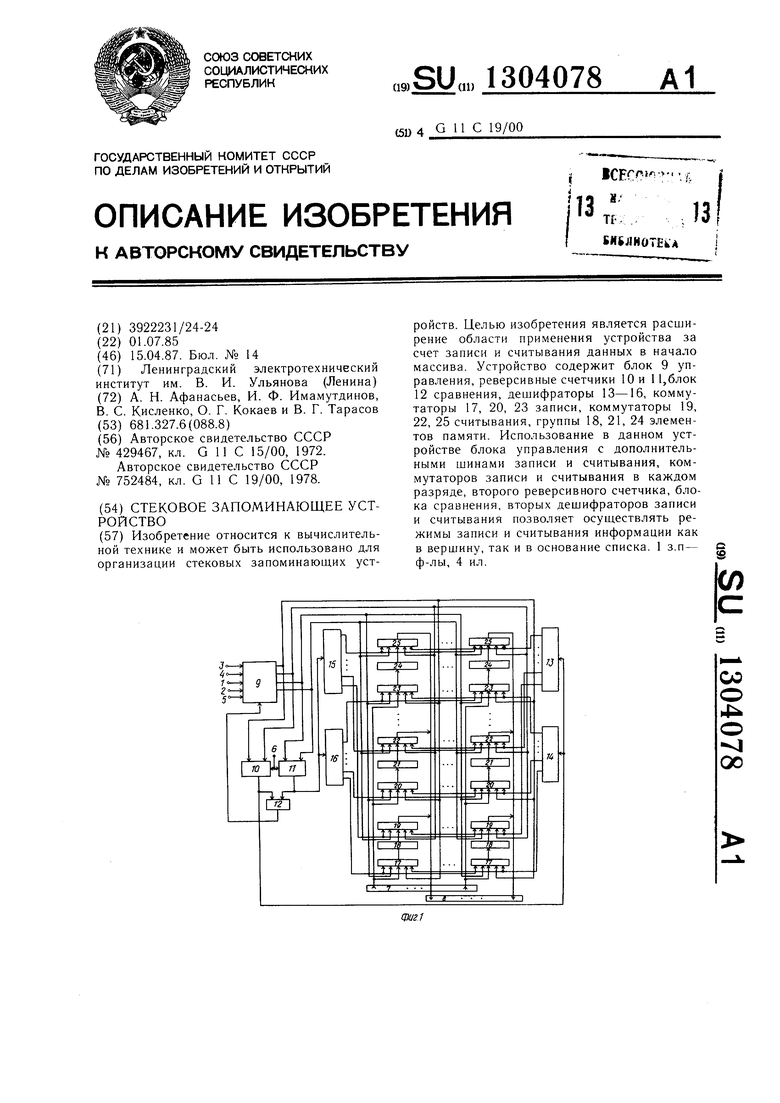

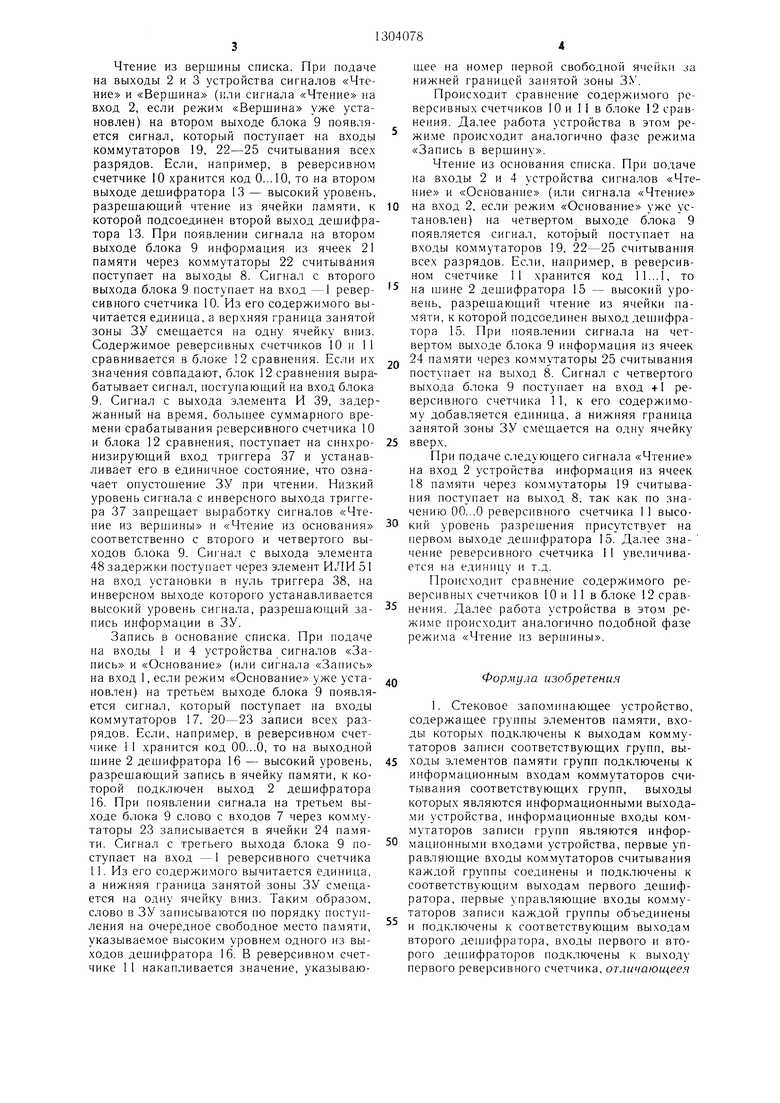

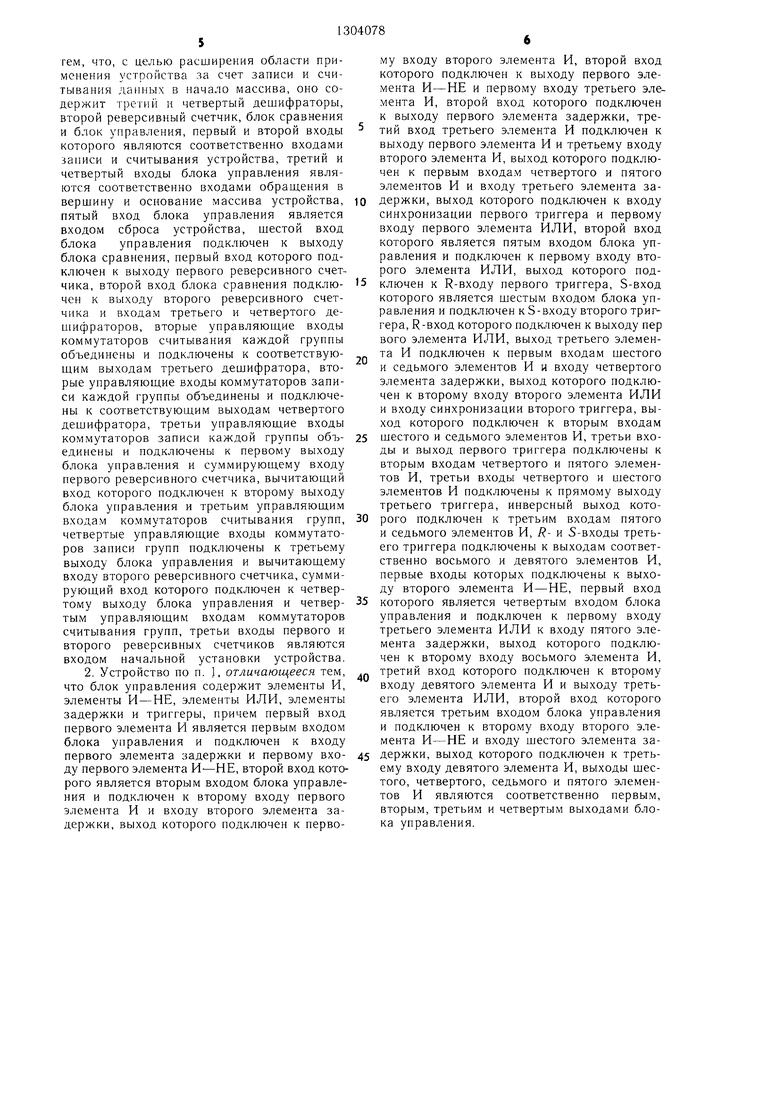

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема коммутаторов записи (считывания); на фиг. 3 - функциональная схема блока управления; на фиг. 4 - эпюра заполнения ЗУ при записи информации в основание или/и вершину массива.

Стековое запоминающее устройство содержит вход 1 записи, вход 2 считывания, вход 3 обращения в вершину массива, вход 4 обращения в основание массива, вход 5 сброса, вход 6 начальной установки, информационные входы 7 и выходы 8, блок 9 управления, первый реверсивный счетчик Го, второй реверсивный счетчик И, блок 12 сравнения, первый дешифратор 13, второй дешифратор 14, третий дешифратор 15, четвертый дешифратор 16, группу коммутаторов 17 записи, группу элементов 18 памяти коммутаторов, группу коммутаторов 19 считывания, группу коммутаторов 20 записи, группу элементов 21 памяти, группу коммутаторов 22 считывания, группу коммутаторов 23 записи, группу элементов 24 памяти и группу коммутаторов 25 считывания.

Коммутатор записи (считывания) содержит элемент И 26, элемент И 27 и элемент ИЛИ 28.

Блок управления содержит элемент 29 задержки, элемент И-НЕ 30, элемент ИЛИ 31, элементы 32 и 33 задержки, элемент И-НЕ 34, элемент ИЛИ 35, элемент 36 задержки, триггеры 37 и 38, элементы И 39-42, триггер 43, элементы И 44-47, элементы 48 и 9 задержки, элементы ИЛИ 50 и 51.

Число выходных позиционных шин каждого из дешифраторов 13-16 равно т 2, где п - число разрядов в счетчиках 10 и 11. Дешифратор 13 используется в качестве указателя последней занятой ячейки памяти (верхней границы занятой зоны памяти), а дешифратор 14 - в качестве указателя первой свободной ячейки памяти при работе с вершиной списка в режимах чтения и записи.

Дешифратор 15 используется в качестве указателя последней занятой ячейки памяти (нижней границы занятой зоны памяти), а дешиффатор 16 записи слова - в качестве указателя первой свободной ячейки памяти при работе в режимах чтения и записи в основание списка.

Устройство работает следующим образом.

Перед началом работы устройства на входы 5 и 6 подаются сигналы, устанавливающие в нулевое состояние триггеры 37 и 38 блока 9 и реверсивные счетчики 10 и 11. Тогда у дешифраторов 14 и 15 высокий уровень разрешения появляется на первых выходах, которые через коммутаторы записи 17 и считывания 19 соответственно подсое

динены к первым ячейкам элементов 18 памяти, а у дешифраторов 13 и 16 - на выходах с номером 2, подсоединенных через коммутаторы записи 23 и считывания 25 соответственно к ячейкам 24 памяти с номером 2. Таким образом, ЗУ готово к приему информации либо в основание списка, начиная с ячейки с номером 2, либо в вершину списка, начиная с первой ячейки. Режимы работы устройства.

Запись в вершину списка. При подаче на управляющие входы 1 и 3 устройства сигналов «Запись и «Вершина (или сигнала «Запись на управляющий вход 1, если режим «Вершина уже установлен) на первом выходе блока 9 появляется сигнал, который

поступает на четвертые входы коммутаторов 17, 20-23 записи всех разрядов. Если, например, в реверсивном счетчике 10 хранится код 00...О, то на первом выходе дешифратора 14 - высокий уровень, разрешающий запись в ячейку памяти, к которой подключен первый выход дешифратора 14. При появлении сигнала на первом выходе блока 9 слово с входов 7 через коммутаторы 17 записывается в ячейки 18 памяти. Сигнал с первого выхода блока 9 поступает на выход

+1 реверсивного счетчика 10. К его содержимому добавляется единица, и верхняя граница занятой зоны ЗУ смещается на одну ячейку вверх. При подаче следующего сигнала «Запись на вход 1 с выхода 7 слово записывается в ячейки 21 памяти, так как по

значению 0...01 реверсивного счетчика 10 высокий уровень разрешения присутствует на втором выходе дешифратора 14. Далее значение реверсивного счетчика 10 увеличивается на единицу и т.д. Таким образом, слова в ЗУ записываются по порядку поступления

на очередное свободное .место памяти, указываемое высоким уровне.м одного из выходов дешифратора 14. В реверсивном счетчике 10 накапливается значение, указывающее на номер первой свободной ячейки за верхней границей занятой зоны ЗУ. Содержимое реверсивных счетчиков 10 и 11 сравнивается на блоке 12 сравнения. Если их значения совпадают блок 12 сравнения вырабатывает сигнал, поступающий на вход блока 9. Сигнал с выхода элемента И 40, задержанный на время, большее суммарного времени срабатывания реверсивного счетчика 10 и блока 12 сравнения, поступает на синхронизирующий вход триггера 38 и устанавливает его в единичное состояние, что означает переполнение при записи в ЗУ. Низкий

уровень сигнала с инверсного выхода триггера 38 запрещает выработку сигналов «Запись в вершину и «Запись в основание, соответственно с первого и третьего выходов блока 9. Сигнал с выхода элемента 49 поступает через элемент ИЛИ 50 на вход установки в

нуль триггера 37, на инверсном выходе которого устанавливается высокий уровень сигнала, разрешаюший чтение информации из ЗУ.

Чтение из вершины списка. При подаче на выходы 2 и 3 устройства сигналов «Чтение и «Вершина (или сигнала «Чтение на вход 2, если режим «Вершина уже установлен) на втором выходе блока 9 появ:1я- ется сигнал, который поступает на входы коммутаторов 19, 22-25 считывания всех разрядов. Если, например, в реверсивном счетчике 10 хранится код 0...10, то на втором выходе дешифратора 13 - высокий уровень, разрешаюш,ий чтение из ячейки памяти, к которой подсоединен второй выход дешифратора 13. При появлении сигнала на втором выходе блока 9 информация из ячеек 21 памяти через коммутаторы 22 считывания поступает па выходы 8. Сигнал с второго выхода блока 9 поступает на вход -1 реверсивного счетчика 10. Из его содержимого вычитается единица, а верхняя граница занятой зоны ЗУ смещается на одну ячейку вниз. Содержимое реверсивных счетчиков 10 и 11 сравнивается в блоке 12 сравнения. Если их значения совпадают, блок 12 сравнения вырабатывает сигнал, поступаюш,ий на вход блока 9. Сигнал с выхода элемента П 39, задержанный на время, большее суммарного времени срабатывания реверсивного счетчика 10 и блока 12 сравнения, поступает на синхронизирующий вход триггера 37 и устанавливает его в единичное состояние, что означает опустошение ЗУ при чтении. Низкий уровень сигнала с инверсного выхода триггера 37 запрещает выработку сигналов «Чтение из BepujHHbi и «Чтение из основания соответственно с второго и четвертого выходов блока 9. Сигнал с выхода элемента 48 задержки поступает через элемент ИЛИ 51 на вход установки в нуль триггера 38, на инверсном выходе которого устанавливается высокий уровень сигнала, разрешающий запись информации в ЗУ.

Запись в основание списка. При подаче на входы 1 и 4 устройства сигналов «Запись и «Основание (или сигнала «Запись на вход 1, если режим «Основание уже установлен) на третьем выходе блока 9 появляется сигнал, который поступает на входы коммутаторов 17, 20-23 записи всех разрядов. Если, например, в реверсивно.м счетчике 1 1 хранится код 00...О, то на выходной шине 2 дец1ифратора 16 - высокий уровень, разрешающий запись в ячейку памяти, к которой подключен выход 2 дешифратора 16. При появлении сигнала на третьем выходе блока 9 слово с входов 7 через ко.мму- таторы 23 записывается в ячейки 24 памяти. Сигнал с третьего вы.хода блока 9 поступает на вход -1 реверсивного счетчика 11. Из его содержимого вычитается единица, а нижняя граница занятой зоны ЗУ с.меща- ется на одну ячейку вниз. Таким образом, слово в ЗУ записываются по порядку поступления на очередное свободное место памяти, указываемое высоким уровнем одного из выходов дещр |фратора 16. В реверсивном счетчике 11 накапливается значение, указываюц 1,ее на номер первой свободной ячейки за нижней границей занятой зоны ЗУ.

Происходит сравнение содержимого реверсивных счетчиков 10 и 11 в блоке 12 сравнения. Далее работа устройства в этом ре- жиме происходит аналогично фазе режима «Запись в вершину.

Чтение из основания списка. При подаче на входы 2 и 4 устройства сигналов «Чтение и «Основание (или сигнала «Чтение

0 на вход 2, если режим «Основание уже установлен) на четвертом выходе блока 9 появляется сигнал, который поступает на входы коммутаторов 19, 22-25 считывания всех разрядов. Если, например, в реверсивном счетчике 11 хранится код 11...I, то

5 на шине 2 дешифратора 15 - высокий уровень, разрешающий чтение из ячейки памяти, к которой подсоединен выход ден1ифра- тора 15. При появлении сигнала на четвертом выходе блока 9 информация из ячеек

Q 24 памяти через коммутаторы 25 считывания поступает на выход 8. Сигнал с четвертого выхода блока 9 поступает на вход +1 реверсивного счетчика 11, к его содержимому добавляется единица, а нижняя граница занятой зоны ЗУ смещается на одну ячейку

5 вверх.

При подаче следующего сигнала «Чтение на вход 2 устройства информация из ячеек 18 памяти через коммутаторы 19 считывания поступает на выход 8, так как по значению 00...О реверсивного счетчика 11 высо0 кий уровень разрешения присутствует на первом выходе дешифратора 15. Далее зна- чение реверсивного счетчика 11 увеличивается на единицу и т.д.

Происходит сравнение содержимого реверсивных счетчиков 10 и 1 1 в блоке 12 срав5 нения. Далее работа устройства в этом режиме происходит аналогично подобной фазе режима «Чтение из верн1ипы.

40

Формула изобретения

0

1. Стековое запоминающее устройство, содержащее группы элементов памяти, входы которых подключены к выходам коммутаторов записи соответствующих групп, вы- 5 ходы элементов памяти групп подключены к информационным входам коммутаторов считывания соответствующих групп, выходы которых являются информационны.ми вьгхода- .ми устройства, инфор.мационные входы коммутаторов записи групп являются информационными входами устройства, первые управляющие входы коммутаторов считывания каждой группы соединены и подключены к соответствующим выхода.м первого дешифратора, первые управляющие входы коммутаторов записи каждой группы объединены и подключены к соответствующим выходам второго деплифратора, входы первого и второго дешифраторов подключены к выходу первого реверсивного счетчика, отличающеея

5

тем, что, с целью расширения области применения устройства за счет записи и считывания данных в начало массива, оно содержит третий и четвертый дешифраторы, второй реверсивный счетчик, блок сравнения и блок управления, первый и второй входы которого являются соответственно входами записи и считывания устройства, третий и четвертый входы блока управления являются соответственно входами обраш,ения в вершину и основание массива устройства, пятый вход блока управления является входом сброса устройства, шестой вход блока управления подключен к выходу блока сравнения, первый вход которого подключен к выходу первого реверсивного счетчика, второй вход блока сравнения подключен к выходу второго реверсивного счетчика и входам третьего и четвертого дешифраторов, вторые управляющие входы коммутаторов считывания каждой группы объединены и подключены к соответствующим выходам третьего дешифратора, вторые управляющие входы коммутаторов записи каждой группы объединены и подключены к соответствующим выходам четвертого дешифратора, трепъи управляющие входы коммутаторов записи каждой группы объ- единены и подключены к первому выходу блока управления и суммирующему входу первого реверсивного счетчика, вычитающий вход которого подключен к второму выходу блока управления и третьим управляющим входам коммутаторов считывания групп, четвертые управляющие входы коммутаторов записи групп подключены к третьему выходу блока управления и вычитающему входу второго реверсивного счетчика, суммирующий вход которого подключен к четвертому выходу блока управления и четвер- тым управляющим входам коммутаторов считывания групп, третьи входы первого и второго реверсивных счетчиков являются входом начальной установки устройства. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит элементы И, элементы И-НЕ, элементы ИЛИ, элементы задержки и триггеры, причем первый вход первого элемента И является первым входом блока у 1равления и подключен к входу первого элемента задержки и первому вхо- ду первого элемента И--НЕ, второй вход которого является вторым входом блока управления и подключен к второму входу первого элемента И и входу второго элемента задержки, выход которого подключен к перво

5

0

5 0 5 5

0

му входу второго элемента И, второй вход которого подключен к выходу первого элемента И-НЕ и первому входу третьего элемента И, второй вход которого подключен к выходу первого элемента задержки, третий вход третьего элемента И подключен к выходу первого элемента И и третьему входу второго элемента И, выход которого подключен к первым входам четвертого и пятого элементов И и входу третьего элемента задержки, выход которого подключен к входу синхронизации первого триггера и первому входу первого элемента ИЛИ, второй вход которого является пятым входом блока управления и подключен к первому входу второго элемента ИЛИ, выход которого подключен к R-входу первого триггера, S-вход которого является шестым входом блока управления и подключен к S-входу второго триггера, R-вход которого подключен к выходу пер вого элемента ИЛИ, выход третьего элемента И подключен к первым входам шестого и седьмого элементов И и входу четвертого элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ и входу синхронизации второго триггера, выход которого подключен к вторым входам шестого и седьмого элементов И, третьи входы и выход первого триггера подключены к вторым входам четвертого и пятого элементов И, третьи входы четвертого и шестого элементов И подключены к прямому выходу третьего триггера, инверсный выход которого подключен к третьим входам пятого и седьмого элементов И, R- и S-входы третьего триггера подключены к выходам соответственно восьмого и девятого элементов И, первые входы которых подключены к выходу второго элемента И-НЕ, первый вход которого является четвертым входом блока управления и подключен к первому входу третьего элемента ИЛИ к входу пятого элемента задержки, выход которого подключен к второму входу восьмого элемента И, третий вход которого подключен к второму входу девятого элемента И и выходу третьего элемента ИЛИ, второй вход которого является третьим входом блока управления и подключен к второму входу второго элемента И-НЕ и входу шестого элемента задержки, выход которого подключен к третьему входу девятого элемента И, выходы шестого, четвертого, седьмого и пятого элементов И являются соответственно первым, вторым, третьим и четвертым выходами блока управления.

2В

27

7о28

Выход

фи2.2

Второй Sbuod

foJ0.

Третий

Вылод

Четвертый

Вылод

0т Сх срЛ-

5оt

38

/1,ш записи 1U Лш счил7ь/ёоWfl /J

си лу к bfeo

свободная зона ЗУ

HanpaSjjeHue ния нижней границы занятой зоны ЗУ при вь/полнении операции уалиси 6 основание сл(/с- на

Нопраёление смещение eepJCHsu границы занятой зонд ЗУ при S6/noji- HGHL/L/ олерации зап1/си 6 Вершину

АШ С1 ить/3ания 15

АШ записи fff

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство управления сообщениями | 1982 |

|

SU1062704A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для моделирования графов | 1983 |

|

SU1126967A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1991 |

|

SU1789986A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации стековых запоминающих устройств. Целью изобретения является расширение области применения устройства за счет записи и считывания данных в начало массива. Устройство содержит блок 9 управления, реверсивные счетчики 10 и 11,блок 12 сравнения, дешифраторы 13-16, коммутаторы 17, 20, 23 записи, коммутаторы 19, 22, 25 считывания, группы 18, 21, 24 элементов памяти. Использование в данном устройстве блока управления с дополнительными шинами записи и считывания, коммутаторов записи и считывания в каждом разряде, второго реверсивного счетчика, блока сравнения, вторых дешифраторов записи и считывания позволяет осуществлять режимы записи и считывания информации как в вершину, так и в основание списка. 1 з.п - ф-лы, 4 ил. i (Л СА: о 4 О оо

фигЛ

| Л\АГАЗИННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU429467A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство параллельного типа | 1978 |

|

SU752484A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-01—Подача