11305686

Изобретение относится к вычислительной технике и может быть исполь- зопано для обнаружения ошибок при передаче информации в параллельном двоичном коде.

Целью изобретения является повышение быстродействия.

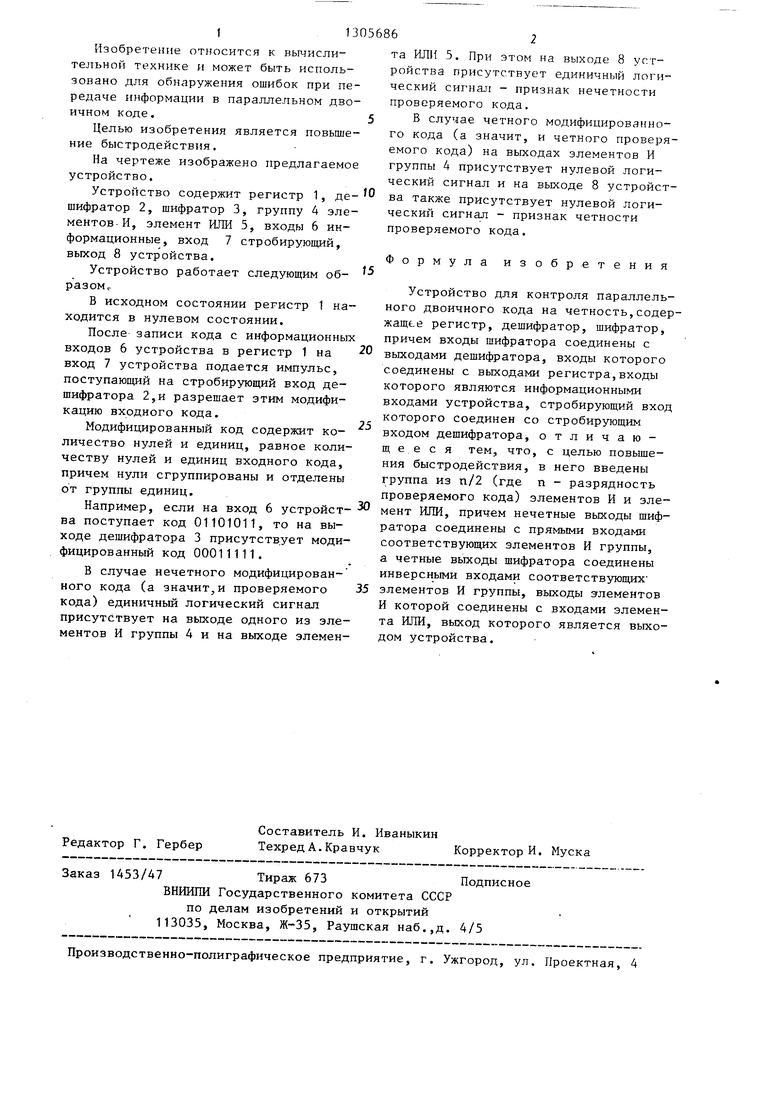

На чертеже изображено предлагаемое устройство.

та ИЛИ 5. При этом на ройства присутствует е ческий сигнал - призна проверяемого кода.

В случае четного мо го кода (а значит, и ч емого кода) на выходах группы 4 присутствует ческий сигнал и на вых

Устройство содержит регистр 1, да- О ва также присутствует

шифратор 2, шифратор 3, группу 4 элементов- И, элемент ИЛИ 5, входы 6 информационные, вход 7 стробирующий, выход 8 устройства.

Устройство работает следующим об- разоМр

В исходном состоянии регистр 1 находится в нулевом состоянии.

После записи кода с информационных

входов 6 устройства в регистр 1 на вход 7 устройства подается импульс, поступаюпщй на стробирующий вход дешифратора 2,и разрешает этим модификацию входного кода.

Модифицированный код содержит количество нулей и единиц, равное количеству нулей и единиц входного кода, причем нули сгруппированы и отделены от группы единиц.

20

25

Устройство для контроля параллельного двоичного кода на четность,содержащее регистр, дешифратор, шифратор, причем входы шифратора соединены с выходами дешифратора, входы которого соединены с выходами регистра,входы которого являются информационными входами устройства, стробирующий вход которого соединен со стробирующим входом дешифратора, отличающееся тем, что, с целью повышения быстродействия, в него введены группа из п/2 (где п - разрядность проверяемого кода) элементов И и элеНапример, если на вход 6 устройст- мент ИЛИ, причем нечетные выходы шифва поступает код 01101011, то на выходе дешифратора 3 присутствует модифицированный код 00011111.

В случае нечетного модифицирован- кого кода (а значит,и проверяемого кода) единичный логический сигнал присутствует на выходе одного из элементов И группы 4 и на выходе элеменРедактор Г. Гербер Заказ 1453/Д7

Составитель И. Иваныкин

Техред А. Кравчук Корректор И. Муска

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

та ИЛИ 5. При этом на вькоце 8 устройства присутствует единичный логический сигнал - признак нечетности проверяемого кода.

В случае четного модифидированно- го кода (а значит, и четного проверяемого кода) на выходах элементов И группы 4 присутствует нулевой логический сигнал и на выходе 8 устройства также присутствует

нулевой логи

0

5

ческии сигнал - признак четности проверяемого кода.

Формула изобретения

Устройство для контроля параллельного двоичного кода на четность,содержащее регистр, дешифратор, шифратор, причем входы шифратора соединены с выходами дешифратора, входы которого соединены с выходами регистра,входы которого являются информационными входами устройства, стробирующий вход которого соединен со стробирующим входом дешифратора, отличающееся тем, что, с целью повышения быстродействия, в него введены группа из п/2 (где п - разрядность проверяемого кода) элементов И и элератора соединены с прямыми входами соответствующих элементов И группы, а четные выходы шифратора соединены инверсными входами соответствующих элементов И группы, выходы элементов И которой соединены с входами элемента ИЛИ, выход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU997038A1 |

| Устройство для формирования контрольного кода по четности | 1980 |

|

SU934477A1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для контроля последовательного двоичного кода | 1989 |

|

SU1644146A1 |

| Устройство для вычитания по модулю | 1989 |

|

SU1689949A1 |

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

Изобретение относится к вычислительной технике и может быть использовано для обнаружения ошибок при передаче информации в параллельном двоичном коде. Цель изобретения - повышение быстродействия. Устройство содержит регистр 1, дешифратор 2,шифратор 3, группу 4 элементов И, элемент ИЛИ 5, входы 6 информационные, вход 7 стробирующий, выход 8 устройства. Совокупность последовательно соединенных регистра 1, дешифратора 2 и шифратора 3 представляет собой модификатор кода, преобразующий входной код в код с разделенными группами нулей и единиц. В случае любого нечетного модифицированного кода (а значит и проверяемого кода) на выходе 8 устройства присутствует единичный логический сигнал. Цель достигается за счет введения группы элементов И, элемента ИЛИ и соответствующих связей. 1 ил. с (Л / 8 ос о СП 05 ОО 05

| Устройство для определения четностииНфОРМАции | 1979 |

|

SU849215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1984-12-17—Подача