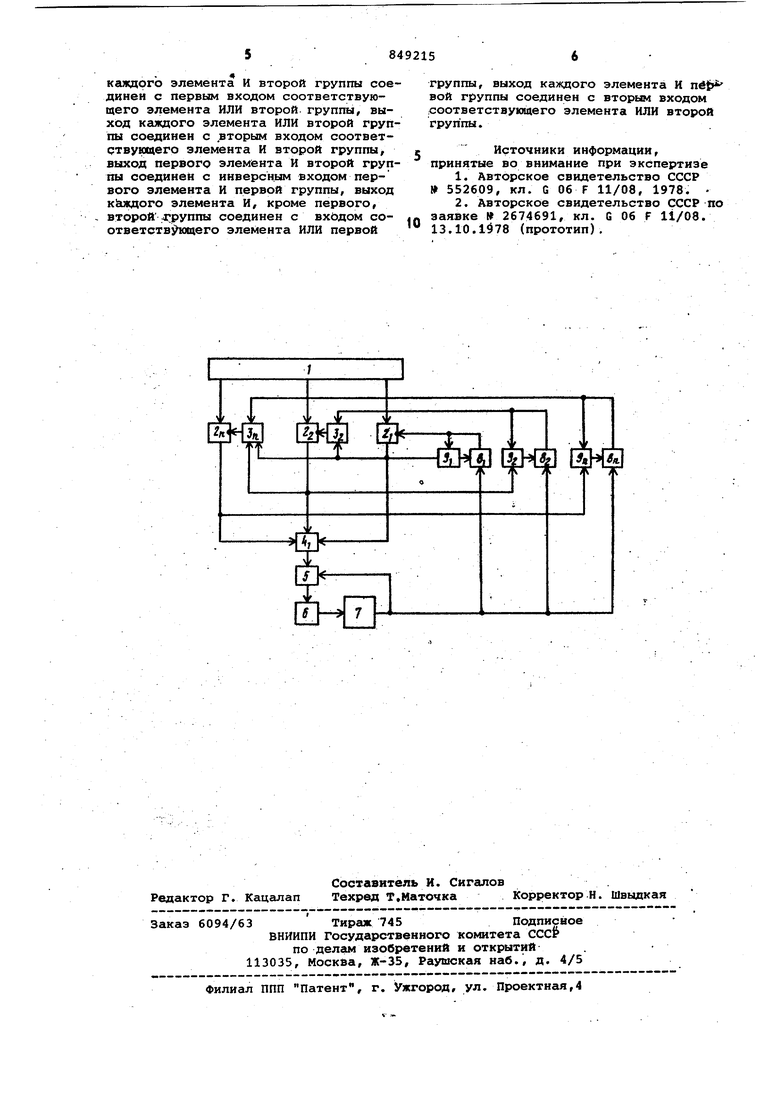

(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧЕТНОСТИ Изобретение относится к вычислительной технике и может быть использовано для проверки на четность или определения в декодирующих устройствах веса кодовых комбинаций корректирующего кода, принимаемых в парешлельном коде. Известны устройства для определения четкости информации, содержащие регистр, элементы И, элемент ИЛИ и триггер со счетным входом til. Недостатком этих устройств .является сравнительно низкое быстродейст вие, особенно при больших длинах ре гистра п. Нс1Иболее близким к изобретению является устройство для определения четности информации, содержащее регистр с выходами разрядов, соединен ных с первой группой элементов И, к инверсным входа которых присоеди нены соответс1вукхаие элементы ИЛИ первой группы, при«1ем выход кгикдого элемента И первой г)уппы соединен с соответствующими входгили всех элеме тов ИЛИ первой группы последуюир1Х разрядов, а также через элемент ИЛИ с счетным входом триггера , . Однако информация, заносимая в регистр, при проверке на четность ИНФОРМАЦИИ стирается, что не позволяет производить при необходимости ее повторную проверку. Поэтому в тех случаях,когда возникает задача сохранения информации в регистре, использование известного устройства затруднено. Цель изобретения - расширение функциональных возможностей за счет обеспечения многократного контроля информации. Поставленная цель достигается тем, что в устройство, содержащее информационный регистр, первые группы элементов И и ИЛИ, элемент ИЛИ и триггер, причем первые выходы каждого из п разрядов информационного регистра соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены с соответствующими входами элемента ИЛИ, выход каждого К-го элемента И первой группы К 1,п соединен с соответствующим входом всех элементов ИЛИ первой группы от К до (n-l)-ro элемента j выход каждого элемента ИЛИ первой группы соединен с инверсным входом соответствующего элемента И первой группы, введены вторые групры элементов И и ИЛИ, формирователь коммутационных сигналов и ялемент и. причем выход элемента ИЛИ соединен с первымВХОДОМ элемента И, выход которого соединен со счетным входом триггера, выход триггера соединен со входом формирователя коммутационных сигналов, ь.ыход которого соединен с вторым входом элемента Ни первыми {входами элементов И второй группы, . выход каждого элемента И второй груп пы соединен с первым входом соответствующего элемента ИЛИ второй группы вызсод каждого элемента ИЛИ второй группы соединен со вторым входом соответствующего элемента И второй группы, выход первого элемента И вто рой группы соединен с инверсным входом первого элемента И первой группы, вход каждого элемента И, кроме первого, второй группы соединен с входом соответствующего элемента ИЛИ первой группы, выход каждого элемента И первой группы соединен с вторым входом соответствующего элемента ИЛИ второй группы. На чертеже представлена структурная схема устройства. Устройство содержит информационный регистр 1, выходы разрядов которого соединены с первой группой элементов И, к входам которых присоединены соответствующие элементы 3.J-3 о-1 ИЛИ первой группы, элемент 4 ИЛИ, элемент. 5 И триггер 6, формирователь 7 коммутационных сигналов, вторая группа элементов И , элементы ИЛИ второй группы Устройство работает следующим образом. Входная двоичная информация заносится в п-разрядный информационный регистр 1 в последовательном или параллельном коде. Пусковым сигналом, подаваемым на вход установки триггера 6 в нулевое состояние, формирователь 7 и входы первой группы элементов И устройство переводится в рабочий ре жим. Если в первом разряде регистра записана 1, сигнал с выхода элеме та 2 И запрещает прохождение сигна лов через элементы 2,-2 И более старших разрядов, а через элемент 4 ИЛИ элемент 5 И фиксируется триггером б со счетным входом. При переключении триггера 6 формирователь 7 образует сигнал комбинации, который поступает через соответствующий элемент 5 И второй группы на запоет прохождения сигнала через элемент 2 И, а через элемент по держивает включённым элемент , В результате, через элемент 3 ИЛ снимается запрет на последующем эле менте 2 И и, следовательно, обеспечивается возможность прохождения си нал а о следующего разряда,где запи сана 1.При этом Сигналы переключе ния триггера 6 поддерживают включен ным формирователь 7,длительность ко мутирующих сигналов которого должна несколько превышать время переключения триггера б и чзадержку прохождения сигналов через элементы 8, 3, 12, 4 и 5. . В дальнейшем работа устройства осуществляется аналогичным образом. Момент времени окончания работы устройства определяется .по прекращению переключения триггера б. Тогда формирователь 7 снимает коммутирующий сигнал на элементы 8 И, прекращая действие запрета на элементах,2 И, а также с помощью элемента 5 И отключает счетный вход триггера 6, подготавливая устройство к новому . циклу работы. Поэтому для определения окончания счета не требуется подключения второго элемента ИЛИ с вторым триггером или введении дополнительного разряда в регистр 1. Для определения веса кодовых; комбинаций в корректирующем коде достаточно вместо триггера б включить двоичный счетчик. Изобретение обеспечивает проверку информации на четность без стирания информации в регистре, позволяя осуществлять при необходимости ее проверку многократно, что расширяет функциональные возможности устройства. Формула изобретения Устройство для определения-четности информации, содержащее информационный регистр, первые группы элементов И и ИЛИ, элемент ИЛИ и триггер, причем первые выходы каждого из п разрядов информационного регистра соединены с первыми входами соответствующих элементов И первой . группы, выходы котой|13 ;. соединены с соответствующими входами элемента ИЛИ, выход каждого, К-го элемента И первой группы К 1,п соединен с соответствующим входом всех элементов ИЛИ первой группы от К-го до (n-l)-ro элемента, выход каждого эле-, мента ИЛИ первой группы соединен с инверсным входом соответствукедего элемента И первой группы,о т л ичающееся тем, что,с целью расширения функциональных возможностей за счет обеспечения многократного контроля информации, содержит вторую группу элементов И и ИЛИ, формирователь коммутационных сигналов и элемент И, причем выход,элемента ИЛИ соединен с первым входом элемента И, выход которого соединен со счетным входом триггера, выход тригге а соединен со входом формирователя коммутационных сигналов, выход которого соединен с вторым входом элемента И и первыми входами элементов И второй группы, выход

каждого элемента И второй группы соединен с первым входом соответствующего элемента ИЛИ второй группы, выход кгикдого элемента ИЛИ второй группы соединен с вторым входом соответствующего элемента И второй группы, выход первого элемента И второй группы соединен с инверсным входом первого элемента И первой группы, выход Ксокдого элемента И, кроме первого, второй4:руппы соединен с вхьдом соответств; ю|цего элемента ИЛИ первой

группы, выход каждого элемента И net вой группы соединен с вторым входом соответствующего элемента ИЛИ второй группы.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР 552609, кл. G Об F 11/08, 1978.

2.Авторское свидетельство СССР по заявке № 2674691, кл. G 06 F 11/08. 13.10.1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вторичные кварцевые часы для синхронизации генератора псевдослучайной последовательности | 1991 |

|

SU1835532A1 |

| Устройство для определения четности информации | 1978 |

|

SU767766A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для разбраковки микросхем | 1982 |

|

SU1103288A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для определения количества единиц в двоичном числе | 1982 |

|

SU1084797A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для обнаружения ошибок при передаче кодов | 1989 |

|

SU1615723A2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

Авторы

Даты

1981-07-23—Публикация

1979-10-29—Подача