Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных цифровых вычислительных ма- шин.

Цель изобретения - повьшение быстродействия устройства путем формирования результата начиная со старших разрядов,

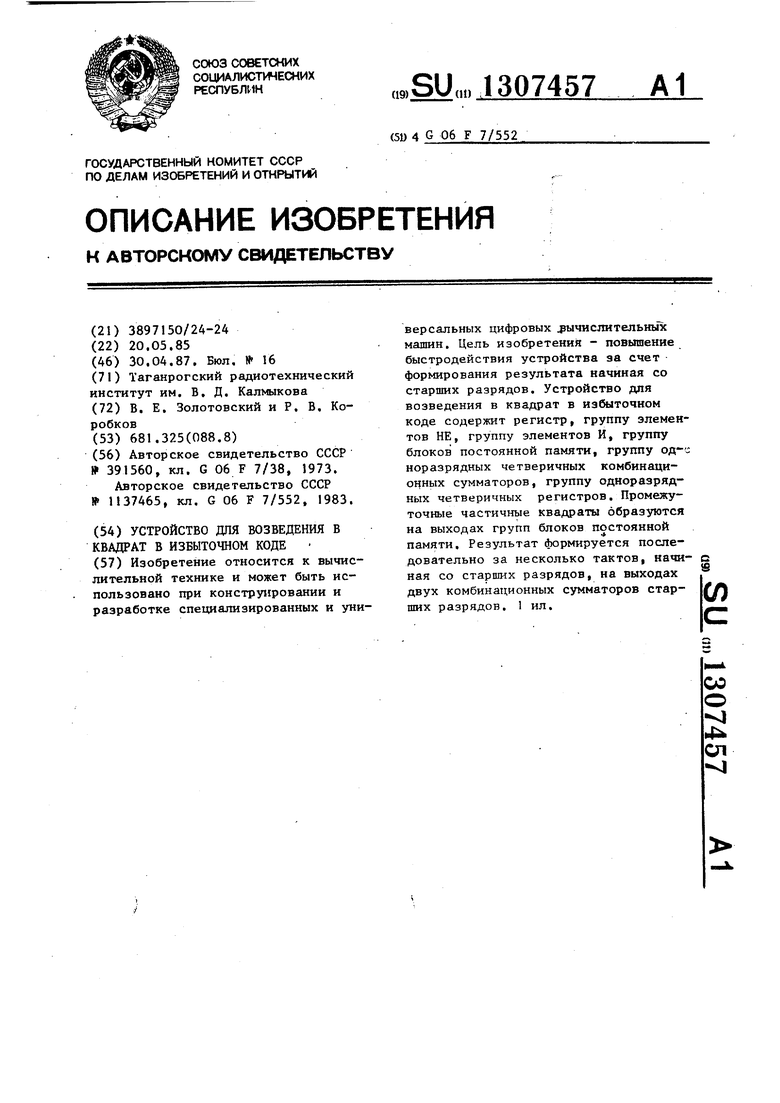

На чертеже приведена схема устройства для пяти четверичных разрядов.

Устройство содержит регистр 1, информационный вход 2, входы 3 и 4 записи и сдвига, с первого по п-й () элементы НЕ 5 - 9 группы, с первого по п-й элементы И 10 - 14, (п+) элемент НЕ 15 группы, (п-И) элемент И 16 групць, с первого по (п+1) блоки 17 - 22 постоянной па- мяти (БПП), нулевой 23 и единичный 24 входы, с первого по п-й одноразрядные четверичные комбинационные сумматоры 25 - 29, с первого по п-й одноразрядные четверичные регистры 30 - 34, вход 35 сдвига оегистров и информационные выходы 36.

Регистр 1 предназначен дпя приема аргумента X в избыточном коде. Аргумент X в параллельном коде подается на входы 2 устройства. Вход 3 устройства соединен с входом управления записью в регистр 1. Вход 4 устройства соединен с входами управления сдвигом регистра 1. Сдвиг производит ся на одну четверичную цифру. Выход старшего двоичного разряда каждого четверичного разряда через элементы НЕ 5 - 9 соединен с первым входом элементов И 10 - 14 соответственно. Мпадший двоичный разряд старшего четверичного разряда через элемент НЕ 15 соединен с входом элемента И 16, Вторые входы элементов И }0 - 14 соединены с выходами вторых дно- ичных разрядов соответствующих четверичных разрядов регистра 1, Второй и третий входы элемента И 10 соединены с выходами второго и первого двоичных разрядов старшего четверичного р-азряда регистра 1 , Выходы регистра 1 и элементов И 10 - 14 и 16 соединены с входами БПП 17 - 22, имеющими 9 адресных входов (дпя Б1ш 20 - входы 20,, 202, 20i, 20, 20у, 20, 20,, 208, Oj) и b выходов данных (для БПП - выходы 20,й, 20, 20„, , ). БПП работают следукнцим образом.

Если обозначить код,поступаюпдай на входы блока 20 (входы 20, 20 и 20д) четверичной цифрой Х-, код, поступающий на входы 20, 20j, и 20, - двоичными цифрами й,, , O5J; код, поступающий на входы 20, 208 четверичной цифрой If; ( 1 для БПП 20), то на выходах БПП формируется двуразрядное четверичное число Zj по следующему правилу:

Z,. Х.(2«,-Й2У 31-) Г%-. где а, 0,1; «2 0,1; tn 0,1; Х| -2„ -1, О, +1, +2, +3 кодируется 110, 111, 000, 001, 010, 011 соответственно; j -2 -1, О, +1, +2 кодируется аналогично,

Младший разряд числа Z- формируется на выходах 20, 20,, как - четверичная цифра S, , старший - на выходах , 20, четверичная цифра «cj. Входы 17, 17., 17 БПП 17 и 22j 22,22, 22, 22 j БПП 22 соединены с входом 23, на который постоянно поступает сигнал О. Вход 17j БПП 17 соединен с входом 24, на который постоянно поступает сигнал 1. Поэтому БПП 22 реализует функцию:

Z5

2 а

if

а БШ1 17

Zo 2 + Pi + m,.

где е(с, Ро Р могут принимать значения О или 1, БПП 18 имеет такое же число входов и выходов. Если сохранить обозначение кодов, поступающих на его входы, прежним, то БПП 18 реализует функцию:

.(-«2j+«3j j м

Шлходы старших БПП соединены с входаьш параллельного комбинахщонно- го четверичного сумматора, построенного на одноразрядных четверичных сумматорах 25 - 29, Входы первого слагаемого сумматоров 26 - 29 соединены с выходами БПП 17 - 20 соответственно. Входы первого слагаемого сумматора 25 и входы переноса сумматора 29 соединены с входом устройства 23, Входы переноса сумматоров 25 - 28 .соединены с выходами переноса сумматоров 26 - 29 соответственно Входы второго слагаемого сумматоров 25 - 29 соединены с выходами одноразрядных четверичных регистров 30 - 34. Входы регистров 33 и 34 соединены с выходами БПП 21 и 22 соответственно. Входы регистров 30 - 32 соединены с выходами сумматоров 27 -

29соответственно. Вход 35 устройства управляет входом управления записью в регистры 30 - 34. Одноразрядный четверичный регистр представляет собой обычный трехразрядный двоичный регистр. Выходы сумматоров 25 и 26 являются выходами устройства 36.

Устройство работает следующим образом.

В исходном состоянии регистры I,

30- 34 обнулены. Перед началом операции на вход 2 подается число, возводимое к вадрат X, которое по сигналу записи, поступающему на вход 3, записывается в регистр 1 старшими разрядами слева. С помощью логических элементов НЕ 5- 15И 0- 14

и 16 и БПП 17-22 формируется 1-й частичный квадрат, который непосредственно (из БПП 21 и 22) или через БПП 18 - 20 и сумматоры 25 - 29 поступает на регистры 30 - 34 со сдвигом на два разряда влево. По затухании переходных процессов на входы 4 и 35 поступает синхросигнал, по которому происходит сдвиг числа в регистре 1 и запись первого частичного квадрата в регистры 30 - 34. Старший разряд величины считывается с выхода 36. На этом 1-й цикл 35 ДУ первого элементаUгруппы и через возведения в квадрат завершается. В (п+1 )-й элемент НЕ группы к первому вхо логических элементах и БПП формирует- ДУ (п+1)-го элемента U группы, выход ся второй частичный квадрат, который первого элемента И группы соединен с в сумматорах 25 - 29 складывается со четвертым адресным входом первого сдвинутым первым. По завершении сум- 40 блока постоянной памяти, а выходы

мирования по сигналу, поступающему на входы 4,35, вновь сдвигается содержимое регистра 1 и записывается со сдвигом сумма первых частичных квадратов в регистры 30 - 34. С выходов 36 считывается пара разрядов величины у.

Формула изобретени

50 норазрядного четверичного комбинационного сумматора и входы переноса п-го одноразрядного четверичного комбинационного сумматора подключены к входу логического нуля устройства

Устройство для возведения в квадрат в избыточном коде, содержащее регистр и группу элементов И, причем информационные входы, входы записи и сдвига устройства подключены к одно- 55 третий адресный вход первого блока именным входам регистра, о т л и - постоянной памяти соединен с входом чающееся тем, что, с целью логической единицы устройства, с повышения быстродействия устройства седьмого по девятый адресные входы

путем формирования результата начиная со старших разрядов, в него введены группа элементов НЕ, группа из (п+1) блоков постоянной памяти, группа одноразрядных четверичных комбина- ционньк сумматоров и группа одноразрядных четверичных регистров, причем выходы старшего четверичного разряда регистра подключены к первому, второму и третьему адресным входам с второго по (п+)-й блоков постоянной памяти, выходы младших двоичш 1х разрядов с первого по п-й четверичных разрядов регистра подключены к четвертым адресным входам с второго по (п+)-й блоков постоянной памяти, соответственно выходы старших двоичных разрядов с второго по п-й четверичных разрядов регистра подключены к пятым адресным входам с второго по п-й блоков постоянной памяти соответственно, выходы старших двоичных разрядов с первого по п-й четверичных разрядов регистра через соответствующие элементы НЕ группы подключены к первым входам с первого по п-й элементов U группы соответственно, выходы средних двоичных разрядов с первого по п-й четверичных разрядов регистра подкпючень к вторым входам с первого по п-й элементов U группы соответственно, выходмладдпего двоичного разряда старшего четверичного разряда регистра подключен к третьему второго по п-й элементов И группы соединены с шестыми адресными входаи с второго по (п+1)-й блоков постоянной памяти соответственно,

первый, второй, пятый адресные входы ервого блока постоянной памяти, с пятого по девятый адресные входы (п+1)-го блока постоянной памяти, входы первого слагаемого первого одноразрядного четверичного комбинационного сумматора и входы переноса п-го одноразрядного четверичного комбинационного сумматора подключены к входу логического нуля устройства,

третий адресный вход первого блока постоянной памяти соединен с входом логической единицы устройства, с седьмого по девятый адресные входы

i-го блока постоянной памяти (i,n) подключены к первому по третий выходам (i+l)-ro блока постоянной памяти, с четвертого по шестой выходы с первого по (п-1)-й блоков постоянной памяти подключены к входам с первого по третий разрядов первого слагаемого с второго по п-й одноразрядных четверичных комбинационных сумматоров группы соответственно, с четвертого по шестой выходы п-го и(п+1)-го блоков постоянной памяти подключены к информационньм входам ()-го и п-го одноразрядных четверичных регистров группы, входы второго слагав мого с первого по п-й одноразрядных четверичных комбинационных сумматоров группы подключены к соответствующим выходам с первого по п-й одноразрядных четверичных регистров группы., входы переноса i-ro одноразрядного четверичного комбинационного сумма,

fO

20

15

тора группы соединены с соответствующими выходами переноса (i+l)-ro одноразрядного четверичного крмбина- ционного сумматора группы, выходы первого и второго одноразрядных четверичных комбинационных сумматоров пойключены к выходу результата устройства, выходы с третьего по п-й одноразрядных четверичных комбинационных сумматоров подключены к соответствующим информационным входам с первого по (п+2)-й одноразрядных четверичных регистров соответственно, входы сдвига одноразрядных четверичных регистров подключены к входу сдвига регистров устройства, выход среднего двоичного разряда старшего четверичного разряда регистра подключен к второму входу ()-1го элемента И группы, выход которого соединен с шестым адресные входом п ервого блока постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для возведения в квадрат комплексных чисел | 1980 |

|

SU879584A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| Векторное устройство для деления | 1984 |

|

SU1259250A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных цифровых вычислительных машин. Цель изобретения - повышение быстродействия устройства за счет формирования результата начиная со старших разрядов. Устройство для возведения в квадрат в избыточном коде содержит регистр, группу элементов НЕ, группу элементов И, группу блоков постоянной памяти, группу од-с поразрядных четверичных комбинационных сумматоров, группу одноразрядных четверичных регистров. Промежуточные частичнь1е квадраты образуются на выходах групп блоков постоянной памяти. Результат формируется последовательно за несколько тактов, начиная со старших разрядов, на выходах двух комбинационных сумматоров старших разрядов. 1 ил. i (Л С со о 4 СП

i i i i i

Составитель В. Сычев Редактор Л, Пчолинская Техред Л,Олейник Корректор А. Ильин

Заказ 1634/49Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная 4

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ | 0 |

|

SU391560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1137465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-30—Публикация

1985-05-20—Подача