Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специалнзированньгх и универсальных процессоров.

Цель изобретения - сокращение оборудования.

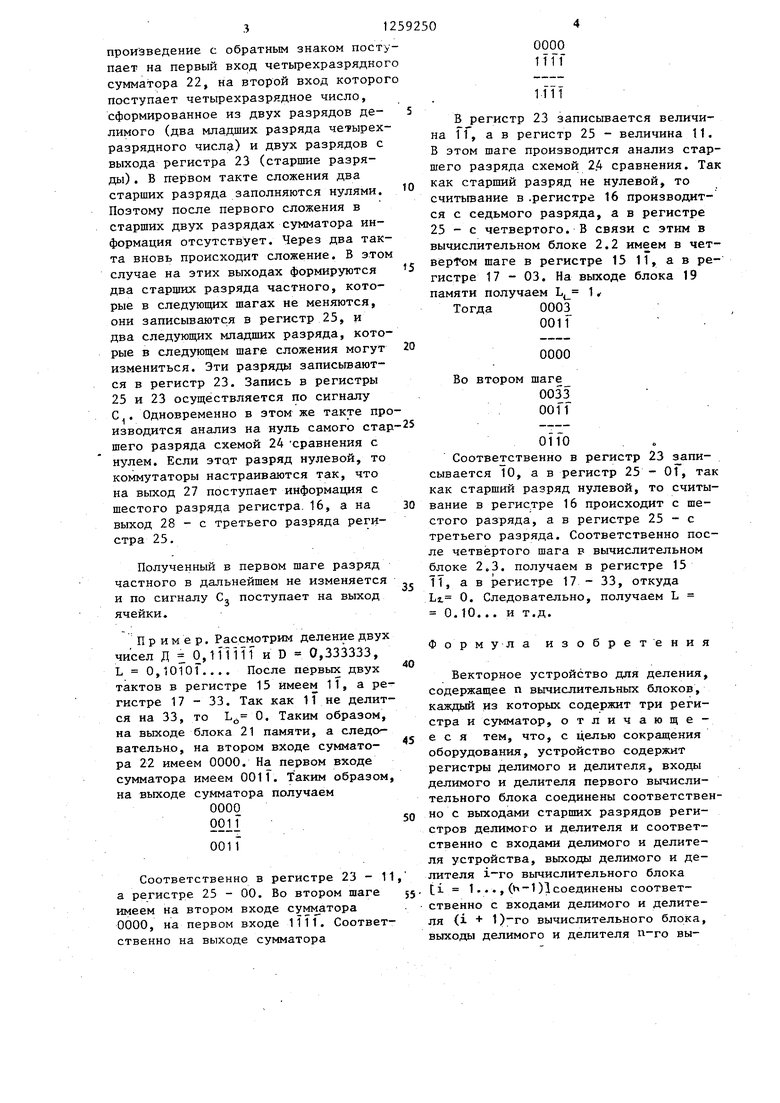

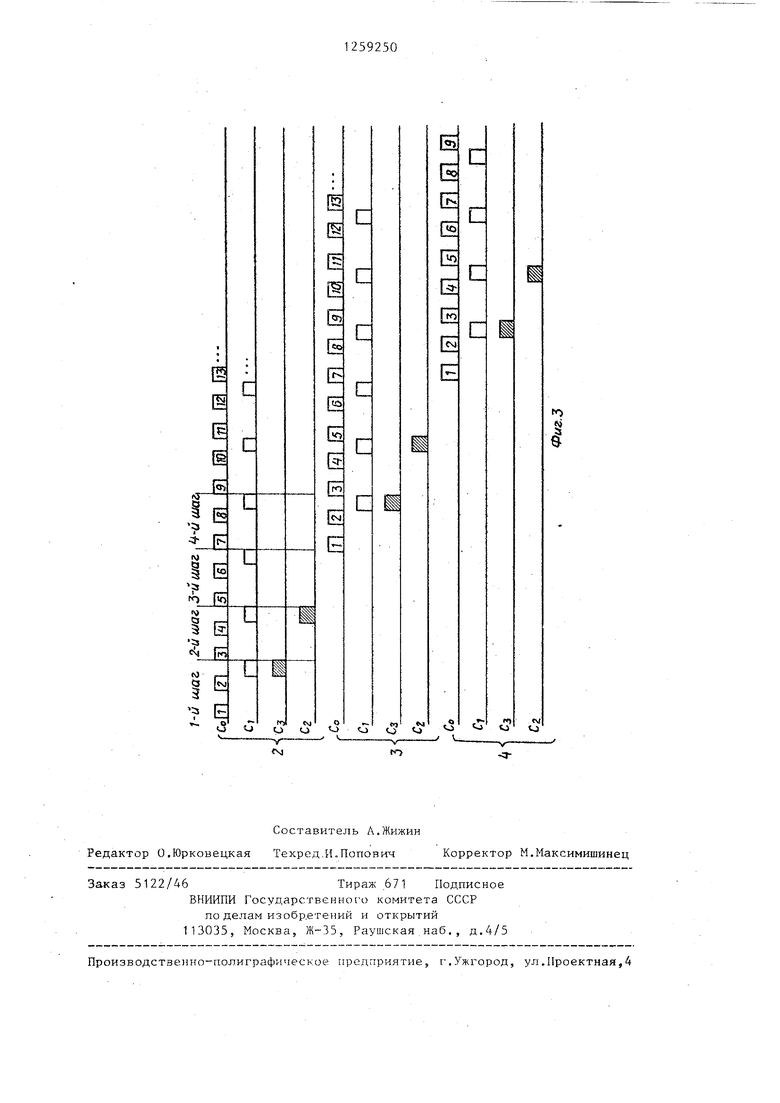

На фиг„1 изображена Структурная схема векторного устройства для деления; на - структурная схема вы- Осокая точность или число вычислитель- числительного блока; на фиг.З - вре-ных блоков меньше чем , например менная диаграмма работы устройства. .Векторное устройство для деления (фиг.1) содержит группу управляющих- входов 1, вычислительный блок 2, груп- 5частного. Для этого делитель и теку- пы управляющих входов 3-5, регистрщий остаток задерживаются в регистрах 6 делимого, входы 7 и & делимого ина ьремя, пока вычислительный блок делителя, управляющий вход 9, регистр2,1, не освободится, и туда вновь

вновь могут быть прогнаны через вектор и получены следующие m разрядов

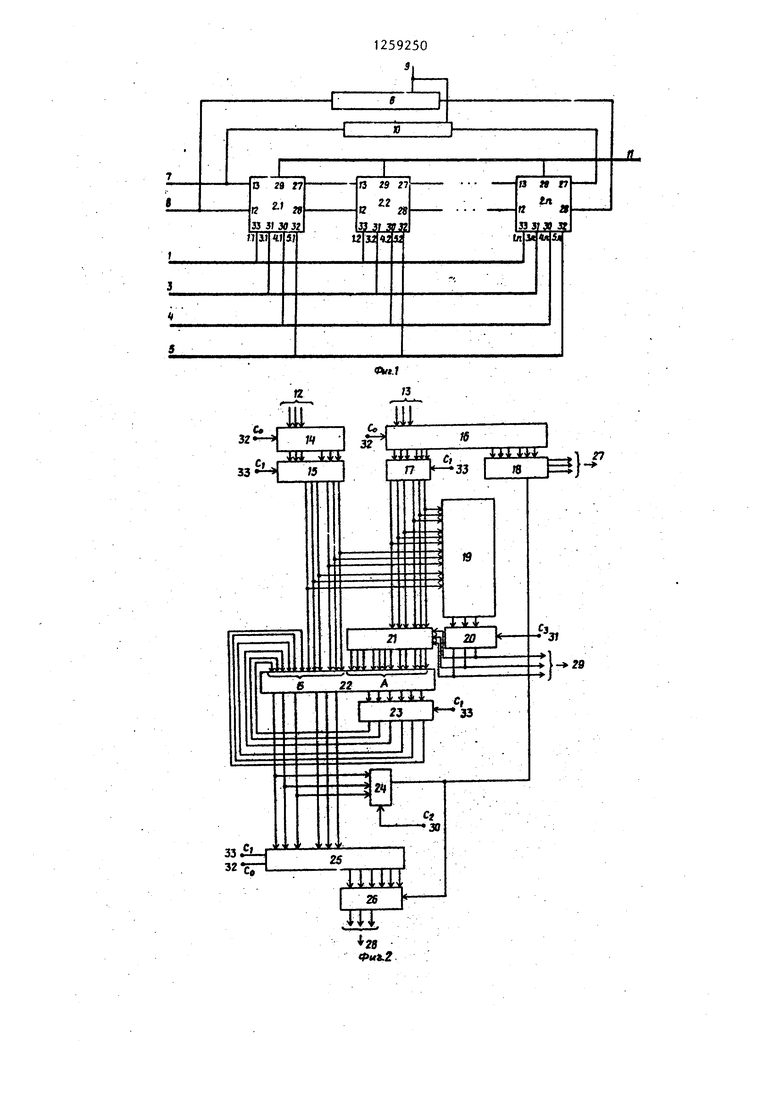

10 делителя и выход 11 устройства« Вычислительный блок (фиг.2) содержит входы 12 и 13 делимого и делителя, регистры 14 - 17, коммутатор 18, блок 19 памяти, регистр 20, блок 21 памяти,, сумматор 22, регистр 23, схему 24 сравнения- с нулем, регистр 25, коммутатор 26, выводы 27 - 29 делителя, делимого и частного и упраляющие вход 30-33.

Устройство работает следующим образом. .

Каждый вычислительный блок используется для формирования разряда частного и соответствующего этому разряду остатка. Делимое и делитель в последовательном четверичном избыточном коде разряд за разрядом, .начина я со старших, поступают на вход устройства. В вычислительном блоке 2.1

определяется старший разряд частного L и определяется первый остаток 0.

О, д - D-L ,

где Д - делимое; D - делитель.

Как только определится старший разряд остатка, он совместно со сташим разрядом делителя поступает в вычислительный блок 2.2 соответственно с выходов 27 и 28 блока 2.1. Одновременно разряд частного с вы- .хода 29 поступает на выход устройства.

Во втором и последуюпщх вычислительных блоках все повторяется. Число вычислительных блоков выбирается таким, чтобы все разряды делимого и делителя умещались в векторе, т.е. когда в последнем вычисли- . тельном блоке обрабатьшается старший разряд делителя и текущего остатка, в первом вычислительном блоке обрабатываются младшие разряды делимого и делителя. Конструкция вычислительного блока такова, что при этом можно получить h/2 четверичных разрядов частного. Если необходима более высокая точность или число вычислитель- ных блоков меньше чем , например частного. Для этого делитель и теку- щий остаток задерживаются в регистрах на ьремя, пока вычислительный блок 2,1, не освободится, и туда вновь

вновь могут быть прогнаны через вектор и получены следующие m разрядов

поступают делитель и текущий остаток.

После получения требуемой точности вычисления прекращаются.

Вычислительный блок работает следующим образом.

На вход 19 делимого поступает делимое (в других случаях остаток), на вход 13 делителя поступает делитель. По сигналам С вначале старший, а затем следующий младший разряд записываются в регистры 14 (делимое)

и 16 (делитель). По сигналу С , поступающему на вход 33, в регистры 15 и 17 переписываются указанные два разряда. При поступлении следующих разрядов в регистр 14 они вытесняют

ранее записанные разряды, а в регистре 16 они последовательно сдвигаются, так как последний является семиразрядным (под разрядом йдесь понимается разряд четверичного избыточного

знакоразрядного кода, содержащего три двоичных разряда: один знаковый и два значащих; кодирование следующее: 3-011, 2 - 010, 1 - 001, О - 000, 1 - 111, 2 - 110. Два разряда

из регистров 15 и 17 поступают на адресные входы блока 19 п амяти, где в зависимости от их соотношения вырабатывается цифра частного. Предполагается, что деление происходит двух

нормализованных чисел (мантисс), Разряд частного с выхода блока 19 памяти через регистр 20, где он фиксируется по сигналу С, с входа 31 поступает на адресные входы блока 21 памяти.

Туда же поступают два текущих разряда делителя. В блоке 21 памяти записана таблица умножения двухразрядньт чисел на одноразрядное. Полученное

произведение с обратным знаком поступает на первый вход четьфехразрядног сумматора 22, на второй вход которог поступает четырехразрядное число, сформированное из двух разрядов делимого (два младших разряда четырехразрядного числа) и двух разрядов с выхода регистра 23 (старшие разряды) . В первом такте сложения два старших разряда заполняются нулями. Поэтому после первого сложения в старших двух разрядах сумматора информация отсутствует. Через два такта вновь происходит сложение. В этом случае на этих выходах формируются два старших разряда частного, которые в следующих шагах не меняются, они записываются в регистр 25, и два следующих младших разряда, которые в следующем шаге сложения могут измениться. Эти разряды записьюают- ся в регистр 23. Запись в регистры 25 и 23 осуществляется по сигналу С . Одновременно в этом же такте производится анализ на нуль самого стар шего разряда схемой 24 -сравнения с нулем. Если этот разряд нулевой, то коммутаторы настраиваются так, что на выход 27 поступает информация с шестого разряда регистра. 16, а на выход 28 - с третьего разряда регистра 25.

Полученный в первом шаге разряд частного в дальнейшем не изменяется

и по сигналу ячейки.

С. поступает на выход

Пример. Рассмотрим деление двух чисел Д О, tilin и D 0,333333, L О,1010Г.... После первых двух тактов в регистре 15 Имеем 11, а регистре 17 - 33. Так как 11 не делится на 33, то L 0. Таким образом, на выходе блока 21 памяти, а следовательно, на втором входе сумматора 22 имеем 0000. На первом входе сумматора имеем 001 Г. Та.ким образом, на выходе сумматора получаем 0000

ogiJ

ООП

Соответственно в регистре 23 - 11, а регистре 25 - 00. Во втором шаге 55 имеем на втором входе сумматора 0000, на первом входе 1111. Соответственно на выходе сумматора

10

IS

25 30

20

5

0

5

0

5

0000 1 Т1 f

lfTl

В регистр 23 записывается величина 11, а в регистр 25 - величина 11. В этом шаге производится анализ старшего разряда схемой 2.4 сравнения. Так как старший разряд не нулевой, то считьшание в .регистре 16 производится с седьмого разряда, а в регистре 25 - с четвертого. В связи с этим в вычислительном блоке 2.2 имеем в четвертом шаге в регистре 15 1, а в регистре 17 - 03. На выходе блока 19 памяти получаем L 1

Тогда 0003 0011

0000

Во втором шаге 0033

00lT

01Го

Соответственно в регистр 23 записывается 10, а в регистр 25 - О Г, так как старший разряд нулевой, то считывание в регистре 16 происходит с шестого разряда, а в регистре 25 - с третьего разряда. Соответственно после четвёртого шага в вычислительном блоке 2.3. получаем в регистре 15

1Т, а в регистре 17 - 33, откуда Li 0. Следовательно, получаем L 0.10... и т.д.

Формула изобретения

Векторное устройство для деления, содержащее п вычислительных блоков, каждый из которых содержит три регистра и сумматор, отличающееся тем, что, с целью сокращения оборудования, устройство содержит регистры делимого и делителя, входы делимого и делителя первого вычислительного блока соединены соответственно с выходами старших разрядов регистров делимого и делителя и соответственно с входами делимого и делителя устройства, выходы делимого и делителя i-ro вычислительного блока ti 1...,(h-1)1 соединены соответственно с входами делимого и делителя (i + 1)-го вычислительного блока, выходы делимого и делителя п-ро вычислительного блока соединены соответственно с информационными входами младших разрядов регистров делимого .и делителя, выходы частного всех вычслительных блоков соединены с выходо устройства, вход управления сдвигом, .вход управления записью делимого и делителя, вход управления выборкой делимого и делителя и вход управления записью частного j-rp вычислительного блока соединены соответственно с j-MH входами управления сдвигом, управления записью делимого и делителя, управления выборкой делимого и делителя, управления записью частного устройства (j t.. .,), причем вычислительный блок содержит дополнительно четвертый, пятый, шестой и седьмой регистры, первьй и второй блоки памяти, два коммутатора и схему сравнения с нулем, причем информационный вход младшего разряда первого регистра подключен к входу делимого вычислительного блока, выход первого регистра соединен с информационным входом второго регистра, выход которого подключен к младшим разрядам первого входа сумматора и к первой группе адресных входов первого блока памяти, вторая группа адресных входов которого соединена с первой группой адресных входов второго блока памяти и с выходом третьего регистра, информационные входы которого соединены с выходами младших разрядов четвертого регистра, информационный вход младшего разряда которого соединен с входом делителя вычислительного блока, выходы старпшх разрядов четвертого регистра соединены с соответствующими информационными входами перво

го коммутатора, выход которого соединен с выходом делителя вычислительного блока, управляющий вход первого коммутатора соединен с управляющим входом второго коммутатора и выходом схемы сравнения с нулем, выходы старших разрядов сумматора соединены соответственно с информационными уходами младших разрядов пятого регистра, выходы старших разрядов которого соединены с соответствующими информационными входами второго коммутатора, выход которого соединен с выходом делимого вычислительного блока, выходы младших разрядов сумматора подключены к информационным входам шестого регистра, выходы которого соединены соответственно с входами старших разрядов первого входа сумматора, второй вход которого соединен с выходом второго блока памяти, вторая группа адресных входов которого соединена с выходом частного вычислительного блока и с выходом седь- мого регистра, информационный вход которого соединен с выходом первого блока памяти, выход старшего разряда сумматора соединен с информационным входом схемы сравнения с нулем, управляющие сдвигом входы первого, четвертого и пятого регистров соединены с входом управления сдвигом вычислительного блока, вход управления писью которого соединен с управляющими входами записи второго, третьего, пятого и шестого регистров, управляющий вход схемы сравнения с нулем соединен с входом управления выборкой делимого и делителя вычислительного блока, вход управления.записью частного которого соединен с управляющим входом седьмого регистра.

Составитель Л.Жижин Редактор О.Юрковецкая Техред,Н.Попович

Заказ 5122/46Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобр.етений и открытий 113035, Москва, Ж-35, Раушская.наб., д,4/5

Производстве}1но-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор М.Максимишннец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1985 |

|

SU1290303A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления чисел | 1987 |

|

SU1465883A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Устройство для вычисления полярных координат | 1984 |

|

SU1183961A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных процессоров. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что в векторное устройство деления, содержащее п вычислительных блоков, каждый из которых содержит три регистра и сумматор с соответствующими связями, дополнительно введены регистры делимого и делителя и каждый вычислительный блок дополнительно содержит четыре регистра, два блока памяти, .два коммутатора и схему сравнения с нулем с соответствующими связями, 3 ил. ,

| Устройство для ускоренного деления | 1971 |

|

SU446058A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1976 |

|

SU705447A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-04—Подача