113

Изобретение относится к вычислительной технике и автоматике и может быть использовано для контроля многовыходных цифровых схем радиоэлектронной аппаратуры.

Цель изобретения - расширение функциональных возможностей путем расширения класса контролируекых цифровых блоков.

На фиг. 1 приведена структурная схема устройства; на фиг. 2, 3 и 4 - структурные cxeN&i того же устройства с различными вариантами блоков коррекции тестовых последовательностей.

Устройство содержит многоканальный сигнатурный анализатор 1, контролируемый цифровой блок 2, узел 3 сравнения, элемент НЕ 4, элемент И 5

счетчик 6, элементы РАВНОЗНАЧНОСТЬ 7, синхровход 8, группу управляющих входов 9 режима коррекции„ вход 10 начальной установки. Элементы 3 7 образуют блок 11 коррекции тестовых последовательностей.

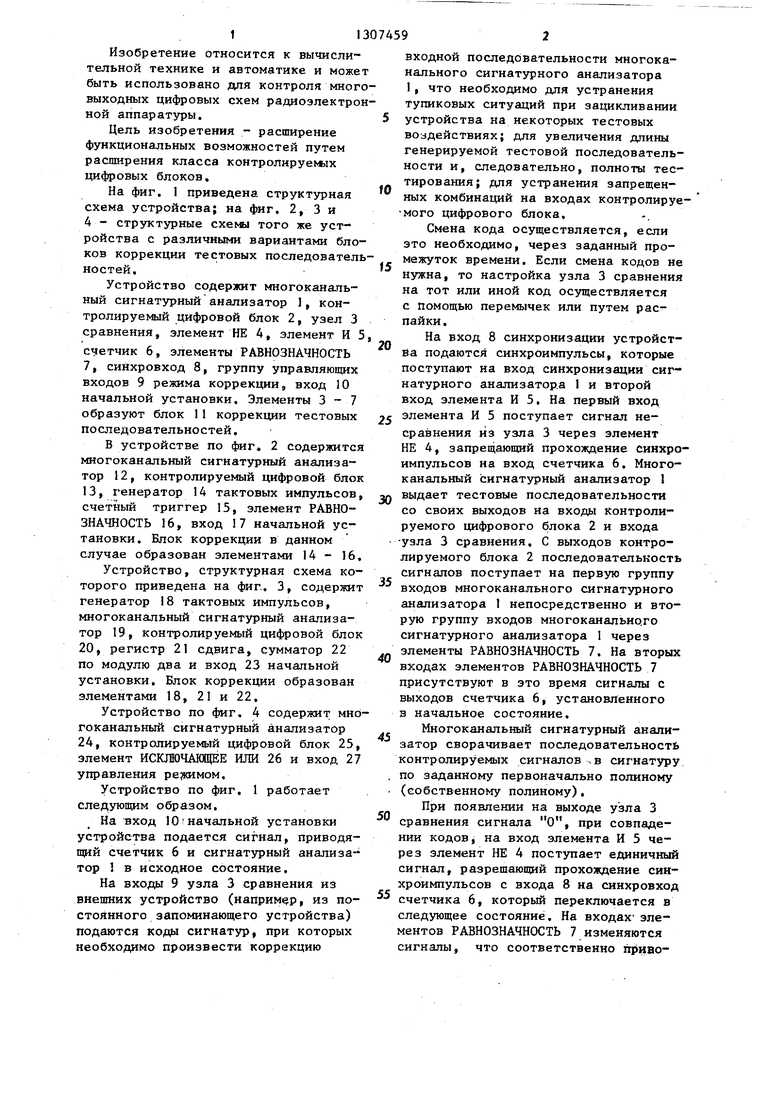

В устройстве по фиг. 2 содержится многоканальный сигнатурный анализатор 12, контролируемый цифровой блок 13, генератор 14 тактовых импульсов, счетный триггер 15, элемент РАВНОЗНАЧНОСТЬ 16, вход 17 начальной установки. Блок коррекции в данном случае образован элементами 14 - 16,

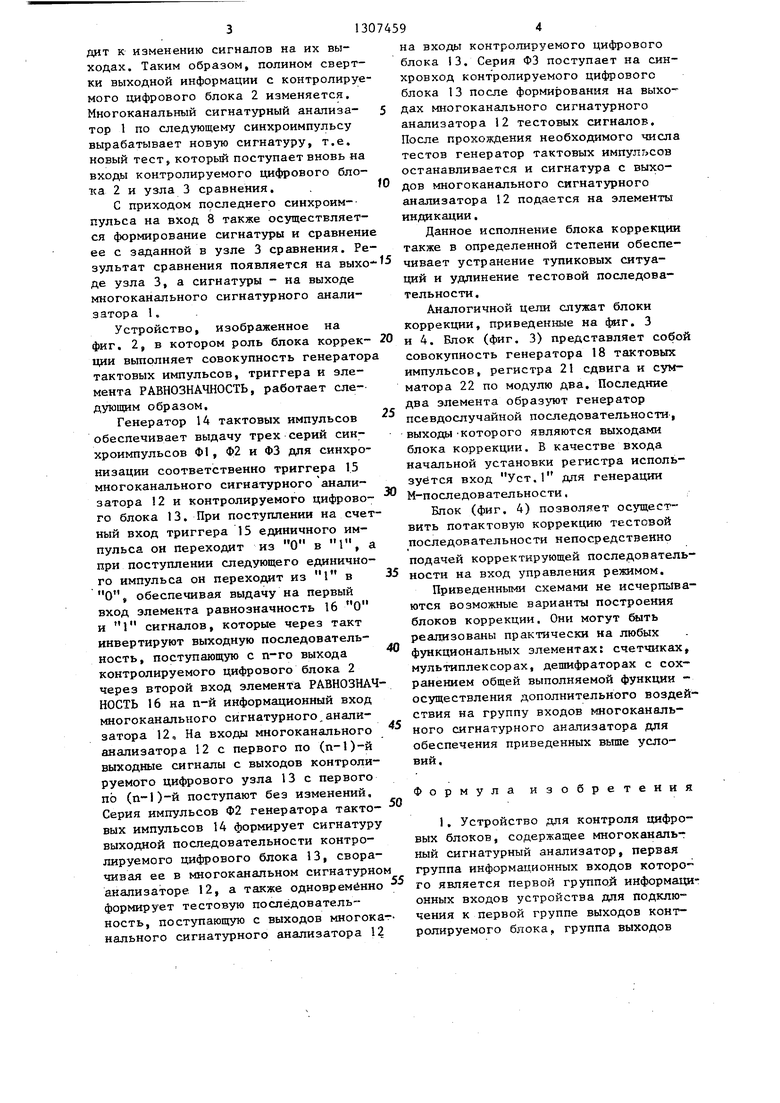

Устройство, структурная схема которого приведена на фиг. 3, содержит генератор 18 тактовых импульсов, многоканальный сигнатурный анализатор 19, контролируемый цифровой блок 20, регистр 21 сдвига, сумматор 22 по модулю два и вход 23 начальной установки. Блок коррекции образован элементами 18, 21 и 22.

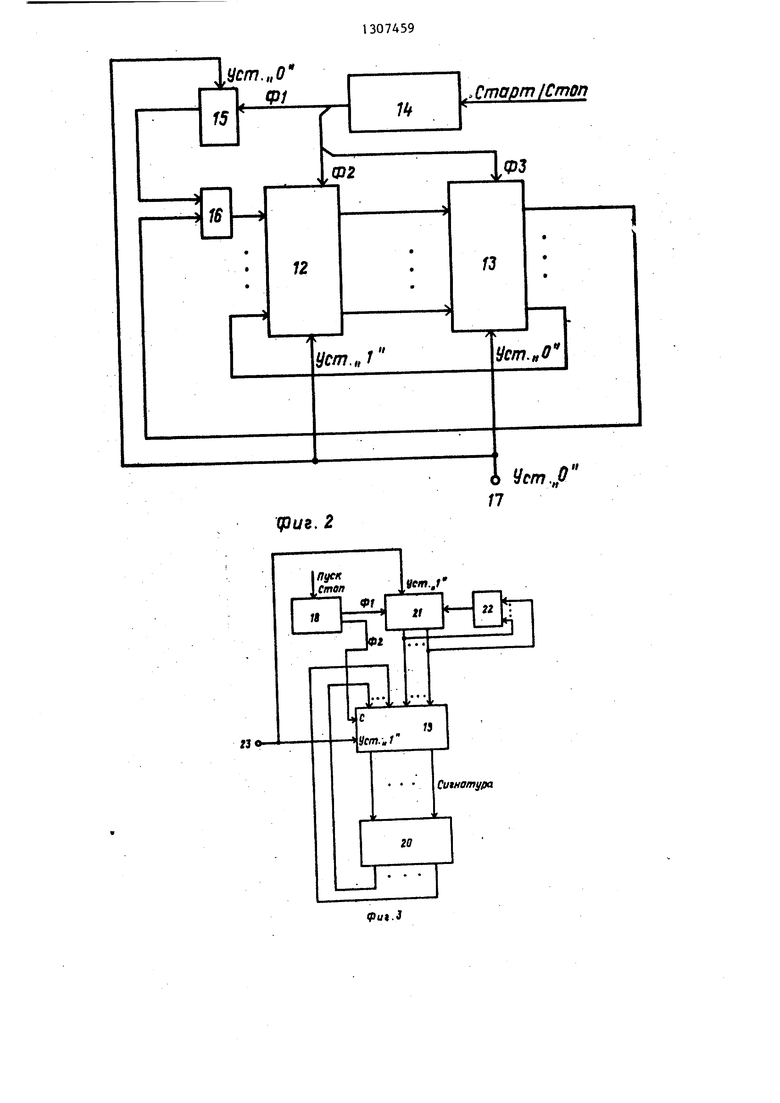

Устройство по фиг. 4 содержит многоканальный сигнатурный анализатор 24, контролируемый цифровой блок 25, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и вход 27 управления ре5кимом.

Устройство по фиг. 1 работает следующим образом.

На вход 10 начальной установки устройства подается сигнал, приводящий счетчик 6 и сигнатурный анализатор 1 в исходное состояние.

На входы 9 узла 3 сравнения из внешних устройство (например, из постоянного запоминающего устройства) подаются коды сигнатур, при которых необходимо произвести коррекцию

5

0

5

входной последбвательности многоканального сигнатурного анализатора 1, что необходимо для устранения тупиковых ситуаций при зацикливании устройства на некоторых тестовых воздействиях; для увеличения длины генерируемой тестовой последовательности и, следовательно, полноты тестирования; для устранения запрещенных комбинаций на входах контролируемого цифрового блока.

Смена кода осуществляется, если это необходимо, через заданный промежуток времени. Если смена кодов не нужна, то настройка узла 3 сравнения на тот или иной код осуществляется с помощью перемычек или путем распайки .

На вход 8 синхронизации устройства подаются синхроимпульсы, которые поступают на вход синхронизации сигнатурного анализатор.а 1 и второй вход элемента И 5, На первый вход элемента И 5 поступает сигнал несравнения из узла 3 через элемент НЕ 4, запрещающий прохождение синхроимпульсов на вход счетчика 6. Многоканальный сигнатурный анализатор 1 выдает тестовые последовательности со своих выходов на входы контролируемого цифрового блока 2 и входа -узла 3 сравнения. С выходов контролируемого блока 2 последовательность сигналов поступает на первую группу входов многоканального сигнатурного анализатора 1 непосредственно и вторую группу входов многоканальнрго сигнатурного анализатора 1 через элементы РАВНОЗНАЧНОСТЬ 7. На вторых входах элементов РАВНОЗНАЧНОСТЬ 7 присутствуют в это время сигналы с выходов счетчика 6, установленного в начальное состояние.

Многоканальный сигнатурный анализатор сворачивает последовательность контролируемых сигналов в сигнатуру по заданному первоначально полиному (собственному полиному),

При появлении на выходе узла 3 сравнения сигнала О, при совпадении кодов, на вход элемента И 5 через элемент НЕ 4 поступает единичный сигнал, разрещающий прохождение синхроимпульсов с входа 8 на синхровход 5 счетчика 6, который переключается в следующее состояние. На входах элементов РАВНОЗНАЧНОСТЬ 7 изменяются сигналы, что соответственно приао0

5

0

5

0

дат к изменению сигналов на их выходах. Таким образом, полином свертки выходной информации с контролируемого цифрового блока 2 изменяется. Многоканальный сигнатурный анализатор 1 по следующему синхроимпульсу вырабатывает новую сигнатуру, т.е. новый тест, который поступает вновь на входы контролируемого цифрового бло- 1са 2 и узла 3 сравнения,

С приходом прследнего синхроим-- пульса на вход 8 также осуществляется формирование сигнатуры и сравнение ее с заданной в узле 3 сравнения. Результат сравнения появляется на выхо - де узла 3, а сигнатуры - на выходе многоканального сигнатурного анализатора 1.

Устройство, изображенное на

на входы контролируемого цифрового блока 3, Серия ФЗ поступает на син- хровход контролируемого цифрового блока 13 после формирования на выходах многоканального сигнатурного анализатора 12 тестовых сигналов, После прохождения необходимого числа тестов генератор тактовых импульсов останавливается и сигнатура с выходов многоканального сигнатурного анализатора 12 подается на элементы индикации.

Данное исполнение блока коррекции также в определенной степени обеспечивает устранение тупиковых ситуаций и удлинение тестовой последовательности.

Аналогичной цели служат блоки коррекции, приведенные на фиг, 3

0

25

30

фиг, 2, в котором роль блока коррек- 20 и 4. Блок (фиг, 3) представляет собой

совокупность генератора 18 тактовых импульсов, регистра 21 сдвига и сумматора 22 по модулю два. Последние два элемента образуют генератор псевдослучайной последовательности, выходы Которого являются выходами блока коррекции. В качестве входа начальной установки регистра используется вход Уст.1 для генерации М-последовательности,

Блок (фиг, 4) позволяет осуществить потактовую коррекцию тестовой последовательности непосредственно подачей корректирующей последовательности на вход управления режимом.

Приведенными схемами не исчерпываются возможные варианты построения блоков коррекции. Они могут быть реализованы практически на любых функциональных элементах: счетчиках, мультиплексорах, дешифраторах с сохранением общей выполняемой функции - осуществления дополнительного воздействия на группу входов многоканального сигнатурного анализатора для обеспечения приведенных выше условий.

Формула изобретения

1, Устройство для контроля цифровых блоков, содержащее многоканаль-г ный сигнатурный анализатор, первал группа информац.ионных входов которо- го является первой rpynnoji информационных входов устройства для подключения к первой группе выходов контролируемого блока, группа выходов

ции выполняет совокупность генератора тактовых импульсов, триггера и элемента РАВНОЗНАЧНОСТЬ, работает следующим образом.

Генератор 14 тактовых импульсов обеспечивает выдачу трех серий синхроимпульсов Ф1, Ф2 и ФЗ дпя синхронизации соответственно триггера 15 многоканального сигнатурного анализатора 12 и контролируемого цифрового блока 13, При поступлении на счетный вход триггера 15 единичного импульса он переходит из О в I, а при поступлении следующего единичного импульса он переходит из 1 в О, обеспечивая выдачу на первый вход элемента равнозначность 16 О и 1 сигналов, которые через такт инвертируют выходную последовательность, поступающую с п-го выхода контролируемого цифрового блока 2 через второй вход элемента РАВНОЗНАЧНОСТЬ 16 на п-й информационный вход многоканального сигнатурного,анализатора 12, На входы многоканального анализатора 12 с первого по (п-1)-й выходные сигналы с выходов контролируемого цифрового узла 13 с первого по ()-й поступают без изменений. Серия импульсов Ф2 генератора тактовых импульсов 14 формирует сигнатуру выходной последовательности контролируемого цифрового блока 13, сворачивая ее в многоканальном сигнатурном анализаторе 12, а также одновременно формирует тестовую последовательность, поступающую с выходов многокат- напьного сигнатурного анализатора 12

35

40

45

50

74594

на входы контролируемого цифрового блока 3, Серия ФЗ поступает на син- хровход контролируемого цифрового блока 13 после формирования на выходах многоканального сигнатурного анализатора 12 тестовых сигналов, После прохождения необходимого числа тестов генератор тактовых импульсов останавливается и сигнатура с выходов многоканального сигнатурного анализатора 12 подается на элементы индикации.

Данное исполнение блока коррекции также в определенной степени обеспечивает устранение тупиковых ситуаций и удлинение тестовой последовательности.

Аналогичной цели служат блоки коррекции, приведенные на фиг, 3

0

25

-

30

-

-

35

-

40

-

45

-

50

многоканального сигнатурного анализатора является группой информационных выходов устройства для подключения к входа м контролируемого блока, отличающееся тем, что, с целью расширения функциональных возможностей за счет расширения клас са контролируемых цифровых блоков, устройство содержит блок коррекции тестовых последовательностей, первая группа информационных входов которого соединена с группой выходов многоканального сигнатурного анализатора, вторая группа информационных входов блока коррекции тестовых последова- тельностей является второй группой информационных входов устройства для подключения к второй группе выходов контролируемого блока, группа управления входов управления режимом бло- ка коррекции тестовых последовательностей является группой входов задания режима устройства, группа выходов блока коррекции тестовых последовательностей соединена с второй группой информационных входов многоканального сигнатурного анализатора, синхровход блока коррекции тестовых последовательностей является синхро- входом устройства,

2. Устройство по п. 1, отличающееся тем, что блок кор

рекции тестовых последовательностей содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом блока, первый и второй входы элемента ИСКЛЮЧАЩЕЕ ИЛИ являются вторым информационным входом и входом управления режимом блока соответственно.

3. Устройство по п, 1, отличающееся тем, что блок коррекции тестовых последовательностей

содержит счетный триггер и элемент РАВНОЗНАЧНОСТЬ, первый вход которого соединен с выходом счетного триггера счетный вход которого является син- хровходом блока, второй вход и выход элемента РАВНОЗНАЧНОСТЬ являются соответственно вторым информационным входом и выходом блока.

4, Устройство поп, 1, отличающееся тем, что блок .коррекции тестовых последовательностей содержит регистр сдвига и сумматор по модулю два, выход которого соединен с информационным входом регистра сдвига, группа выходов которого соединена с группой входов сумматора по модулю два и является группой выходов блока, синхровход регистра Сдвига является синхровходом блока.

5, Устройство по п, 1, отличающееся тем, что блок коррекции тестовых последовательностей содержит счетчик, элемент И, элемент НЕ, группу элементов РАВНОЗНАЧНОСТЬ и узел сравнения, первая и вторая группы информационных входов которого являются группой информационных входов и группой входов управления режимом блока соответственно, выход узла сравнения через элемент НЕ подключен к первому входу элемента И, второй вход которого является синхровходом блока, выход

элемента И соединен со счетным входом счетчика, группа выходов которого соединена с первыми входами элементов РАВНОЗНАЧНОСТЬ группы, вторые входа и выходы которых являются второй группой информационных входов и группой выходов блока соответственно ,

12

Уст.,,1

фиг. 2

Ф2

ФЗ

ГЗ

Уст.„0

4 ст,„0 Л

230

27

офиг, 4

Составитель С, Старчихин Редактор Л. Пчолинская Техред Л.Олейник Корректор А. Ильин

Заказ 1634/49Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1381509A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля многовыходных логических элементов | 1985 |

|

SU1345198A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1603386A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

Изобретение относктся к вычислительной технике и автоматике и может быть использовано для контроля многовыходных цифровых схем радиоэлектронной аппаратуры. Целью изобретения является расширение функци.овальных возможностей устройства за счет расширения класса контролируемых цифровых блоков. Устройство содержит многоканальный сигнатурный анализатор 1, контролируемый цифровой блок 2, узел 3 сравнения, зле- мент НЕ 4, элемент И 5, счетчик 6, группу элементов РАВНОЗНАЧНОСТЬ 7, синхровход 8, группу управляющих входов 9 режима, вход 10 начальной установки. Элементы 3 - 7 в совокупности образуют блок 11 коррекции тестовых последовательностей. Блок 1i может быть выполнен различными способами. Его основные функции: устранение тупиковых ситуаций при зацикливании устройства на некоторых тестовых воздействиях} увеличение длины генерируемой тестовой последовательности и тем самым полноты тестирования; устранение запрещенных комбинаций на входах контролируемого цифрового блока. 4 з.п. ф-лы, 4 ил. --1 (Л СХ5 1 сд со

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1078430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-30—Публикация

1985-03-01—Подача