13

Изобретение о гнос1-пч;я к автоматике и вычислительной технике и может быть использовано для контроля многовыход-- ных логических элементов и цифровых блоков.

Целью изобретения является повьшш- ние производительности контроля,

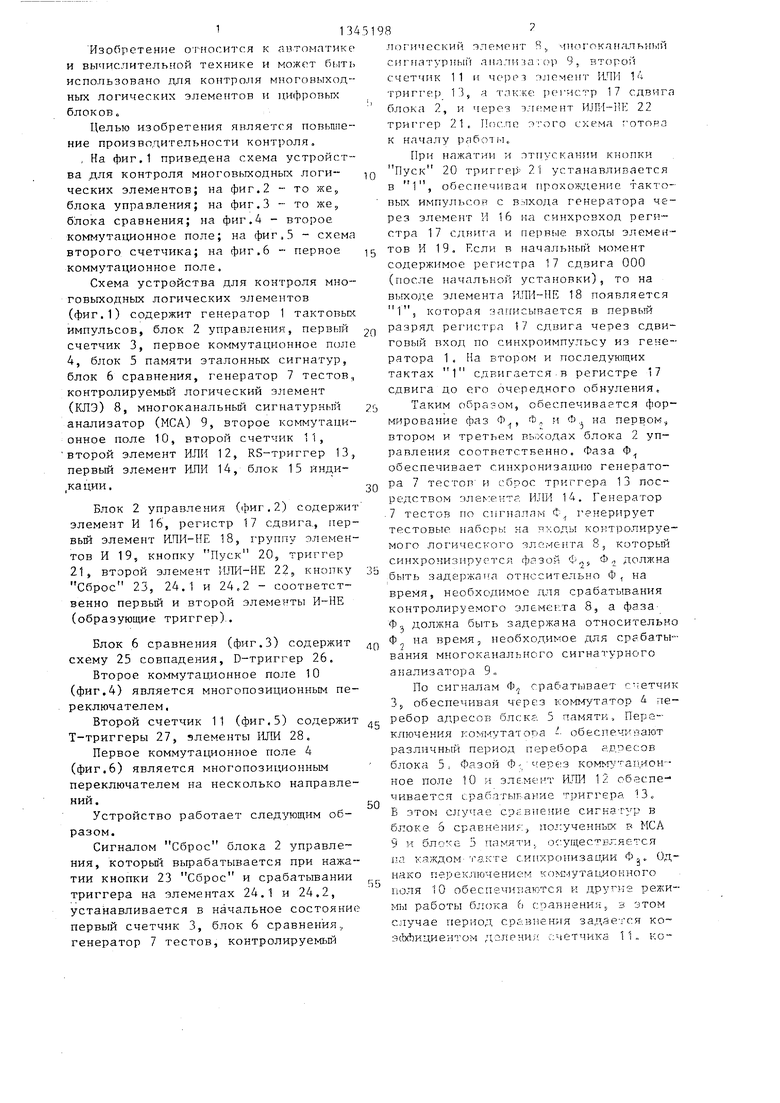

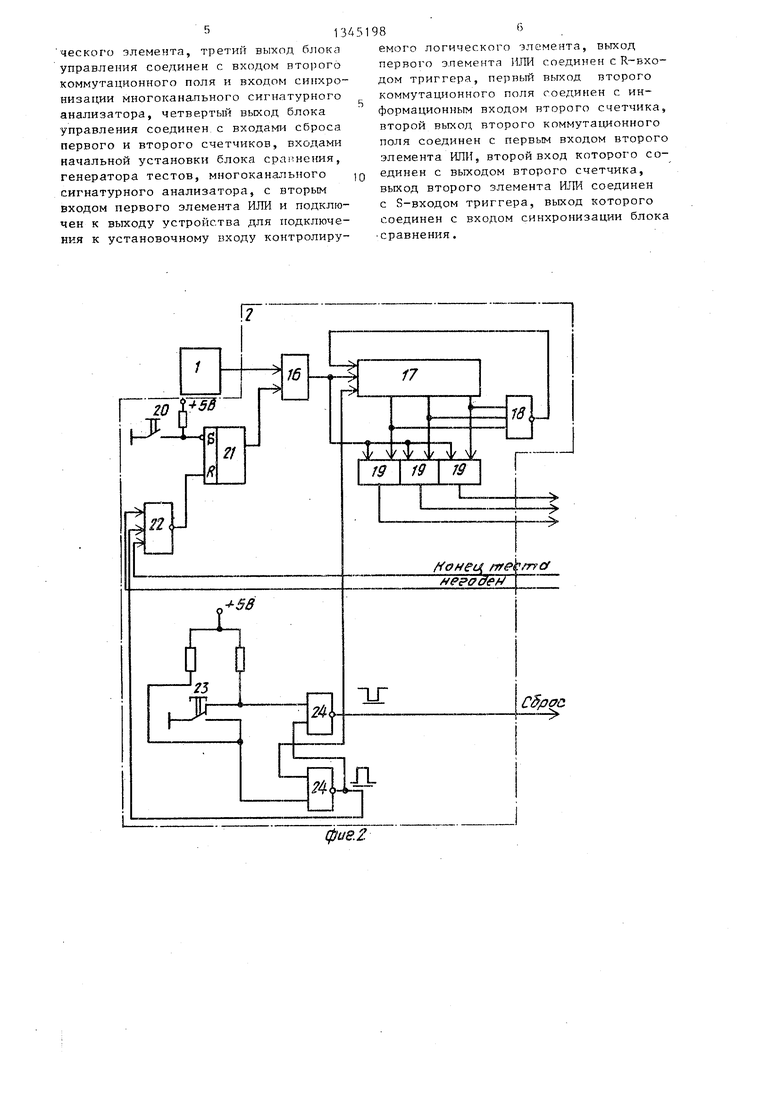

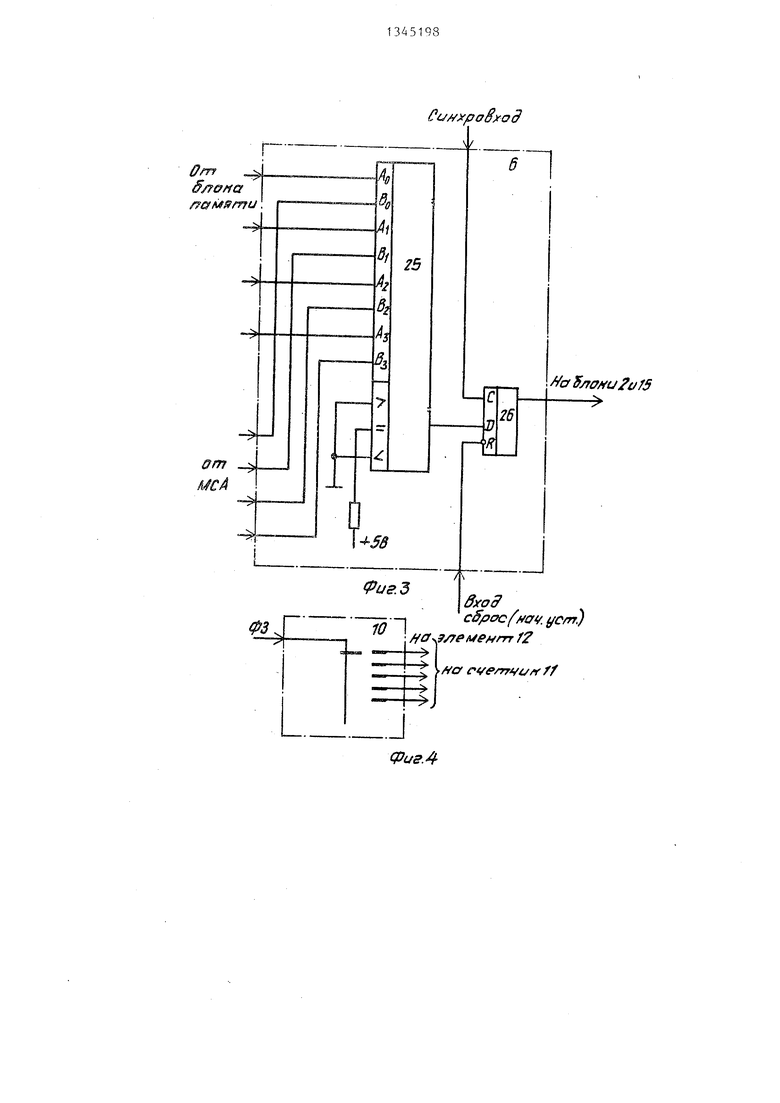

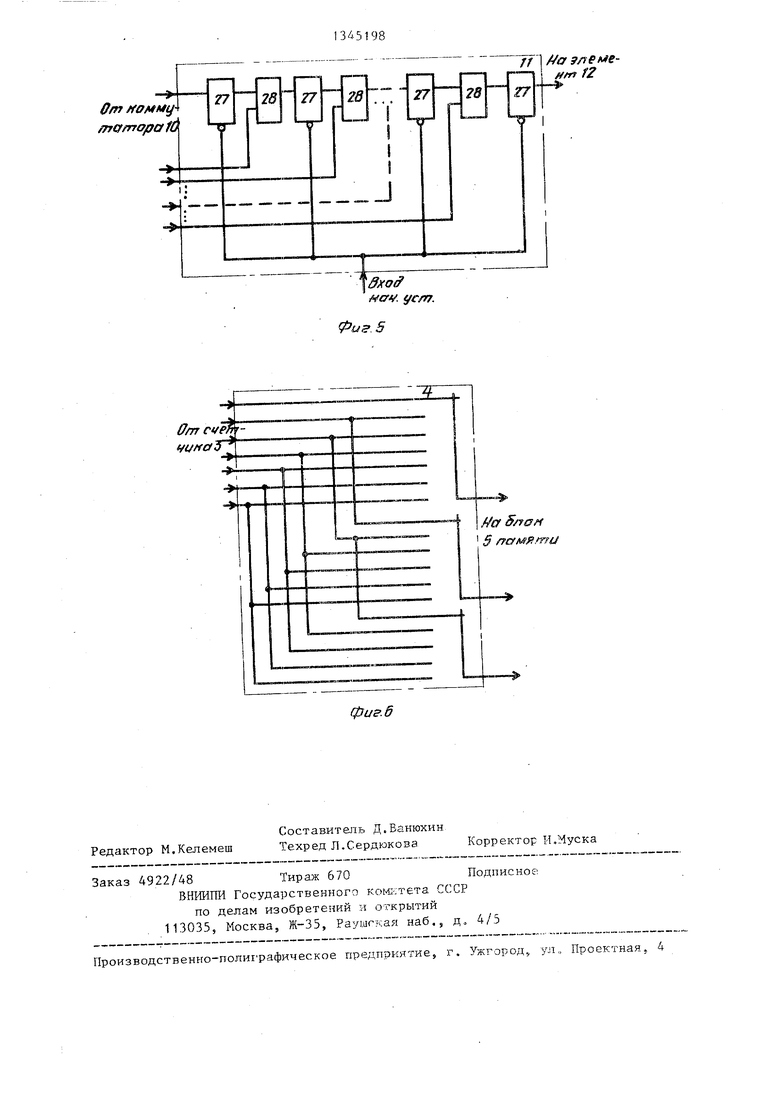

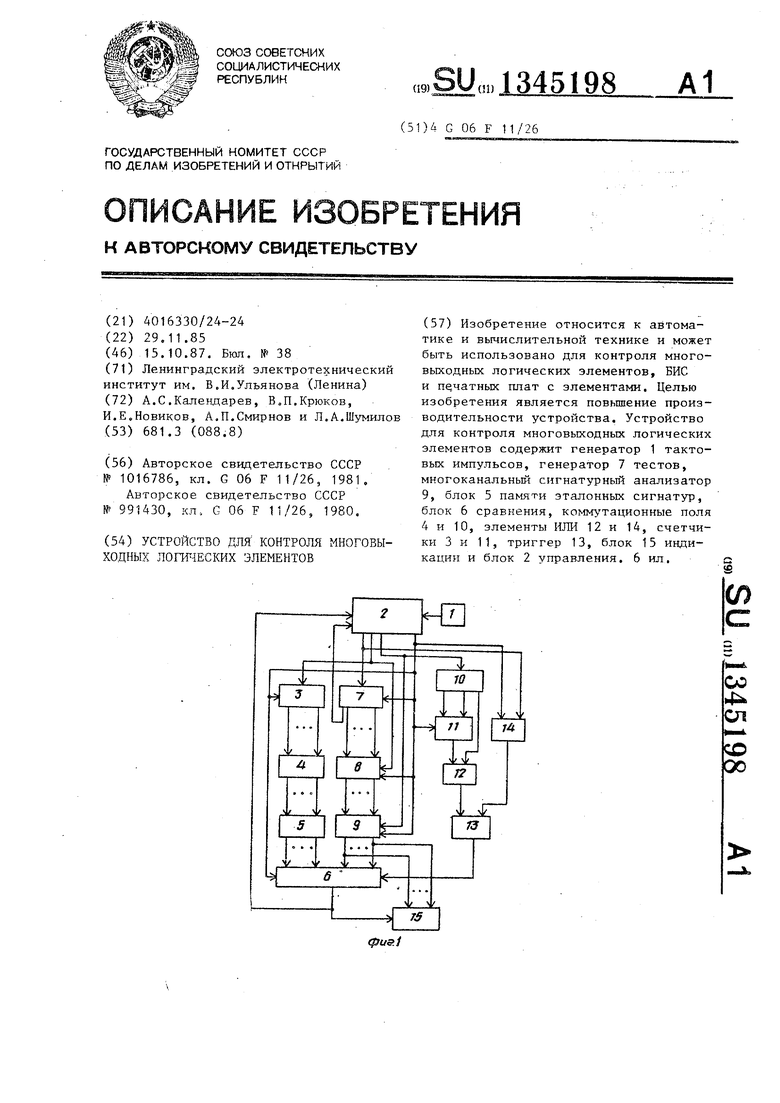

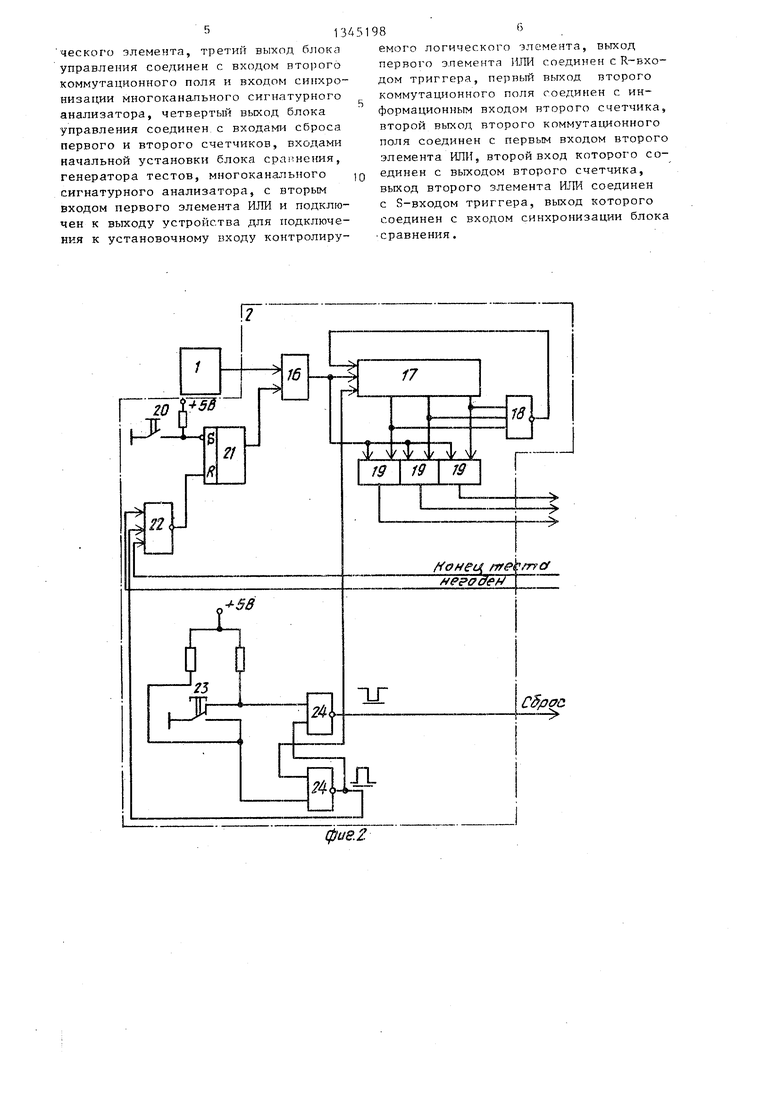

, На фиг.1 приведена схема устройства для контроля многовыходных логических элементов; на фиг.2 - то же,, блока управления; на фиг.З - то же, блока сравнения; на фиг.4 - второе коммутационное поле; на фиг,5 - схема второго счетчика; на фиг.6 - первое коммутационное поле.

Схема устройства для контроля мно-- говыходных логических элементов (фиг.1) содержит генератор 1 тактовьк импульсов, блок 2 управления, первый счетчик 3, первое коммутационное поле 4, блок 5 памяти эталонных сигнатур, блок 6 сравнения, г енератор 7 тестов, контролируемый логический элемент (КЛЭ) 8, многоканальньй сигнатурньш анализатор (МСА) 9, второе KONfMyTauH-- онное поле 10, второй счетчик 11, второй элемент ИЛИ 12, RS-триггер 13, первый элемент ИПИ 14, блок 15 йнди- ,ка ции.

Блок 2 управления ((иг,2) содержит элемент И 16, регистр 17 сдвига,, пер- вьм элемент И.ПИ-НЕ 18, группу элементов И 19, кнопку Пуск 20, триггер 21, второй элемент ИЛИ-НЕ 228 кнопку Сброс 23, 24.1 и 24,2 - соответственно первый и второй элементы (образующие триггер),.

Блок 6 сравнения (фиг.З) содержит схему 25 совпадения, D-триггер 26,

Второе коммутащюнное поле 10 (фиг,4) является многопозиционным переключателем,

Второй счетчик 11 (фиг,5) содержит Т-триггеры 27, элементы И1М 28.

Первое коммутационное поле 4 (фиг.6) является многопозиционным переключателем на несколько направлений.

Устройство работает следующим образом.

Сигналом Сброс блока 2 управления, которьпЧ вырабатывается при нажатии кнопки 23 Сброс и срабатывании триггера на элементах 24.1 и 24.2, устанавливается в начальное состояние первый счетчик 3, блок 6 сравнения, генератор 7 тестов, контролируеТ ШШ

0

5

Ь

198

,11огический элемент В, -.щогокан. шьный сигнатурный :ia ; (ip 9, второй счетчнк 11 (I 401501 элемент 1Д триггер 13, а т.мкже регистр 17 сдвнга блока 2, и через т.-гемент HJni- H 22 триггер 21. ,,пе этого схема г отона к началу работы.

При нажатии и птгтускани 1 кнопки Пуск 20 триггер 21 устанавливается в 1, обеспечивач пpoлoж, тактовьк импульсов с в,-1хода генератора через элемент И 16 на синхровход регистра 17 сдяит Я и первые входы элементов И 19, Если в начальньм момент содержимое регистра 17 сдвига 000 (после начальной установки), то на выходе элемента 18 появляется 1, которая записывается в первьй разряд рег нстра 17 сдвига через сдвиговый вход по синхроимпульсу из ге:-:е- ратора 1, На втором и последующих тактах 1 сдвигается в регистре 17 сдвига до его очередного обнуления. Таким образом, обеспечивается формирование фаз Ф, ft.

я Ф,, на первом.

0

0

5

0

втором и третьем выходах блока 2 управления соответственно. Фаза Ф обеспечивает синхронизац -(ю генератора 7 тестов и сброс триггера 13 посредством элекекТс ; ИЛИ 14. Генератор ,7 тестов по cnrHanaNs Ф, I eiiepHpyeT тестовые, наборь; на якоды контролируемого логического элемента В, который синхронизируется, фазой Ф должна быть задержана относительно Ф, на время, необходимое для срабаты.вання контролируемого элемента 8, а фаза Ф.j должна быть задержана относительно Ф на время, необходимое для срабатывания мнoгo caнaлhнoгo сигнатурного анализатора 9„

По сигналам Ф срабатьчвает счетчик 3., обеспечивая через KOMtfyra.rop 4 перебор адресов блскг 5 памяти. Переключения коммутатора i- обеспечивают различный период перебора адоесов блока 5, Фазой Ф. коммз- а1,ион-- кое поле 10 и эле,мент ЕШ-1 12 обеспечивается срабатыг;.ание триггера 13„

8этом случае cpcBiieiiHe сигкв гур в блоке 6 сравнения:, по1:ученньсх в МСА

9и блоке 5 памяти, осугдеств.гяется

па к,ч,ждом- ivaKTe с,и1 хронизаиди Ф. Однако переключением коммута1 лонного поля 10 обеспечпиактся и другие режи- М) работы бло1са 6 срат1нения,, з этом с,тучае период сравнения задается ко- эйхЬициентом ;v2,,neHH; : счетчика 11„ ко

31

торьгй также через элемент ППИ 12 обеспечивает срабатывание триггера 13 и блока 6 сравнения.

Сигнатура с ВЫХОДОБ МСА 9 вьиает- ся в блок 15 индикации, результат сравнения сигнатур также выдается в блок 15,

Если на каком-то такте, например при контроле наиболее короткого канала КЛЭ 8, произошло несравнение сигнатур, то блок индикации высвечивает сигнал Не годен, а блок 6 сравнения посредством элемента ИЛИ-НЕ 22 блока 2 управления останавливает процесс контроля.

Кроме того, контроль останавливается посредством элемента ИЛИ-НЕ 22 при появлении 1 на последнем выходе генератора 7 тестов (например, в старшем разряде счетчика).

Блок 6 сравнения на фиг.З обеспечивает сравнение эталонной сигнатуры из блока 5 памяти и МСА 9 посредством схемы 25 совпадения, а вьщача сигнала на выход блока 6 осуществляется по синхроимпульсам, поступающим на синх- ровход триггера 26, имеющего также вход Сброс, управляемый сигналами Сброс блока 2 управления.

Коммутационное поле 10 (фиг.4) содержит переключатель, обеспечивающий подключение фазы Ф к одному из своих выходов. В это время на остальные выходы 10 подаются 0000. Цепи коммутации нулей не показаны.

Счетчик 11 (фиг.5) состоит из последовательно соединенных Т-триггеров 27 и элементов ИЛИ 28, вторые входы элементов ИЛИ 28 и вход первого Т- триггера 27 используются для приема информации от коммутатора 10. Счетчик 11 используется как делитель частоты, выходом его является выход последнего Т-триггера. Вход начальной установки счетчика 11 работает по сигналам Сброс блока 2 управления.

Коммутационное поле 4 (фиг.6) обеспечивает переключение выходов счетчика 3 и входов блока 5 памяти.

Таким образом, предложенное устройство обеспечивает увеличение производительности контроля за счет регулирования периода формирования эталонной сигнатуры и периода сравнения сигнатур посредством первого счетчика, цервого коммутационного поля и блока памяти, а также второго коммутационного поля, второго счетчика.

0

5

0

5

0

0

5

0

5

98

первого и второго элементов ИЛИ, триггера и блока сравнения. Эти периоды подстраиваются под наиболее короткие каналы контролируемой схемы и, если длины каналов отличаются в 2-3 раза, то возможно 2-3-кратное увеличение производительности контроля с

Формула изобретения

YcTpopiCTBo для контроля многовы- ходньгх логических элементов, содержащее генератор тактовых импульсов, блок управления, первый счетчик, ге нератор тестов, блок памяти эталонных сигнатур, многоканальный сигнатурный анализатор и блок сравнения, причем выход генератора тактовых импульсов соединен с входом синхронизации блока управления, группа выходов генератора тестов образует выход устройства для подключения к информационному входу контролируемого логического элемента, группа информационных входов многоканального сигнатурного анализатора образует вход устройства для подключения к информационному выходу контролируемого логического элемента, выход блока памяти эталонных сигнатур соединен с первым информационным входом блока сравнения, выход многоканального сигнатурного анализатора соединен с В7 орь м информационным входом блока сравнекия и является инфор- мационньп выходом устройства, отличающееся тем, что, с целью повышения производительности контроля, устройство содержит первое и второе коммутационные поля, второй счетчик, два элемента ИЛИ и триггер, причем первый и второй входы останова блока управления соединены соответственно с выходом блока сравнения и выходом конца теста генератора тестов, выход блока сравнения является выходом годности устройства, группа выходов первого счетчика соединена с группой входов первого KOMHyTa iOHHO- го поля, выход которого соединен с адресным входом блока памяти эталонных сигнатур, первый выход блока управления соединен с первым входом первого элемента ИЛИ и входом пуска генератора тестов, второй выход блока управления соединен со счетным входом первого счетчику и подключен к выходу устройства для подключения к входу синхронизации контролируемого логи 1345 ческого элемента, третий выход блока управления соединен с входом второго коммутационного поля и входом синхронизации многокаиапьного сигнатурного анализатора, четвертый выход блока управления соединен.с входами сброса первого и второго счетчиков, входами начальной установки блока сравнения, генератора тестов, многоканального Q сигнатурного анализатора, с вторым входом первого элемента ИЛИ и подключен к вьпсоду устройства для подключения к установочному входу контролиру98

емого логического элемента, выход первого элемента ИЛИ соединен с R-BXO- дом триггера, первый выход второго коммутационного поля соединен с информационным входом второго счетчика, второй выход второго коммутационного поля соединен с первьгм входом второго элемента ИЛИ, второй вход которого соединен с выходом второго счетчика, выход второго элемента ИЛИ соединен с S-входом триггера, выход которого соединен с входом синхронизации блока

Сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля много- выходных логических элементов, БИС и печатных плат с элементами. Целью изобретения является повышение производительности устройства. Устройство для контроля многовыходных логических элементов содержит генератор 1 тактовых импульсов, генератор 7 тестов, многоканальный сигнатурньш анализатор 9, блок 5 памяти эталонных сигнатур, блок 6 сравнения, коммутационные поля 4 и 10, элементы ИЛИ 12 и 14, счетчики 3 и 11, триггер 13, блок 15 индикации и блок 2 управления. 6 ил. с (О

f

фи8.2

ffm

ФЗ

)fod 6

26

/ aS ff/fu tJfS

SB ua5

Sxoff c pcycff at/. уст.)

ffff 9/7f мент f

rve/rrt/aff //

.J

сригА

От /потора tC

27

2В

П

ау/тел(е- /fm fZ

27

28

Z7

Ниет

с

ff/TTCvefir

(/t/ffCta

Редактор М.Келемеш

Составитель Д.Ванюхин Техред Л.Сердюкова

Заказ 4922/48Тираж 670Подписное.

ВНИИПИ Государственного ко№-:тета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушгкая наб., д. 4/5

Производственно-полиг рафическое предприятие, г, Ужгород, ул„ Проектная. 4

8}(off Vo уст.

Фиг 5

f/a /7Gfi

5

фиг. 6

Корректор И.Муска

| Устройство для контроля логических блоков | 1981 |

|

SU1016786A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1985-11-29—Подача