Изобретение отн-осится к контрольно-измерительной технике и может быть использовано для параметрическо го контроля интегральных схем.

Цель изобретения - упрощение уст- ройства при контроле интегральных схем с больи№1м количеством тестов,

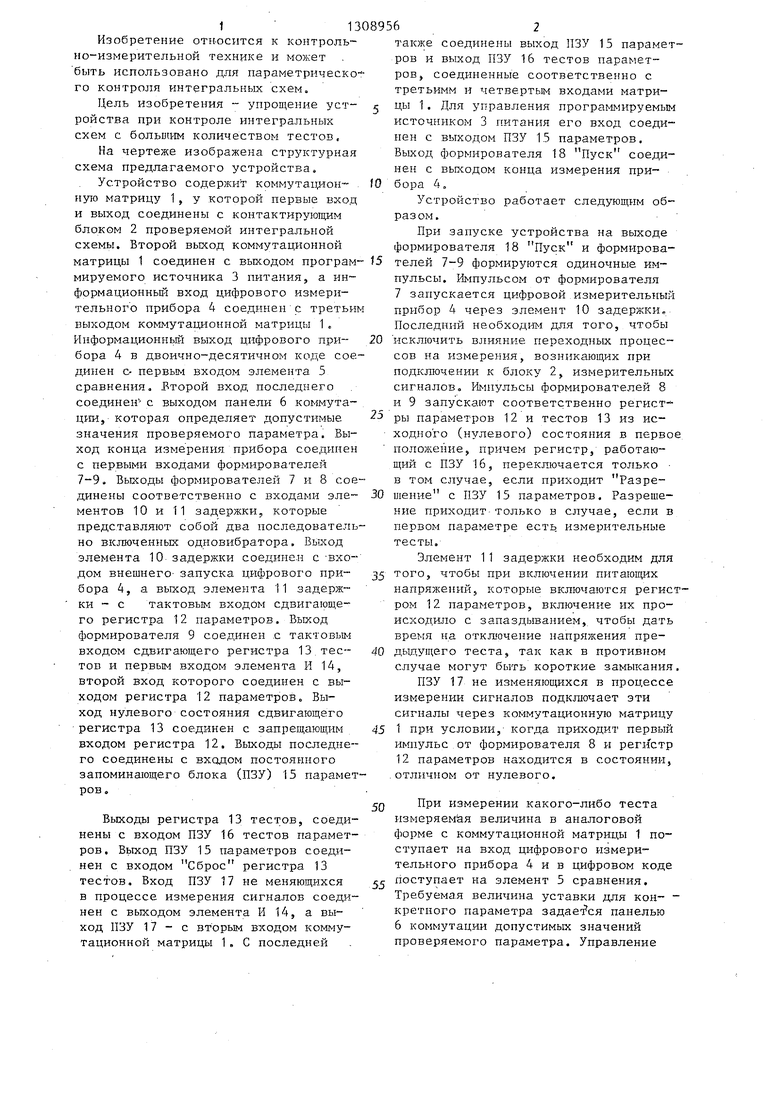

На чертеже изображена структурная схема предлагаемого устройства.

Устройство содержит коммутацион- нзпо матрицу 1 , у которой первые вход и выход соединены с контактирующим блоком 2 проверяемой интегральной схемы. Второй выход коммутационной матрицы 1 соединен с вькодом програм мируемого источника 3 питания, а ин формационньщ вход цифрового измерительного прибора 4 соединен с третьи выходом коммутационной матрицы 1. Информационньш выход цифрового при- бора 4 в двоично-десятичном коде соединен с- первым входом элемента 5 сравнения, Бторой вход последнего соединен - с выходом панели 6 коммута- црш, которая определяет допустимые значения проверяемого параметра. Выход конца измерения прибора соединен с первыми входами формирователей 7-9. Выходы формирователей 7 и 8 соединены соответственно с входами эле ментов 10 и И задержки, которые представляют собой два последовательно включенных одновибратора. Выход элемента 10 задержки соединен с -входом внешнего- запуска цифрового при- бора 4, а выход элемента 11 задержки - с тактовым входом сдвигающего регистра 12 параметров. Выход формирователя 9 соединен с тактовым входом сдвигающего регистра 13.тес- тов и первым входом элемента И 14, второй вход которого соединен с выходом регистра 12 параметров., Выход нулевого состояния сдвигающего регистра 13 соединен с запрещающим входом регистра 12, Выходы последнего соединены с входом постоярпюго запоминшощего блока (ПЗУ) 15 параметров,

Выходы регистра 13 тестов, соединены с входом ПЗУ 16 тестов параметров, Вькод ПЗУ 15 параметров соединен с входом Сброс регистра 13 тестов. Вход ПЗУ 17 не меняющихся в процессе измерения сигналов соединен с выходом элемента И 14, а выход ПЗУ 17 - с BTOpbLM входом коммутационной матрицы 1, С последней

также соединены выход ПЗУ 15 параметров и выход ПЗУ 16 тестов параметров, соединенные соответственно с третьимм и четвертым входами матрицы 1, Для управления программируемым источником 3 питания его вход соединен с выходом ПЗУ 15 параметров. Выход формирователя 18 Пуск соединен с выходом конца измерения прибора 4.

Устройство работает следующим образом.

При запуске устройства на выходе формирователя 1В Пуск и формирователей 7-9 формируются одиночные импульсы. Импульсом от формирователя 7 запускается цифровой измерительный прибор 4 через элемент 10 задержки. Последний необходим для того, чтобы исключить влияние переходных процессов на измерения, возникающих при подключении к блоку 2, измерительных сигналов. Импульсы формирователей 8 и 9 запускают соответственно регист-- ры параметров 12 и тестов 13 из исходного (нулевого) состояния в перво положение, причем регистр, работающий с ПЗУ 16, переключается только - в том случае, если приходит Разрешение с ПЗУ 15 параметров. Разрешение приходит только в случае, если в первом параметре есть, измерительные тесты.

Элемент 11 задержки необходим для того, чтобы при включении питающих напрялсений, которые включаются регисром 12 параметров, включение их происходило с запаздыванием, чтобы дать время на отключение напряжения предыдущего теста, так как в противном случае могут быть короткие замыкания

ПЗУ 17 не изменяющихся в процессе измерении сигналов подключает эти сигналы через коммутационную матрицу 1 при условии, когда приходит первый импульс от формирователя 8 и регистр 12 параметров находится в состоянии, .отличном от нулевого.

При измерении какого-либо теста измеряемая величина в аналоговой форме с коммутационной матрицы 1 поступает на вход цифрового измерительного прибора 4 и в цифровом коде поступает на элемент 5 сравнения. Требуемая величина уставки для кон- кретного параметра задает ся панелью 6 коммутации допустимых значений проверяемого параметра. Управление

переключением уставок, а также управление программируемым источником 3 питания производится от ПЗУ 15 параметров. Подключение требуемых сигналов на каждом тесте к изменяемой интегральной схеме производится коммутационной матрицей 1, управление которой .осуществляется ПЗУ 15-17.

Для обеспечения режима кольца используется импульс Конец измерения цифрового измерительного прибора. Этим импульсом запускаются формирователи 7-9 при последующих (после первого) тестах. В случае

через постоянный запоминающий блок не меняющихся в процессе измерения сигналов соединен с третьим входом коммутационной матрицы, выход сдвигающего тестов через постоянный запоминающий блок тестов параметра соедтшен с четвертым входом коммутационной матрицы, а информационный выход постоянного запоминающего

сигнала. Брак, снимаемого с элемен- 15 измерения сигналов,выход элемента И та 5 сравнения, на формирователи 7-9 приходит Запрет и цикл измерения на этом тесте остановлен.

Устройство параметрического контроля легко перестраивается с одного 20 типа ИС на другой посредством замены одной печатной платы ПЗУ, не требует математического обеспе- ения, имеет высокое быстродействие и точность измерения и малые габариты, что 25 блока параметров соединен с пятым позволяет использовать его как в се- входом коммутационной матрицы, выход рийном производстве, так и при перио- формирователя Пуск соединен с пер- дических испытаниях со стационарными выми входами первого, второго и камерами тепла, барокамерами или для третьего формирователей и выходом измерения параметров в процессе элек-jg цифрового измерительного прибора, тротермотренировки.вход запуска которого через первый

элемент задержки соединен с выходом

Формула изобретенияпервого формирователя, выход второго

формирователя через второй элемент

Устройство параметрического конт- - задержки с тaктoвы входом роля интегральных схем, содержащее сдвигающего регистра параметров, пер- элемент сравнения, панель коммутации, коммутационную матрицу, контактирующий блок исследуемой микросхемы, .элемент И, программируемьш источник 40 питапия, цифровой измерительньш прибор и формирователь Пуск, причем первые вход и выход коммутационной матрицы соединены соответственно с выходом и входом контактирующего бло- 45 нен с входом прогргтммируемого источ- ка исследуемой микросхемы, второй ника питания, третий выход - с вхо- вход - с выходом программируемого источника питания, второй выход - с измерительным входом цифрового измерительного прибора, информационный 50 выход которого соединен с первым

вый выход которого соедШ Ген с первьм входом элементами, второй вход которого соединен с выходом третьего формирователя и тактовым входом сдвигающего регистра тестов, вход сброса которого соединен с первым выходом постоянного запоминающего блока параметров, второй выход которого соедидом панели коммутации, вход - с вто- рьм выходом сдвигаюа1;его регистра параметров, а выход элемента сравнения соединен с вторьми входами первого, второго и третьего формирователей.

входом элемента сравнения, второй вход которого соединен с выходом панели коммутации, отличающееся тем, что, с целью упрощения устройства при контроле интегральных схем с большим количеством тестов, в iiei o введе.ны первый, второй и третий формирователи, первый и второй элементы задержки, сдвигающие регистры тестов и параметров, элемент. И, постоянный запоминающт блок параметров, постоянный запоминающий блок тестов параметра и постоянньй запоми- нающ1ш блок не меняющихся в процессе

через постоянный запоминающий блок не меняющихся в процессе измерения сигналов соединен с третьим входом коммутационной матрицы, выход сдвигающего тестов через постоянный запоминающий блок тестов параметра соедтшен с четвертым входом коммутационной матрицы, а информационный выход постоянного запоминающего

измерения сигналов,выход элемента И

блока параметров соединен с пятым входом коммутационной матрицы, выход формирователя Пуск соединен с пер- выми входами первого, второго и третьего формирователей и выходом цифрового измерительного прибора, вход запуска которого через первый

задержки с тaктoвы входом сдвигающего регистра параметров, пер- нен с входом прогргтммируемого источ- ника питания, третий выход - с вхо-

вый выход которого соедШ Ген с первьм входом элементами, второй вход которого соединен с выходом третьего формирователя и тактовым входом сдвигающего регистра тестов, вход сброса которого соединен с первым выходом постоянного запоминающего блока параметров, второй выход которого соедизадержки с тaктoвы входом сдвигающего регистра параметров, пер- нен с входом прогргтммируемого источ- ника питания, третий выход - с вхо-

дом панели коммутации, вход - с вто- рьм выходом сдвигаюа1;его регистра параметров, а выход элемента сравнения соединен с вторьми входами первого, второго и третьего формирователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров полупроводниковых приборов | 1978 |

|

SU781721A1 |

| Устройство параметрического контроля интегральных схем | 1976 |

|

SU694822A1 |

| Устройство для параметрического контроля интегральных схем | 1981 |

|

SU985755A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Тестер контроля и диагностики электронных модулей | 1986 |

|

SU1396099A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2080653C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

| Устройство для параметрического контроля интегральных схем | 1981 |

|

SU985755A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство параметрического контроля интегральных схем | 1976 |

|

SU694822A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-05-07—Публикация

1986-01-06—Подача