(5) УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

| Устройство для контроля параметров | 1986 |

|

SU1403074A1 |

| Устройство для контроля интегральных схем | 1984 |

|

SU1208555A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU748422A1 |

1

Изобретение относится к контрольно-измерительнрй технике и может быть использовано для параметрического контроля интегральных схем.

Известно устройство для параметрического контроля интегральных схем (ИС), содержащее коммутационную матрицу, программируемый источник питания, дешифратор, счетчик выводов, генератор тактовых импульсов, измеритель, элементы И, элементы сравнения, панели коммутации Г1.

Данное устройство обеспечивает контроль параметров ИС (токов утечки в частности ) по каждому выводу после-,j довательно

Однако данное устройство контроля обладает следующими недостатками: время контроля по каждом выводу ИС неизменно, а поэтому общее время конт-20 роля ИС велико, кроме того, наличие большого количества коммутационных планок усложняет переход от одного типа ИС к другому типу.

Наиболее близким к предлагаемому является устройство для параметричес кого контроля интегральных схем, содержащее сдвиговый регистр, мэммутатор, коммутационную планку, измери тельный элемент ИЛИ, элементы И, регистр, триггер, генератор тактовых импульсов 2 .

Известное устройство обеспечивает ограничение допустимого времени контроля по каждому выводу ИС, что дает более быстрое выделение признака годности или брака по каждому выводу ИС. Однако оно фиксирует появление признака Брак-Годен и не осуществляет. никаких воздействий на ИС, которые способствовали бы стоку паразитных зарядов с ИС, что препятствует ускорению измерений по каждому выводу отдельно, а следовательно снижает производительность известного устройства.

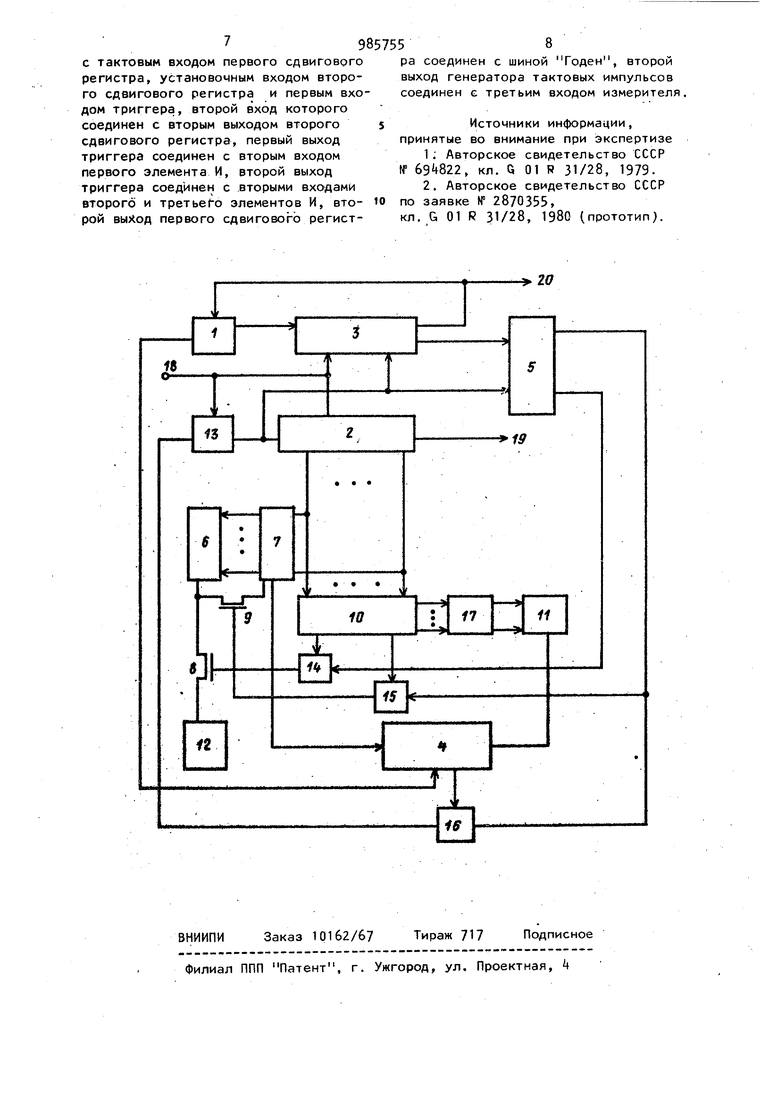

Цель изобретения - повышение производительности контроля за-счет формирования на интегральной схеме дополнительных воздействий, способствующих ускорению стока паразитных зарядов с ИС. Поставленная цель достигается тем что в устройство для параметрического контроля интегральных схем, содержащее триггер, генератор тактовых импульсов, элемент ИЛИ, первый, второй и третий элементы И, и первый сдвиговый регистр, соединенный первыми выходами с входами коммутационной планки и со входами коммутатора, первые выходы которого соединены с первыми выходами устройства, второй выход коммутатора соединен с первым вхо дом измерителя, первые выхсэды коммута ционной планки соединены с входами ре,гистра, выходы которого соединены с входами программируемого блока питающего напряжения, выход которого соединен со вторым входом измерителя введены второй сдвиговый регистр, первый и второй электронные ключи, блок питающего напряжения, шина Брак, шина Пуск, шина Годен, причем второй вход устройства соединен с выходами первого и второго электронных ключей, первый вход первого электронного ключа соединен с выходом блока питающего напряжения, второй вход первого электронного ключа соединен с выходом первого элемента И, первый вход которого соединен с вторым выходом коммутационной планки, третий выход которой соеди нен t первым входом второго элемента И, выход которого соединен с первым входом второго электронного ключа, второй вход которого соединен с третьим выходом коммутатора, выход измерителя соединен с первым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ второй вход которого соединен с шиной Пуск и входом установки первого сдвигового регистра и сбросовым входом второго сдвигового регистра, тестовый вход которого соединен с выходом генератора тактовых импульсов, вход которого соединен с первым выходом второго сдвигового регистра и шиной Брак, выход элемента ИЛИ соединен с тактовым входом первого сдвигового регистра, установочным входом второго сдвигового регистра и первым входом триггера, второй вход которого соединен с вторым выходом второго сдвигового регистра, первый выход триггера соединен с вторым входом первого элемента И, второй выход три|- гера соединен с вторыми входами второго и третьего элементов И, второй выход первого сдвигового регистра со единен с шиной Годен второй выход генератора тактовых импульсов соединен с третьим входом измерителя. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит генератор 1 тактовых импульсов, первый сдвиговый регистр 2, второй сдвиговый регистр 3, измеритель , триггер 5, интегральную схему 6, коммутатор 7 первый 8 и второй 9 электронные ключи, коммутационную планку 10, программируемый блок 11 питающих напряжений, блок 12 питающего напряжения, элемент ИЛИ 13, первый 1, второй 15 и третий 16 элементы И, регистр 17, шину Пуск 18, шину Годен 19, шину Брак 20. Устройство работает следующим образом. Сигнал с шины Пуск 18 записывает единицу в первый разряд сдвигового регистра 2 и сбрасывает в ноль сдвиговый регистр 3. Сигнал с выхода элемента ИЛИ 13 взводит триггер 5, записывает единицу в первый разряд сдвигового регистра 3 и сдвигает единицу в сдвиговом регистре 2 на один разряд. Сдвиговый регистр 2 через коммутатор 7 подключает выводы интегральной схемы 6 к измерителю 4. Кроме того, сдвиговый регистр 2 через коммутационную планку 10, соединен с регистром 17, который задает режим измерений на программируемый блок 11 питающего напряжения,подключаемый к выводам интегральной схеMbi 6 через измеритель 4, для задания измерительного напряжения. Триггер 5 блокирует выход измерителя 4 через схему И 16 и открывает элемент И 1 по одному входу. При этом на другой вход элемента И 14 подается сигнал с коммутационной планки 10. По этому сигналу разрешается подача напряжения с блока 12 питающего напряжения через электронный ключ 8 на подложку ИС 6. Подача напряжения с блока питающего напряжения 12 на ИС 6 через электронный ключ 8 для стока заряда осуществляется только во взведенном состоянии триггера 5, который сбрасывается сдвиговым регистром 3, задающим временную диаграмму его работы. При переходе к измерению входного тока утечки по новому выводу ИС 6 происходит вначале взведение триггера 5 через элемент ИЛИ 13 от измерителя k, что приводит кподаче напряжения от блока 12 на подложку И С и ускоряет сток паразитных зарядов с ИС 6, а следовательно ускоряет установление измеряемого тока утечки по выводу ИС 6. Затем триггер 5 сбрасывается сигналом с сдвигового регистра 3, при этом открываются элементы И 15 и И 16, снимается напряжение с лодложки ИС б и (1роисходит замер тока утечки измерителем k в устано-вившемся режиме, т.е. при установочном значении тока утечки. Ключ 9 обеспечивает подключение вывода подложки ИС 6 к измерителю в момент времени, определяемый коммутацией на планке 10, для измерения тока утечки по этому выводу. , Сигнал о годности ИС 6 с измерите ля поступает через элементы И 16, ИЛИ 13 на входы сдвиговых регистров и 3. При этом сдвиговый регистр 3 приходит в исходное состояние, в сдвиговом регистре 2 происходит сдви единицы на один разряд, а устройство переходит к измерению то,ка утечки к следущему выводу ИС 6. Сдвиг единицы в сдвиговом регистре 2 происходит до тех пор, пока не будут произведены измерения по всем выводам ИС 6, т.е. будет зафиксирова на годность ИС 6 сигналом с выхода старшего разряда сдвиговогорегистра 2 на шину Годен- 19. В случае негодности ИС 6 по какому-либо ее выводу сигнал с выхода измерителя на сброс регистра 3 не вырабатывается. При этом сдвиговый регистр 3 сохраняет состояние с единицей в старшем разряде, использованной для сбро са триггера 5. Сигнал с выхода старшего разряда сдвигового регистра 3 блокирует работу генератора 1 тактовых импульсов и фиксирует признак бр КЗ ИС 6 на шине Брак 20. Таким образом, применение предлагаемого устройства позволяет активно управлять процессом контроля токов утечки интегральных схем, а не только фиксировать появление сигнала год ности в заданных пределах времени. Обеспечение ускоренного стока парази ных зарядов из испытуемой интегральной схемы позволяет повысить производительность контроля интегральных схем в 2-3 раза. Формула изобретения Устройство для параметрического контроля интегральных схем, содержащее триггер, генератор тактовых импульсов, элемент ИЛИ, первый, второй и третий элементы И, и первый сдвиговый регистр, соединенный первыми выходами с входами коммутационной планки и со входами коммутатора, первые выходы которого соединены с первыми выходами устройства, второй Выход коммутатора соединен с первым входом измерителя, первые выходы коммутационной планки соединены с входами регистра, выходы которого соединены с входами программируемого блока питающего напряжения, выход которого соединен со вторым входом измерителя, отличающееся тем, что, с целью повышения производительности контроля, в него введены второй сдвиговый регистр, первый и второй электронные ключи, блок питающего напряжения, шина Брак, шина Пуск, шина Годен, причем второй вход устройства соединен с выходами первого и второго электронных ключей, первый вход первого электронного ключа соединен с выходом блока питающего напряжения , второй вход первого электронного ключа соединен с выходом первого элемента И, первый вход которого соединен с вторым выходом коммутационной планки, третий выход которой соединен с первым входом второго элемента И, выход которого соединен с первым входом второго электронного ключа, второй вход которого соединен с третьим выходом коммутатора, выход измерителя соединен с первом входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с шиной Пуск и входом установки первого сдвигового регистра и сбросовым входом второго сдвигового регистра, тактовый вход которого соединен с выходом генератора тактовых импульсов, вход которого соединен с первым выходом второго сдвигового регистра и шиной Брак, выход элемента ИЛИ соединен

с тактовым входом первого сдвигового регистра, установочным входом второго сдвигового регистра и первым входом триггера, второй вход которого соединен с вторым выходом второго сдвигового регистра, первый выход триггера соединен с вторым входом первого элемента И, второй выход триггера соединен с вторыми входами второго и TpeTbefo элементов И, второй выход первого сдвигового регистf3

ра соединен с шиной Годен, второй выход генератора тактовых импульсов соединен с третьим входом измерителя

Источники информации, принятые во внимание при экспертизе

1; Авторское свидетельство СССР № , кл. Q 01 R 31/28, 1979.

11

17

Авторы

Даты

1982-12-30—Публикация

1981-04-15—Подача