Изобретение относится к вычислительной технике, в частности к автоматизированным системам контроля, и может быть использовано при контроле логических блоков, нанример, больших интегральных схем.

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля блоков регулярной логики, а также повышения информативности контроля.

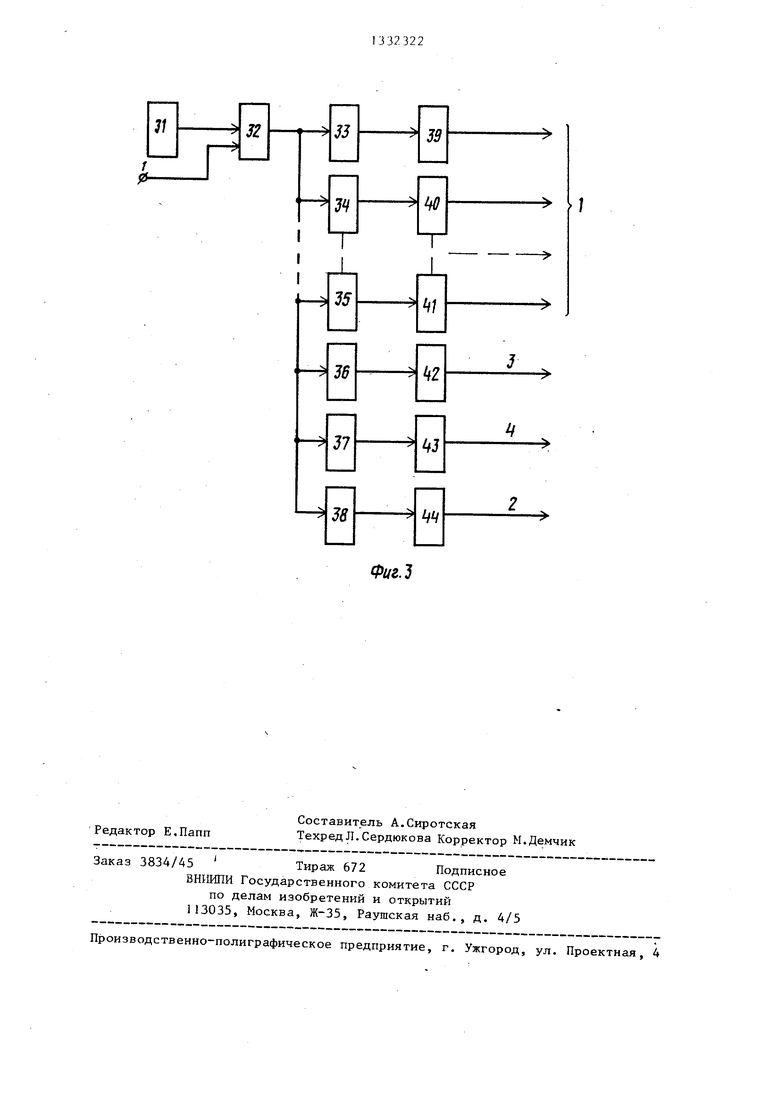

На фиг.1 изображена схема устройства; на фиг.2 - схема блока управления; на фиг.З - блок синхронизации.

Устройство содержит блок 1 синхронизации, блок 2 потенциального согласования, генератор 3 тестов, блок 4 управления, блок 5 сравнения, мультиплексор 6, усилитель 7 выходного отклика., сумматор 8 по модулю два и регистр 9 сдвига, образующие сигнатур ,ный анализатор, коммутатор 10, вход

счетчика 20 в нулевое состояние фор- 15 мирователь 22 импульсов осуществляет вычитание 1 из счетчика 26, при этом через элемент ИЛИ 30 происходит восстановление информации в счетчике 20 адресов. Сигналы с выхода контролируемого блока 4 поступают на усилитель 7, обеспечивающий согласовани его выходных уровней с логическими уровнями устройства, и затем на инфо мационный вход мультиплексора 6 и, в

|11 пуска устройства, вход- 12 и выход

.3 устройства. На фиГо изображен так-25 случае наличия управляющего сигнала

же контролируемый блок 14.на входе коммутатора 10 (формируемоБлок 4 управления (фиг.2) содержит триггеры 15 и 16 брака и пуска соответственно, формирователь 17 импульсов, элементы 18 задержки, элементы ИЛИ 19, счетчик, образованный собственно счетчиком 20 и дешифратором 21 нуля, формирователи 22 и 23 импульсов, элемент ИЛИ 24, формирова

тель 25 импульсов, счетчик, образован-35 триггере J5 (фиг.2) и через ный счетчиком 26 и депшфратором 27 нуля, элемент И 28, элемент 29 задержки, элемент ИЛИ 30.

Блок синхронизации содержит генератор 31 импульсов, элемент И 32, 40 элементы 33-38 задержки, формирователи 39-44 импульсов.

Устройство работает следующим образом.

По сигналу, поступающему на вход 45 11, в блоке 4 управления формирователь 17 (фиг.2) осуществляет сброс

го элементом И 28 и элементом 29 задержки блока 4 управления), на вход блока 5 сравнения, на второй 3Q вход которого поступает ожидаемая ин формация из генератора 3. Результат сравнения фиксируется блоком 4 управления, который, в случае несовпадения КОДОВ-, фиксирует состояние

элемент ИЛИ 19 сбрасывает триггер 16, что приводит к прерыванию контро ля .

Адрес канала мультиплексора 6 фор мируется счетчиком 26 в блоке 4 упра ления. Информация с выхода мультипле сора 6 поступает на вход регистра 9 через сумматор 8 по модулю два. Сдви информации в .-регистре 9 осуществляет ся импульсами., поступающими с . блока i синхронизации. После того, как из генератора 3 поступит вся тестовая информация, элемент И 28 (фиг.2) фор мирует сигнал совпадения нулевого состояния счетчиков 20 и 26 (с помощью дешифратора 21 и 27). При этом элемент ИЛИ 19 сбрасывает триггер 6, останавливающий работу блока 1 синхронизации. Одновременно элемент 29 задержки выдает на выход блока 4 управления стробирующий сигнал, коммутирующий выходы регистра 9 сдвига через коммутатор 10 на вход блока 5 сравнения. Одновременно вырабатываеттриггера 15 и установку триггера 16. Одновременно происходит запись числа состояний в каждом адресе, числа разрядов тестового слова в счетчики 20 и 26 соответственно. Выход триггера 16 запускает блок 1 синхронизации, разрешая прохождение импульсов генератора 31 (фиг.З) на элементы 33-38 задержки и формирователи импульсов , обеспечивающих необходимую временную диаграмму контроля,.тактовые импульсы и сигналы управления.

необходимые для работы контролируемого блока 14 и передаваемые на него через блок 2 согласования уровней напряжения. Импульсы, ггоступающие из блока 1 синхронизации на синхро- вход генератора 3 тестов, обеспечивают его своевременное переключение. При этом блок 4 управления вырабатывает также стробы в блок 5 сравнения через элемент 18 задержки (фиг,2), формирователь 23 импульсов . и элемент lUiPi 24. После установки

счетчика 20 в нулевое состояние фор- 5 мирователь 22 импульсов осуществляет вычитание 1 из счетчика 26, при этом через элемент ИЛИ 30 происходит восстановление информации в счетчике 20 адресов. Сигналы с выхода контролируемого блока 4 поступают на усилитель 7, обеспечивающий согласование его выходных уровней с логическими уровнями устройства, и затем на информационный вход мультиплексора 6 и, в

X

0

го элементом И 28 и элементом 29 задержки блока 4 управления), на вход блока 5 сравнения, на второй 3Q вход которого поступает ожидаемая информация из генератора 3. Результат сравнения фиксируется блоком 4 управления, который, в случае несовпадения КОДОВ-, фиксирует состояние

триггере J5 (фиг.2) и через

элемент ИЛИ 19 сбрасывает триггер 16, что приводит к прерыванию контроля .

0

5

0

5

Адрес канала мультиплексора 6 формируется счетчиком 26 в блоке 4 управления. Информация с выхода мультиплексора 6 поступает на вход регистра 9 через сумматор 8 по модулю два. Сдвиг информации в .-регистре 9 осуществляется импульсами., поступающими с . блока i синхронизации. После того, как из генератора 3 поступит вся тестовая информация, элемент И 28 (фиг.2) формирует сигнал совпадения нулевого состояния счетчиков 20 и 26 (с помощью дешифратора 21 и 27). При этом элемент ИЛИ 19 сбрасывает триггер 6, останавливающий работу блока 1 синхронизации. Одновременно элемент 29 задержки выдает на выход блока 4 управления стробирующий сигнал, коммутирующий выходы регистра 9 сдвига через коммутатор 10 на вход блока 5 сравнения. Одновременно вырабатывает313

ся стробирующий сигнал в блок 5 сравнения через формирователь 25 и элемент ИЛИ 24 (фиг.2). Результат сравнения фиксируется триггером 15.

Применение предлагаемого устройства позволяет использовать -для контроля блоков сокращенные тесты с учетом внутренних логических связей проверямого блока Б отличие от полного пе- ребора входных воздействий. Кроме того, устройство позволяет производить совмещенный контроль с помощью сдвигового регистра и с помощью по- тактового сравнения выходной информа ции с ожидаемой по наиболее важным выходам блока. Так, например, обычно при использовании устройств для контроля постоянных запоминающих уст- . ройств (ПЗУ), заключение о браке ПЗУ можно сделать только после перебора всех его адресов, тогда как при использовании этого устройства брак ПЗ может быть выявлен на первых тактах контроля при отсутствии на его выхо- де какого-либо из служебных сигналов (например, Ответ, Память). ,1 Формула изобретения

Устройство для контроля логических блоков, содержащее коммутатор, мультиплексор, генератор тестов, блок сравнения и блок управления, содержащий триггер пуска, причем выход поля эталонного отклика генератора тестов соединен с первым информационным входом блока сравнения, о т л и - чающее.ся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля блоков регулярной логики, а также повышения информативности контроля, устройство содержит блок потенциального согласования, усилитель выходного отклика, сигнату)ный анализатор и блок синхронизации, а блок управления содержит первый и второй счетчики, два элемента задержки, четыре формирователя импульсов, элемент И, три элемента ИЛИ и триггер брака, причем первый выход .блока синхронизации соединен с первым информационным входом блока потенциального согласования, выход которого является выходом .устройства для подключения к вхо- дам -.контролируемого логического блока, вход усилителя выходного отклика является входом устройства для подключения к выходу контролируемого логического блока, выход усилителя выходного отклика соединен с информационным входом мультиплексора и первым информационным входом коммутатора, выход которого соединен с вторым информационным входом блока сравнения, выход Неровно которого соединен с единичным входом триггера брака, выход которого является выходом признака сбоя устройства и соединен с первым входом первого элемента liJlH, выход которого соединен с нулевым вхо дом триггера пуска выход которого соединен с входом блокировки блока синхронизации, второй выход которого соединен с входом синхронизации генератора тестов, выход поля тестов которого соединен с вторым информационным входом 6jiOKa потенциального согласования, третий выход блока синхронизации соединен с синхровходом сигнатурного анализатора, выход которого соединен с вторым информационным входом коммутатора, синхровход которого соединен с выходом первого элемента задержки и через первый фор мирователь импульсов соединен с первым входом второго элемента ИЛИ, выход которого соединен с синхровходом блока сравнения, четвертый выход блока синхронизации соединен с входом управления вычитанием первого счетчика и через второй элемент задержки и второй формирователь импульсов - с вторым входом второго элемента ИЛИ, выход нулевого состояния первого счетчика соединен с первыми входами третьего элемента ИЛИ и элемента И и через третий формирователь импульсов соединен с входом управления вычитанием второго счет;- чика, выход нулевого состояния которого соединен с вторым входом элемента И, выход которого соединен с входом первого элемента задержки и вторым входом первого элемента ИЛИ, информационный вход сигнатурного анализатора соединен с выходом мультплексора, адресные входы которого соединены с разрядными выходами второго счетчика, вход пуска устройства соединен через четвертый формирователь импульсов с входами сброса триггера брака и установки второго счетчика, с единичным входом триггера пуска и вторым входом третьего элемента ИЛИ, выход которого соединен с вкодоь установки первого счетчика.

51332322 .6

информационные входы которого подклю- ния числа разрядов тестовог-о слова

чены к шине задания числа состояний в каждом разряде теста контролируемого логического блока, к шине задаконтролируемого логическо1 о блока подключены информационные входы вто рого, счетчика.

контролируемого логическо1 о блока подключены информационные входы второго, счетчика.

Редактор Е.Папп

Составитель А,Сиротская

Техред Л. Сердюкова Корректор М.Демчик

Заказ 3834/45 Тираж 672 Подписное ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля больших интегральных схем памяти | 1984 |

|

SU1179375A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОЛИЧЕСТВЕННОГО | 0 |

|

SU217729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для автоматического контроля блоков | 1984 |

|

SU1179348A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1986-04-07—Подача