1

Изобретение относится к вычислительной технике и может быть применено в автоматизированных системах контроля параметров интегральных схем.

Известно устройство для параметрическрго контроля интегральных схем, содержащее генератор импульсов, счетчик импульсов, дешифратор состояний счетчика, проверяемый и эталонный блоки, контролируемые выводы которых соединены с входами многоканальных элементов несовпадения импульсов 1. Но это устройство сложно.

Наиболее близким к изобретению по технической сущности является устройство для параметрического контроля интегральных схем, содержащее коммутационную матрицу, входы которой соответственно соединены с входными и выходными зажимами исследуемой интегральной схемы, с выходами программируемого источника питания и дешифратора, входы которого подключены, к выходу счетчика выводов, подключенного счетным входом к выходу элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а второй - с выходом триггера брака, соединенного через элемент ИЛИ с вйходом элементов сравнения, цифровой измерительный прибор, один из входов которого соединен с выходом коммутационной матрицы, другой

вход - с выходом элемента И, а выходы - с первыми входами элементов сравнения и входом генератора тактовых импульсов, источник питания 2. Однако такое устройство также сложно.

Цель изобретения - упрощение устройства. Достигается это тем, что в известное устройство, содержащее коммутационную матрицу, входы которой соединены с входными и выходными зажимами исследуемой интегральной схемы, с выходами программируемого источника питания и дешифратора, вход которого подключен к выходу счетчика выводов, подключенного счетным входом к выходу элейента И, первый вход которого соединен с выходом генератора тактовых импулбсов, а второй - с выходом триггера брака, соединенного через элемент ИЛИ с выходами элементов сравнения, цифровой измерительный прибор, один из входов которого соединен С вътходбм коммутационной матрицы, другой вход - с выходом элемента И, а выходы - с первыми входами элементов сравнения и входом генератора тактовых импульсов, и источник питания, введены элементы И, панель коммутации проверяемых номеров выводов, панель коммутации управления Црограммируемым источникомпитания и панели коммутации допустимых значений проверяемого параметра. При этом первые группы контактов панели коммутацип проверяемых номеров выводов и донустимых значений проверяемого параметра соединены с выходом источника питания, вторые группы контактов панели коммутации проверяемых номеров выводов - с первыми входами элементов И, вторые входы которых связаны с выходами дешифратора, а выходы - с первой группой контактов панели коммутации управления программируемым источником питания, вторая группа контактов которой подключена к программируемому источнику питания и к вторым входам элементов сравнения. Третьи входы элементов сравнения йбдсйёдинены к вторым группам контактов панелей коммутации допустимых значений Проверяемого параметра.

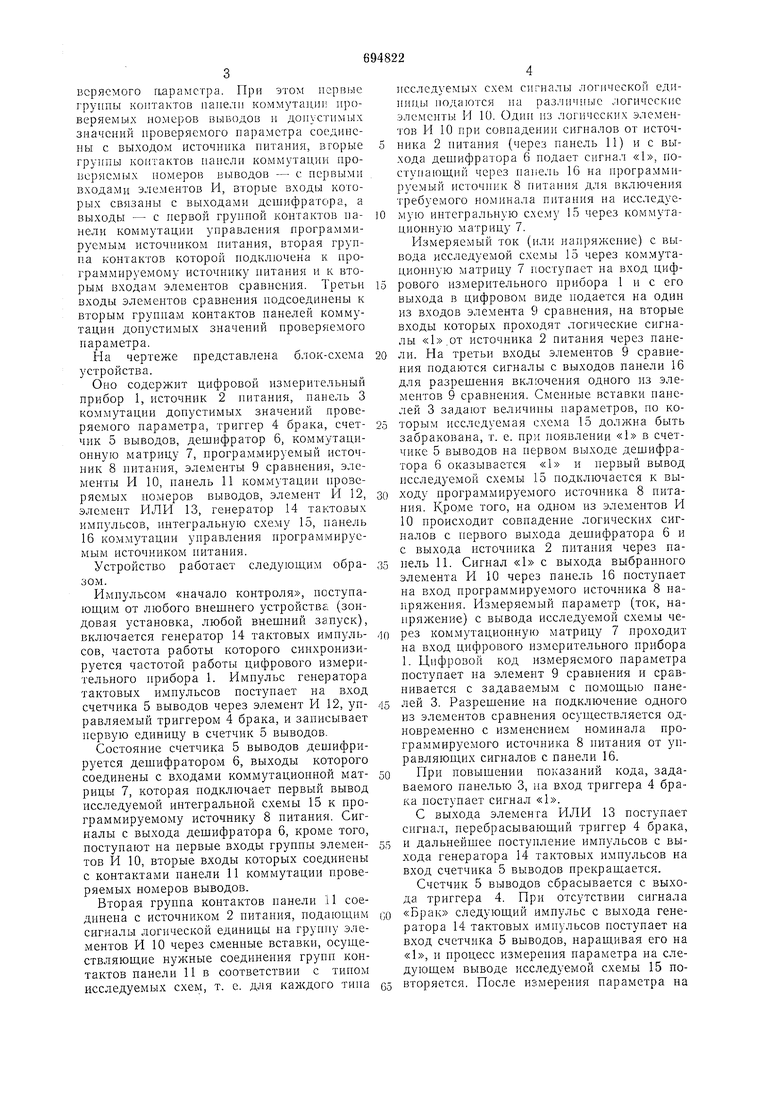

На чертеже представлена блок-схема устройства.

Оно содержит цифровой измерительный прибор 1, источник 2 питания, панель 3 коммутации допустимых значений проверяемого параметра, триггер 4 брака, счетчик 5 выводов, дешифратор 6, коммутационную матрицу 7, программируемый источник 8 питания, элементы 9 сравнения, элементы И 10, панель 11 коммутации проверяемых номеров выводов, элемент И 12, элемент ИЛИ 13, генератор 14 тактовых импульсов, интегральную схему 15, панель 16 коммутации управления программируемым источником питания.

Устройство работает следующим образом.

Импульсом «начало контроля, поступающим от любого внешнего устройства (зондовая установка, любой внешний запуск), включается генератор 14 тактовых импульсов, частота работы , которого синхронизируется частотой работы цифрового измерительного прибора 1. Импульс генератора тактовых импульсов поступает на ЁХОД счетчика 5 выводов через элемент И 12, управляемый триггером 4 брака, и записывает первую единицу в счетчик 5 выводов.

Состояние счетчика 5 выводов дешифрируется дешифратором 6, выходы которого соединень с входами коммутационной матрицы 7, которая подключает первый вывод исследуемой интегральной схемы Г5 к программируемому источнику 8 питания. Сигналы с выхода дешифратора 6, кроме того, поступают на первые входы группы элементов И 10, вторые входы которых соединены с контактами панели 11 коммутации проверяемых номеров выводов.

Вторая группа контактов панели 11 соединена с источником 2 питания, подающим сигналы логической единицы на группу элементов И 10 через сменные вставки, осуществляющие нужные соединения групп контактов панели 11 в соответствии с типом исследуемых схем, т. е. для каждого типа

исследуемых схем сигналы логической единицы подаются на различные логические элементы И 10. Один из логических элементов И 10 при совпадении сигналов от источника 2 питания (через панель 11) и с выхода дешифратора 6 подает сигнал «1, поступающий через панель 16 на программируемый источник 8 питания для включения требуемого номинала питания на исследуемую интегральную схему 15 через коммутационную матрицу 7.

Измеряемый ток (или напряжение) с вывода исследуемой схемы 15 через коммутационную матрицу 7 поступает на вход цифрового измерительного прибора 1 и с его выхода в цифровом виде подается на один из входов элемента 9 сравнения, на вторые входы которых проходят логические сигналы источника 2 питания через панели. На третьи входы элементов 9 сравнения подаются сигналы с выходов панели 16 для разрешения включения одного из элементов 9 сравнения. Сменные вставки панелей 3 задают величины параметров, по которым исследуемая схема 15 должна быть забракована, т. е. при появлении «1 в счетчике 5 выводов на первом выходе дешифратора 6 оказывается «1 и первый вывод исследуемой схемы 15 подключается к выходу программируемого источника 8 питания. Кро.ме того, на одном из элементов И 10 происходит совпадение логических сигналов с первого выхода дешифратора 6 и с выхода источника 2 питания через панель 11. Сигнал «1 с выхода выбранного элемента И 10 через панель 16 поступает на вход программируемого Источника 8 напряжения. Измеряемый параметр (ток, напряжение) с вывода исследуемой схемы через коммутационную матрицу 7 проходит на вход цифрового измерительного прибора 1. Цифровой код измеряемого параметра поступает на элемент 9 сравнения и сравнивается с задаваемым с помощью панелей 3. Разрешение на подключение одного из элементов сравнения осуществляется одновременно с изменением номинала программируемого источника 8 питания от управляющих сигналов с панели 16.

При повышении показаний кода, задаваемого панелью 3, на вход триггера 4 брака поступаёт сигнал «1.

С выхода элемента ИЛИ 13 поступает сигнал, перебрасывающий триггер 4 брака,

и дальнейшее поступление имЪульсов с выхода генератора 14 тактовых импульсов на входсчетчика 5 выводов прекращается.

Счетчик 5 выводов сбрасывается с выхода триггера 4. При отсутствии сигнала

«Брак следующий импульс с выхода генератора 14 тактовых импульсов поступает на вход счетчика 5 выводов, наращивая его на «1, н процесс измерения параметра на следующем выводе исследуемой схемы 15 повторяется. После измерения параметра на последнем выводе схемы 15 сигналом с дешифратора 6 сбрасывается счетчик 5 выводов и отключается генератор 14 тактовых имнульсов. Использование изобретения повышает производительность системы контроля интегральных схем, так как статические испытания этих схем .проводятся без участия цифровой вычислительной машины, которая в это время обрабатывает результаты функционального контроля на другом измерительном посту. Ожидаемое увеличение производительности системы составляет 15%. Формула изобретения Устройство параметрического контроля интегральных схем, содержаш,ее коммутационную матрицу, соединенную с входными и выходными зажимами исследуемой интегральной схемы, с выходами программируемого источника питания и дешифратора, входы которого подключены к счетчику выводов, подключенному счетным входом к выходу элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а второй - с выходом триггера брака, подсоединенного через элемент ИЛИ к выходам элементов сравнения, цифровой измерительный прибор, соединенный с коммутационной матрицей, генератором тактовых импульсов, элементом И и первыми входами элементов сравнения, и источник питания, отличающееся тем, что, с целью упрощения устройства, в него введены элементы И, панель коммутации проверяемых номеров выводов, панель коммутации управления программируемым источником питания и панели коммутации допустимых значений проверяемого параметра, при этом первые группы контактов панели коммутации проверяемых номеров выводов и допустимых значений проверяемого параметра соединены с выходом источника питания, вторые группы контактов панели коммутации проверяемых номеров выводов соединены с первыми входами элементов И, вторые входы которых соединены с выходами дешифратора, а выходы - с первой группой контактов панели коммутации управления программируемым источником питания, вторая группа контактов которой подключена к программируемому источнику питания и к вторым входам элементов сравнения, третьи входы элементов сравнения подсоединены к вторым группам контактов панелей коммутации допустимых значений проверяемого параметра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 238236, кл. G 06F 15/46, 1970. 2.Авторское свидетельство СССР № 393748, кл. G 01R 31/28, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство параметрического контроля интегральных схем | 1986 |

|

SU1308956A1 |

| Устройство для параметрического контроля интегральных схем | 1981 |

|

SU985755A1 |

| Классификатор линейных интегральных схем | 1974 |

|

SU528520A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU748422A1 |

| Устройство для контроля параметров | 1986 |

|

SU1403074A1 |

Авторы

Даты

1979-10-30—Публикация

1976-12-10—Подача