(54) УСТРОЙСТВО ДЛЯ ПОСЛЕДОВАТЕЛЬНОГО ВЫДЕЛЕНИЯ ЕДИНИЦ ИЗ П.-РАЗРЯДНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Процессор | 1981 |

|

SU962964A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в схемах приоритета, в системах аппаратного контроля средств вычислительной техники, в ассоциативных запоминающих устройствах.

Известно устройство для последовательного выделения единиц из заданного п-разрядного двоичного кода, содержащее два последовательно соединенных регистра блока выделения единиц, блок исключения выделения единиц, преобразователь номера выделенной единицы в двоичный код и дещифратор двоичного кода номера разряда выделенной единицы 1.

Недостатками устройства являются его сложность, обусловленная применением шифратора, дешифратора, а также большое количество информационных связей, резко возрастающих с увеличением разрядности исходного кода. Сложность устройства обусловливает и его пониженную наде.жность.

Известно устройство для последовательности выделения единиц из заданного п-разрядного двоичного кода, содержащее основной, вспомогательный и дополнительный регистры, выполненные на триггерах, блок выделения единиц, выполненный в. виде однотипных ячеек, каждая из которых состоит из элемента ИЛИ и двух элементов И 2.

Недостатками данного устройства являются сложный режим его использования, обусловленный тем, что для выделения каждой единицы необходим повторный цикл обращения к запоминающему устройству, хранящему исходный код, и повторная подача исходного кода для выделения второй , третьей и т. д. единиц (это одновременно приводит к снижению быстродействия устройст0ва), отсутствие возможности определения (без дополнительных внешних схем) является ли выделенная единица последней, узкое функциональное назначение устройства и невозможность его использования в других задачах вычислительной техники кроме вы5деления единиц из п-разрядного кода.

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения функций генератора «бегущей единицы, сдвигателя и памяти.

Поставленная цель достигается тем, что в устройстве для последовательного выделения единиц из п-разрядного кода, содержащем п разрядов, причем каждый разряд устройства содержит основной и вспомогательный триггеры, первый и второй элементы И, элемент ИЛИ, введены четвертый, пятый, шестой, седьмой и восьмой элементы И, причем в каждом разряде первый вход первого элемента И подключен к первой входной шине устройства, первый вход второго элемента И подключен ко второй входной шине устройства, выходы первого и второго элементов И соединены соответственно с первым и вторым входами основного триггера, инверсный выход основного триггера соединен с первым входом третьего элемента И, а прямой выход - с первым входом четвертого элемента И, второй вход четвертого элемента И подключен к третьей входной, шине устройства, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первыми входа-, ми пятого и шестого элементов И, вторые входы которых подключены соответственно к четвертой и пятой входным шинам устройства, выход пятого- и шестого элементов И соединены соответственно с первым и вторым входами вспомогательного триггера, прямой выход которого соединен с первыми входами седьмого и восьмого элементов И, вторые входы которых подключены соответственно кшестой и седьмой входным шинам устройства, выход седьмого элемента И соединен со вторыми входами первого и второго элементов И, выход восьмого элемента И соединен с соответствующим разрядным выходом устройства, второй вход третьего элемента И первого разряда устройства Подключен к первому входу устройства, а второй вход третьего элемента И последующего разряда соединен с выходом третьего элемента И предыдущего разряда, третий вход элемента ИЛИ первого разряда устройства подключен ко второму входу устройства, а третий вход элемента ИЛИ последующего разряда соединены с выходом седьмого элемента И предыдущего разряда, выход седьмого элемента И последнего разряда устройства соединен с первым выходом устройства, второй выход которого соединен с выходом третьего элемента И последнего разряда устройства, первый и второй входы основного триггера каждого разряда соединены соответственно с первым и вторым установочными входами устройства, а первый и второй входы вспомогательного триггера каждого разряда соединены соответственно с третьим и четвертым установочными входами устройства.

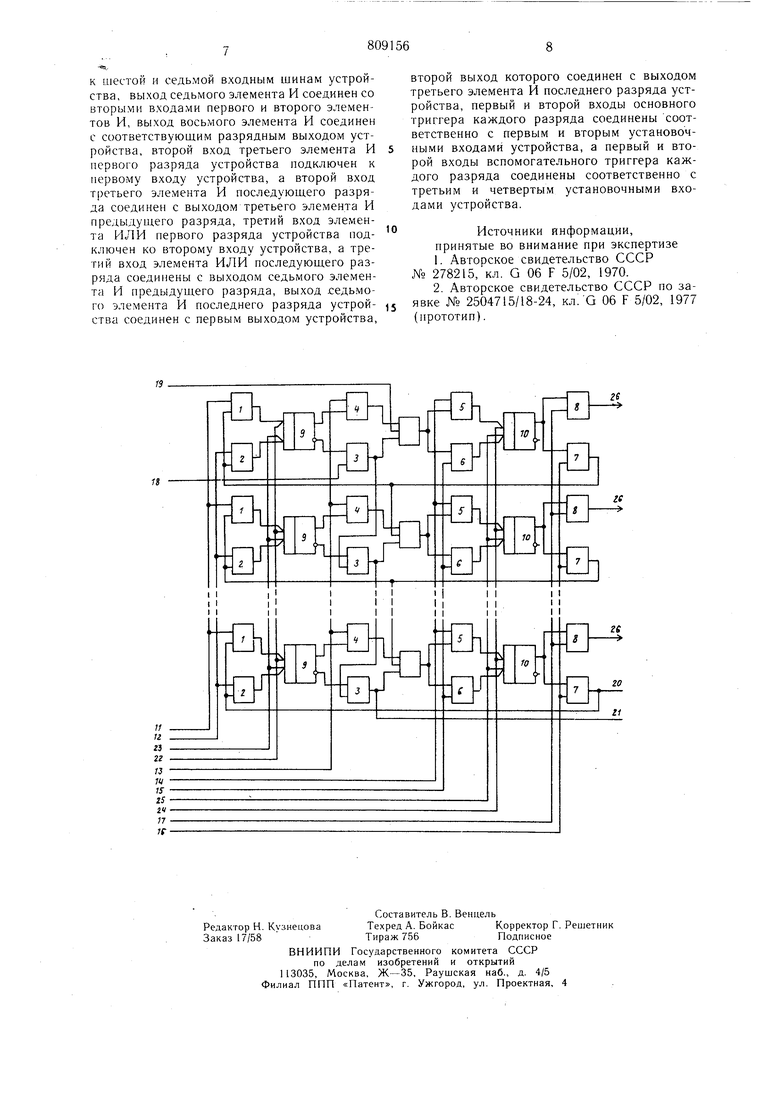

На чертеже представлена функциональная схема устройства для последовательного выделения единиц из п-разрядного кода. Устройство содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И 1-8, триггеры 9 основного регистра, триггеры 10 вспомогательного регистра, первую, вторую, третью, четвертую, пятую, шестую и седьмую входные

шины 11 -17 устройства, первый и второй входы 18 и 19 устройства, первый и второй выходы 20 и 21 устройства, первый, второй, третий и четвертый установочные входы 2225 устройства, разрядные выходы 26 устройства.

Устройство работает следующим образом.

Первым тактом по информационным шинам 11 и 12 в основной регистр производится загшсь л-разрядного двоичного При использовании парафазного информационного входа предварительная установка нулевого состояния основного регистра не производится, при этом необходимость во входе 23 отсутствует. Одновре.менно с первым тактом записи кода производится установка вспомогательного регистра в единичное состояние по щине 24.

Вторым тактом на щину 15 и вход 18 подается сигнал разрешения, который проходит последовательно по цепи всех третьих элементов И до первой единицы в основном регистре, причем выходной сигнал третьих элементов И через элементы ИЛИ и пятые элементы И установит соответствующие триггеры вспомогательного регистра в нулевое состояние.

Пример. Пусть все устройство имеет размерность одного байта (восемь разрядов) и подается код 00010110 (будет читать его 0 слева направо). Одновременно с установкой этого кода в основном регистре, в вспомогательном регистре будет код 11111111. После подачи сигналов на входы 15 и 18 вспомогательного регистра станет 00011111. Третьим тактом с подачей сигнала на шины 12 и 16 на вспомогательном регистре фиксируется положение первойщ единицы 00010000 и одновременно она «гасится на основном регистре, т. е. остается код 00000110, подготовленный для выделения последующей 0 единицы.

При заданных разрядах кода последовательно генерируется сигнал «1 на первом входе, затем на втором и т. д. до п, затем последовательность повторяется, начиная с первого входа и т. д.

Указанная функция реализуется предлагаемым устройством, если внещней цепью соединить выход 20 со входом 22. 50 Перед началом работы в рассматриваемом режиме подается сигнал установки единичного состояния в основном регистре-или записывается код из одних единиц в основной регистр по параллельны.м информационным входам.

5 Зате.м осуществляется режим выделения единицы. На каждом третьем такте на выходе 20 будет появляться «очередная единица. После выделения последней единицы по выходу 20 автоматически восстановится состояние всех единиц в основном регистре и работа повторится. 3. Функция регистра сдвига вправо (или влево). По первому такту производится прием исходного кода в основной регистр и одновременно сигналом по входу 25 производится установка вспомогательного регистра в нулевое состояние. Вторым тактом с подачей сигналов на шины 13 и 14 производится передача кода из основного в вспомогательный регистр. Третьим тактом с подачей сигналов на шины 14 и 16 производится сдвиг кода в вспомогательном регистре. Четвертым тактом с подачей сигнала по шинам 11 и 16 производится запись сдвинутого вправо на один разряд кода в основной регистр. Для устранения возможных гонок при операции сдвига на шины 14 и 16 подается сигнал длительностью не более времени четырех задержек в элементах И, ИЛИ. Сдвиг влево на устройстве возможен в том случае, если связь от седьмых элементов И на вход схемы ИЛИ произведена справа налево. 4.Функция памяти микропрограммного автомата. В микропрограммных автоматах -с различным принципом реализации комбинационных схем, например на программируемых логических матрицах, элементах И, ИЛИ, перестраиваемых средах и т. д. требуется для устранения гонок наличия памяти с простой функцией передачи п-разрядного кода из одного регистра в другой с разделением во времени операций приема кода в первый регистр и передачи кода во второй регистр по специальному такту. Указанная функция реализуется устройством следующим образом. После приема кода в основной регистр передача кода на вспомогательный регистр осуществляется при подаче сигнала одновременно на шины 13 и 14. Съем сигналов осуществляется по параллельным выходам 26 при подаче сигнала н.а шину 17. 5.Функция стековой памяти. Достигается объединение m устройств соединением .в единую шину|3 и во вторую шину 15. Разрядные выходы п-го устройства соединены с информационными входами 11 устройства. Получим стековую память на 2т чисел разрядности п. После подачи п-разрядного кода на вход первого устройства сдвиг во всем стеке из 2т регистров осуществляется за два такта. На первом такте осуществляется промежуточный сдвиг внутри каждого устройства при подаче сигнала на шину 13 и 14. На втором такте осуществляется перепись кодов из устройства 1 в устройство 2 из устройства 2 в устройство 3 и г. и. при подаче сигнала на входы 17. Снятие кода как и обычном стеке производится из его вершины, т. е. с т-го устройства. Заметим, что получившаяся стековая память обладает по сравнению с существуюшими типами стеков тем преимуществом, что одновременно позволяет производить вышеописанные функции над 2т-числами разрядностью п, т. е. по существу является специализированным параллельным процессором. Эффективность изобретения заключается в расширении функциональных возможностей устройства за счет выполнения функций генератора «бегущей единицы, функций регистра сдвига, функций памяти микропрограммного автомата и функции стековой памяти, а также увеличение быстродействия устройства в задаче последовательного выделения единиц из п-разрядного кода, так как при этом не требуется повторная подача исходного п-разрядного кода для выделения второй, третьей и т. д. единиц. Формула изобретения Устройство для последовательного выделения единиц из п-разрядного кода, содержащее п разрядов, причем каждый разряд устройства содержит основной и вспомогательный триггеры, первый и второй элементы И, элемент ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения функций генератора «бегущей единицы, сдвигателя и памяти, в него дополнительного введены четвертый, пятый, щестой, седьмой и восьмой элементы И, причем в каждом разряде первый вход первого элемента И подключен к первой входной шине устройства, первый вход второго элемента И подключен ко второй входной щине устройства, выходы первого и второго элементов И соединены соответственно с первым и вторым входами основного триггера, инверсный выход основного триггера соединен с первым входом третьего элемента И, прямой выход - с первым входом четвертого элемента И, второй вход чертвертого элемента И подключен к третьей входной щине устройства, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первыми входами ПЯТОГО и шестого элементов И, вторые входы которых подключены соответственно к четвертой и пятой входным шинам устройства, выход пятого и щестого элементов И соединены соответственно с первым и вторым в.ходами вспомогательного триггера, прямой выход которого соединен с первыми входами седьмого и восьмого элементов И, вторые входы которых подключены соответственно

к шестой и седьмой входным шинам устройства, выход седьмого элемента И соединен со вторыми входами первого и второго элементов И, выход восьмого элемента И соединен с соответствующим разрядным выходом устройства, второй вход третьего элемента И первого разряда устройства подключен к первому входу устройства, а второй вход третьего элемента И последуюш,его разряда соединен с выходом третьего элемента И предыдупд.его разряда, третий вход элемента ИЛИ первого разряда устройства подключен ко второму входу устройства, а третий вход элемента ИЛИ последующего разряда соединены с выходом седьмого элемента И предыдущего разряда, выход .седьмого элемента И последнего разряда устройства соединен с первым выходом устройства.

второй выход которого соединен с выходом третьего элемента И последнего разряда устройства, первый и второй входы основного триггера каждого разряда соединены соответственно с первым и вторым установочными входами устройства, а первый и второй входы вспомогательного триггера каждого разряда соединены соответственно с третьим и четвертым установочными входами устройства.

Источники информации, принятые во внимание при экспертизе

1Авторское свидетельство СССР № 278215, кл. G 06 F 5/02, 1970.

2Авторское свидетельство СССР по заявке № 2504715/18-24, кл.С 06 F 5/02, 1977 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-04-03—Подача