Изобретение относится к импульсной технике, предназначено для управления импульсным устройством, лазерными системами и может быть использовано в синхронизаторах, цифровых управляющих и вычислительных системах.

Цель изобретения - расширение функциональных возможностей за счет формирования как четных, так и нечетных частот относительно опорной частоты,

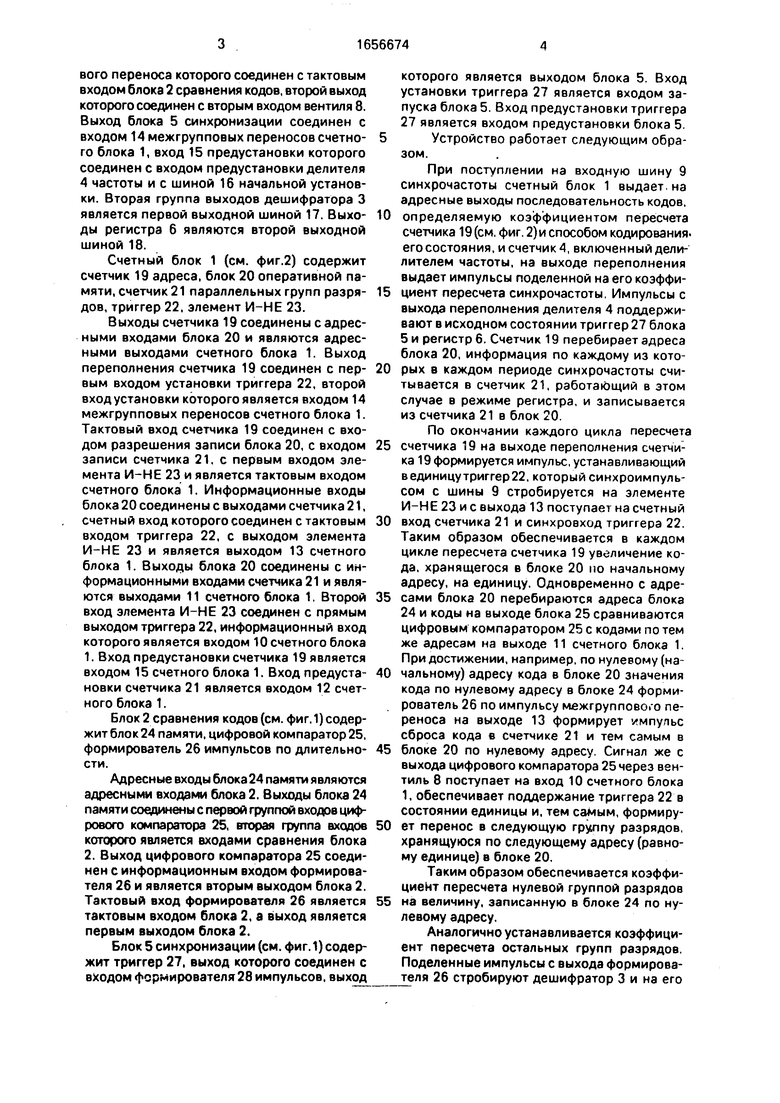

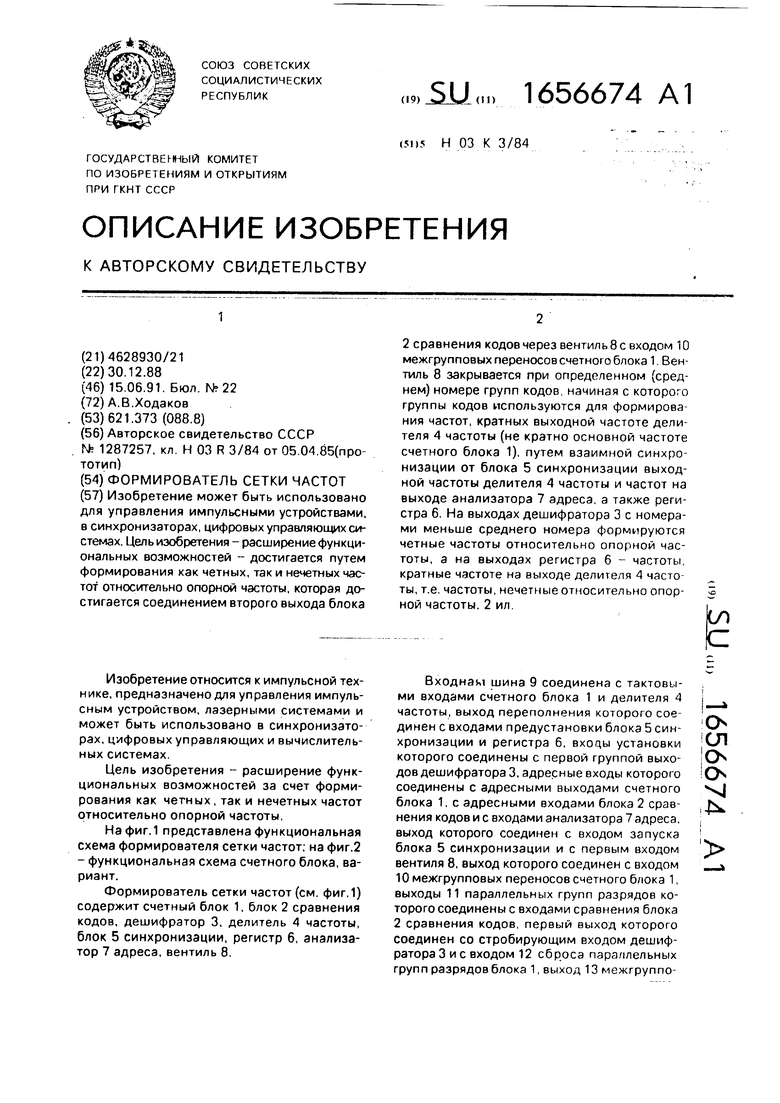

На фиг.1 представлена функциональная схема формирователя сетки частот: на фиг.2 - функциональная схема счетного блока, вариант.

Формирователь сетки частот (см. фиг.1) содержит счетный блок 1, блок 2 сравнения кодов, дешифратор 3, делитель 4 частоты, блок 5 синхронизации, регистр 6, анализатор 7 адреса, вентиль 8.

Входнам шина 9 соединена с тактовыми входами счетного блока 1 и делителя 4 частоты, выход переполнения которого соединен с входами предустановки блока 5 синхронизации и регистра 6, входы установки которого соединены с первой группой выходов дешифратора 3, адресные входы которого соединены с адресными выходами счетного блока 1, с адресными входами блока 2 сравнения кодов и с входами анализатора 7 адреса, выход которого соединен с входом запуска блока 5 синхронизации и с первым входом вентиля 8, выход которого соединен с входом 10 межгрупповых переносов счетного блока 1, выходы 11 параллельных групп разрядов которого соединены с входами сравнения блока 2 сравнения кодов, первый выход которого соединен со стробирующим входом дешиф- ратораЗ ис входом 12 сброса параллельных групп разрядов блока 1,выход 13 межгруппоО ;СЛ О О XI ,Ј. i

i

вого переноса которого соединен с тактовым входом блока 2 сравнения кодов, второй выход которого соединен с вторым входом вентиля 8. Выход блока 5 синхронизации соединен с входом 14 межгрупповых переносов счетного блока 1, вход 15 предустановки которого соединен с входом предустановки делителя 4 частоты и с шиной 16 начальной установки. Вторая группа выходов дешифратора 3 яЁляется первой выходной шиной 17. Выходы регистра 6 являются второй выходной шиной 18.

Счетный блок 1 (см. фиг.2) содержит счетчик 19 адреса, блок 20 оперативной памяти, счетчик 21 параллельных групп разрядов, триггер 22, элемент И-НЕ 23.

Выходы счетчика 19 соединены с адресными входами блока 20 и являются адресными выходами счетного блока 1. Выход переполнения счетчика 19 соединен с первым входом установки триггера 22, второй вход установки которого является входом 14 межгрупповых переносов счетного блока 1. Тактовый вход счетчика 19 соединен с входом разрешения записи блока 20, с входом записи счетчика 21, с первым входом элемента И-НЕ 23 и является тактовым входом счетного блока 1. Информационные входы блока 20 соединены с выходами счетчика 21, счетный вход которого соединен с тактовым входом триггера 22, с выходом элемента И-НЕ 23 и является выходом 13 счетного блока 1. Выходы блока 20 соединены с информационными входами счетчика 21 и являются выходами 11 счетного блока 1, Второй вход элемента И-НЕ 23 соединен с прямым выходом триггера 22, информационный вход которого является входом 10 счетного блока

1.Вход предустановки счетчика 19 является входом 15 счетного блока 1. Вход предустановки счетчика 21 является входом 12 счетного блока 1.

Блок 2 сравнения кодов (см. фиг. 1) содержит блок 24 памяти, цифровой компаратор 25, формирователь 26 импульсов по длительности.

Адресные входы блока24 памяти являются адресными входами блока 2. Выходы блока 24 памяти соединены с первой группой входов цифрового компаратора 25, вторая группа входов которого является входами сравнения блока

2.Выход цифрового компаратора 25 соединен с информационным входом формирователя 26 и является вторым выходом блока 2. Тактовый вход формирователя 26 является тактовым входом блока 2, а выход является первым выходом блока 2.

Блок 5 синхронизации (см. фиг. 1) содержит триггер 27. выход которого соединен с входом формирователя28 импульсов, выход

которого является выходом блока 5. Вход установки триггера 27 является входом запуска блока 5. Вход предустановки триггера 27 является входом предустановки блока 5.

Устройство работает следующим образом.

При поступлении на входную шину 9 синхрочастоты счетный блок 1 выдает, на адресные выходы последовательность кодов,

0 определяемую коэффициентом пересчета счетчика 19 (см. фиг. 2) и способом кодирования, его состояния, и счетчик 4, включенный дели- лителем частоты, на выходе переполнения выдает импульсы поделенной на его коэффи5 циент пересчета синхрочастоты, Импульсы с выхода переполнения делителя 4 поддерживают в исходном состоянии триггер 27 блока 5 и регистр 6. Счетчик 19 перебирает адреса блока 20, информация по каждому из кото0 рых в каждом периоде синхрочастоты считывается в счетчик 21, работающий в этом случае в режиме регистра, и записывается из счетчика 21 в блок 20.

По окончании каждого цикла пересчета

5 счетчика 19 на выходе переполнения счетчика 19 формируется импульс, устанавливающий вединицутриггер22, который синхроимпульсом с шины 9 стробируется на элементе И-НЕ 23 и с выхода 13 поступает на счетный

0 вход счетчика 21 и синхроаход триггера 22. Таким образом обеспечивается в каждом цикле пересчета счетчика 19 увеличение кода, хранящегося в блоке 20 но начальному адресу, на единицу. Одновременно с адре5 сами блока 20 перебираются адреса блока 24 и коды на выходе блока 25 сравниваются цифровым компаратором 25 с кодами по тем же адресам на выходе 11 счетного блока 1. При достижении, например, по нулевому (на0 чальному) адресу кода в блоке 20 значения кода по нулевому адресу в блоке 24 формирователь 26 по импульсу межгруппового переноса на выходе 13 формирует импульс сброса кода в счетчике 21 и тем самым в

5 блоке 20 по нулевому адресу. Сигнал же с выхода цифрового компаратора 25 через вентиль 8 поступает на вход 10 счетного блока 1, обеспечивает поддержание триггера 22 в состоянии единицы и, тем самым, формиру0 ет перенос в следующую грулпу разрядов, хранящуюся по следующему адресу (равному единице) в блоке 20.

Таким образом обеспечивается коэффициент пересчета нулевой группой разрядов

5 на величину, записанную в блоке 24 по нулевому адресу.

Аналогично устанавливается коэффициент пересчета остальных групп разрядов. Поделенные импульсы с выхода формирователя 26 стробируют дешифратор 3 и на его

выходах, определяемых кодом на адресных выходах счетного блока 1, формируют частоты, понижающиеся с увеличением номера выхода дешифратора 3 в число раз, записанное в блоке 24 по предыдущему адресу.

Выходные частоты на шине 17 кратны частоте на выходе переполнения счетчика 19 (см. фиг.2).

Анализатор 7 адреса, выполненный, например, в виде схемы И-НЕ, формирует по одному из адресов, например по седьмому, при коэффициенте пересчета счетчика 19, равном шестнадцати, отрицательный импульс, во-первых,запрещающий перенос в восьмую группу из седьмой по входу 10 счетного блока, во- вторых, устанавливающий в единицу триггер 27. Переброс триггера 27 из нуля в единицу вызывает формирование сигнала переноса в восьмую группу по входу 14 счетного блока 1. Такое добавление единицы в ёосьмую группу происходит только после поступления импульса с выхода делителя 4, частота которого определяется коэффициентом пересчета делителя 4, отличным от коэффициента пересчета счетчика 19 и выбира- емым большим коэффициентом пересчета этого счетчика. Импульсы с выхода переполнения делителя 4, поступая на общий вход предустановки триггеров регистра 6, изменяют состояние тех триггеров регист- ра 6, на которые до того поступали частоты, поделенные на коэффициенты, записанные в блоке 24 по адресам, начиная с восьмого по пятнадцатый. Таким образом, на выходной шине 18 формируются импульсы с частотами, определяемыми коэффициентом деления делителя 4 и кодами из блока 24 по старшим адресам.

По входной шине 16 делитель 1 г. смег- чик 19 Moryi быть сброшены т р одномо ментно засинхронизованы

Необходимо отметить, что в блоке 24 должны храниться уставки, значения кото рых на единицу меньше требурмого коэффи циента деления соответствующей груп. ы

Формула изобретения

Формирователь сетки частот содержа щий счетный блок, блок сравнения кодов дешифратор, адресные входы которого соединены с адресными выходами счетного блока и с адресными входами блока сравнения кодов, синхровход которого соединен с выходом межгрупповых переносов счетного блока, первый выход блока сравнения кодов соединен со стробирующим входом дешифратора и входом сброса параллельной группы разрядов счетного блока, выходы параллельных групп разрядов счетного блока соединены с входами сравнения блока сравнения кодов, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен делитель частоты, блок синхрони зации, анализатор адреса, вентиль и регистр, выход делителя частоты соединен с входами предустановки блока синхронизации и регистра, входы установки которого соединены с выходами дешифратора, выход блокз синхронизации соединен с входом межгрупповою переноса счетного блока, входы анализатора адреса соединены с выходами номеров параллельных групп разрядов счетного блока, а выход соеди нен с входом запуска блока синхронизации и с первым входом вентиля, второй вход которого соединен с вторым выходом блока сравнения а выход соединен с входом межгрупповых переносов счетного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования серии импульсов | 1987 |

|

SU1525873A1 |

| Устройство для контроля параметров объекта | 1983 |

|

SU1164670A1 |

| Устройство для измерения N временных интервалов | 1986 |

|

SU1465868A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Делитель частоты следования импульсов | 1983 |

|

SU1177907A1 |

Изобретение может быть использовано для управления импульсными устройствами, в синхронизаторах, цифровых управляющих системах. Цель изобретения - расширение функциональных возможностей - достигается путем формирования как четных, так и нечетных частот относительно опорной частоты, которая достигается соединением второго выхода блока 2 сравнения кодов через вентиль 8 с входом 10 межгрупповых переносов счетного блока 1 Вентиль 8 закрывается при определенном (среднем) номере групп кодов, начиная с которого группы кодов используются для формирования частот, кратных выходной частоте делителя 4 частоты (не кратно основной частоте счетного блока 1), путем взаимной синхронизации от блока 5 синхронизации выходной частоты делителя 4 частоты и частот на выходе анализатора 7 адреса, а также регистра 6. На выходах дешифратора 3 с номерами меньше среднего номера формируются четные частоты относительно опорной частоты, а на выходах регистра 6 - частоты. кратные частоте на выходе делителя 4 частоты, т.е. частоты, нечетные относительно опорной частоты.2 ил 00

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-15—Публикация

1988-12-30—Подача