подключены соответственно к входу разрешения обращения блока памяти ;результата, второму выходу адресно; го регистра и выходу дешифратора адipeca, первый и второй входы блока Элементов ИЛИ соединены соответст;венно с информационным входом устройства и первым входом блока приемо передатчиков адреса, второй выход и управляющий вход которого подключены соответственно к входу дешифратора адреса и второму выходу адресного регистра, первый и второй входы и выход четвертого элемента ИЛИ соединены соответственно с первым и вторым выходами адресного регистра и входом разрешения обращения блока памяти термов, адресный вход, вход чтения и вход записи которого подключены соответственно к адресному входу устройства, выходу первого одновибратора и выходу пятого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно первого элемента И и второго одновибратора, вход которого подключен к выходу второго элемента И, управляющий вход, второй информационHfctfi вход и выход блока приемо-передатчиков данных соединены соответственно с вторьм выходом адресного регистра, вькодом блока памяти результата и информационным входом блока памяти термов, выход, информационный вход, вход параллельной записи, вход приращения и счетный вход реверсивного счетчика функций подключены соответственно к информационному входу и выходу блока памяти функций, выходу первого одновибратора, информационному входу устройст ва и выходу ключа, управляющий вход и информационный вход которого соединены с выходами соответс1венно второго элемента И -и дифференцирующего элемента, вход которого подключен к выходу старшего разряда реверсивного счетчика термов, а вход чтения, вход записи, адресный вход и вход разрешения обращения блока памяти функций соединены соответственно с выходом первого одновибратора , выходом второго одновибратора , адресным входом устройства и вторым выходом адресного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

УСТРОЙСТВО ЛОГИЧЕСКОЙ ОБРАБОТКИ, содержащее адресный регистр, :дешифратор адреса, блок приемо-передатчиков адреса и.блок приемо-передатчиков данных, первый информационный вход которого соединен с информационным входом устройства, а информационные входы адресного регистра и блока приемо-передатчиков адреса подключены к адресному входу устройCTBi , отличающееся тем, что, с целью повышения производительности, оно содержит блок памяти термов, блок памяти функций, блок памяти результата, реверсивный счетчик термов, реверсивный счетчик функций, коммутатор, регистр результата, два одновибратора, дифференцирующий элемент, ключ, блок элементов ИЛИ, пять элементов ИЛИ и три элемента И, при .этом первый и -второй- входы первого элемента И соединены соответственно с первым выходом адресного регистра и входом упрагления режимом устройства, первый и второй входы и выход второго элемента И подключены соответственно к яторому выходу адресного регистра, входу управления режимом устройства и счетному входу реверсивного счетчика термов, вход приращения, вход параллельной за- . писи, информационный вход и информационный выход которого соединены соответственно с информационным входом устройства, выходом первого одновибратора, информационным выходом и информационным входом блока памяти термов, первый и второй входы и выход первого элемента ИЛИ подключены соответственно к выходу первого -1 одновибратора, входу управления режи мом устройства и входу чтения блока (Л памяти результата, вход записи, адресный вход, информационный вход и информационный выход которого соединены соответственно с выходом второго одновибратора, выходом блока элементов ИЛИ, выходом регистра результата и первым информационным входом коммутатора, второй информационньй вход, управляющий вход и выход коммутатора подключены соответственно к выходу младшего разряда реверсивного счетчика функций, информационному входу устройства и ; информационному входу регистра ре зультата, синхровход которого соединен с выходом первого одновибратора, выход, первый и второй входы третьего элемента И подключены соответственно к входу первого одновибратора, второму выходу адресного регистра и выходу второго элемента ИЛИ, входы которого соединены с информационным входом устройства, выход, первый и второй входы третьего элемента ИЛИ

Изобретение относится к цифровым вычислительным машинам и может быть использовано в управляющих микропроцессорных системах.

Известно устройство логической обработки, содержащее однобитовый процессор, запоминающее устройство, порт данных и устройства вводавьшода lj .

Известно также устройство логичес кой обработки, содержащее микропроцессор общего назначения, запоминающее устройство, устройства ввода-вывода и логический дешифратор 2J ,

Эти устройства предназначены для автоматического управления машинами и производственными процессами.

Недостатком указанных устройств является малое быстродействие при решении булевых уравнений.

Наиболее близким к предлагаемому является устройство логической обработки, содержащее процессор, устройства ввода-вьтода, запоминающее устройство, коммутатор, последовательнопараллельные преобразователи и детёктор неисправности. В известном устройстве производится циклический опрос входньвс каналов. Коммутатор по команде из процессора выборочно подключает группу входов к параллельно-последовательным преобразователям, которые осзгществляют упорядочение данных для проверки логический условий. В логические условия входят переменные, соответствующие опрашиваемым каналам з .

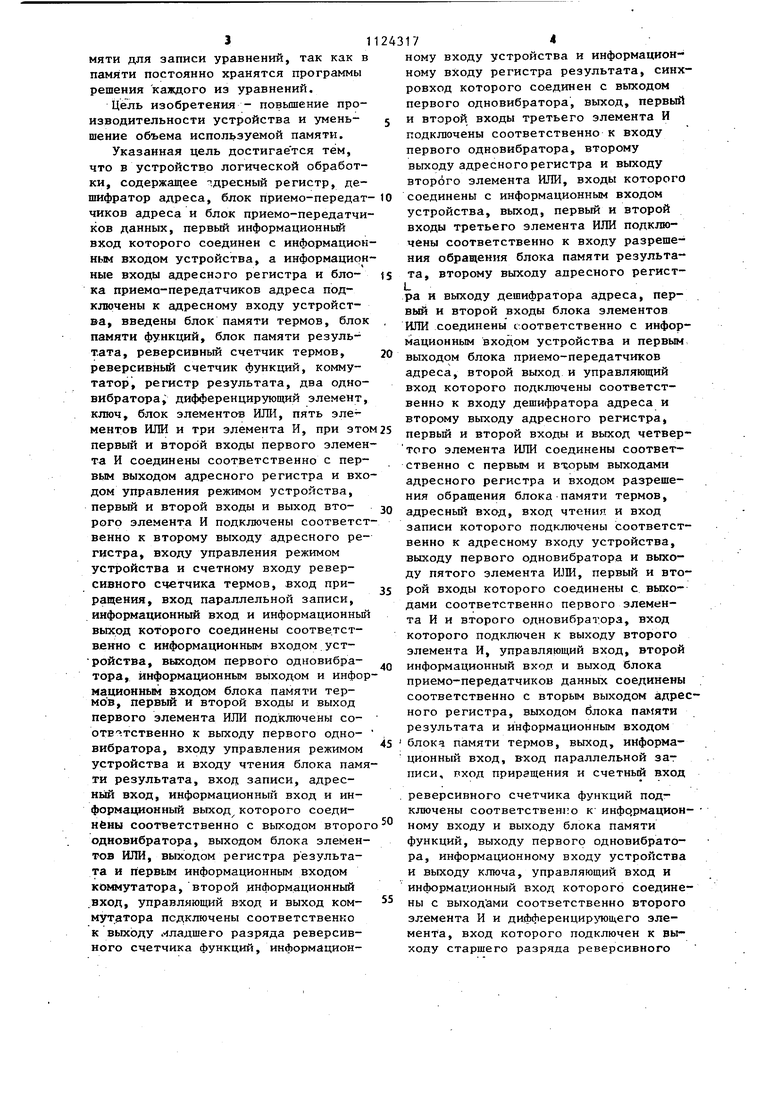

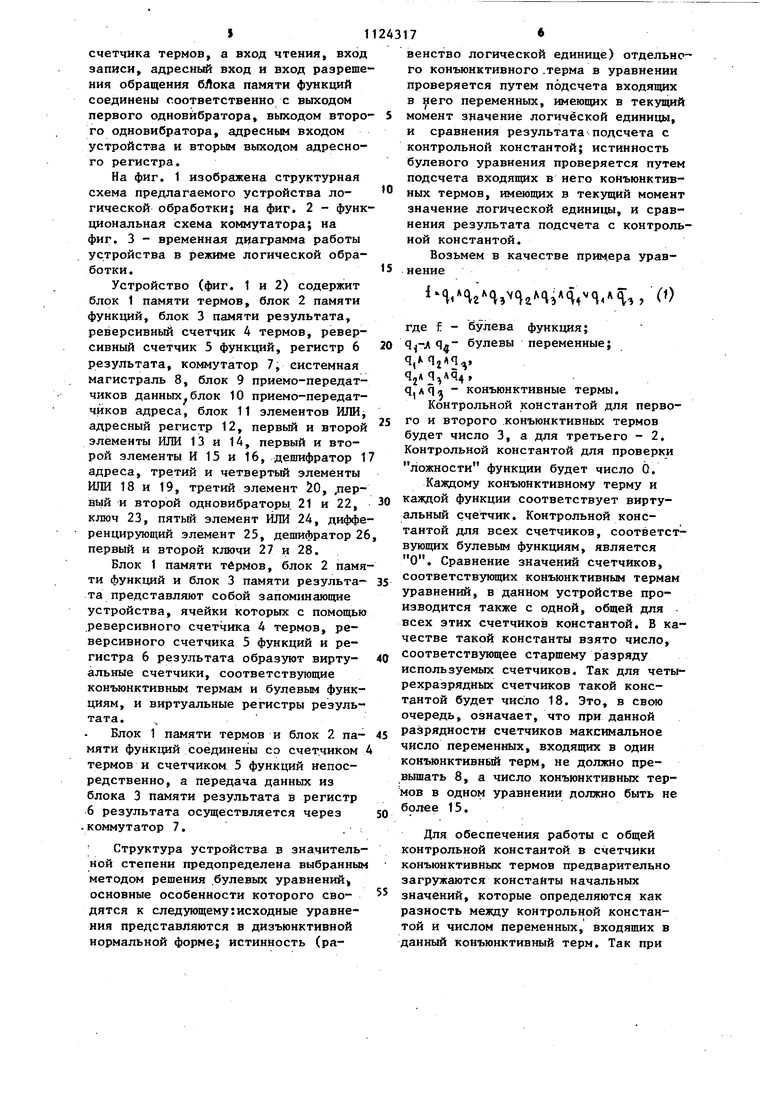

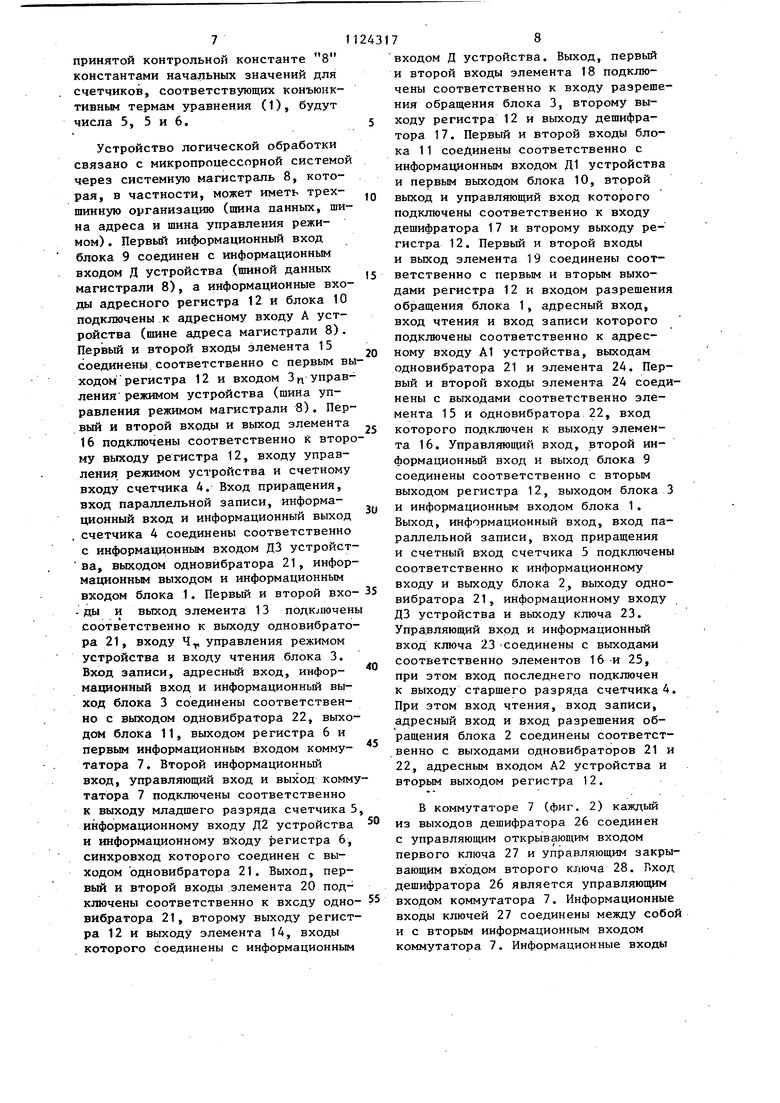

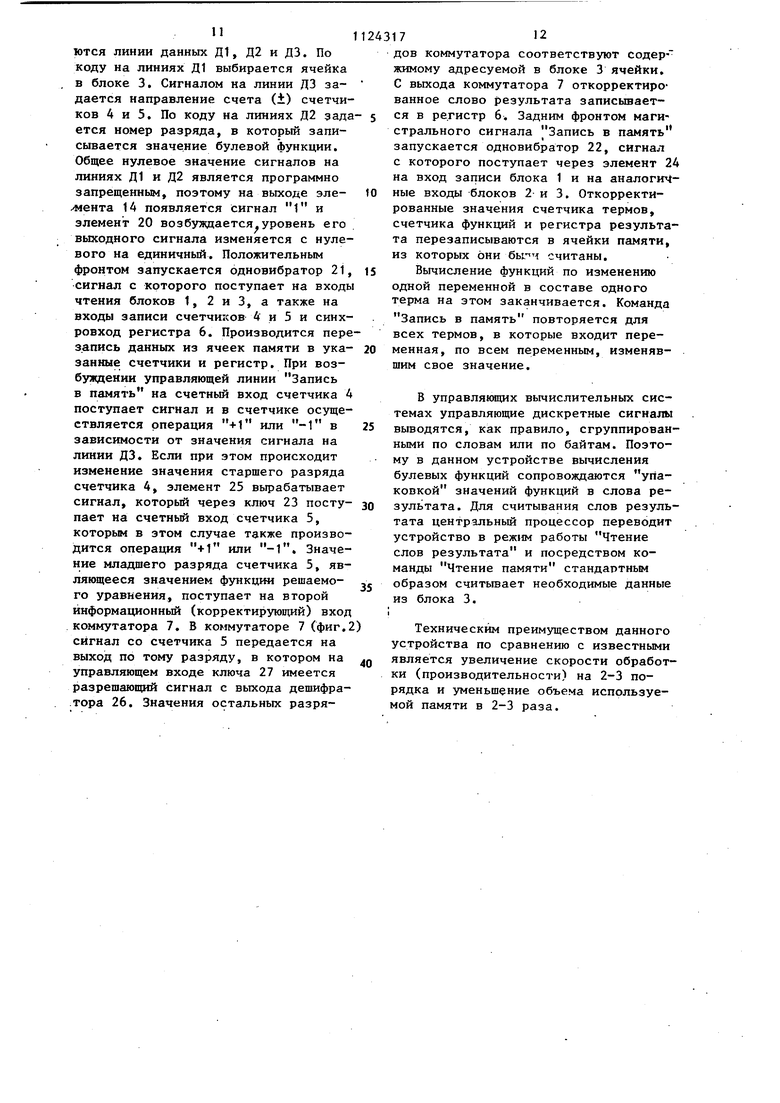

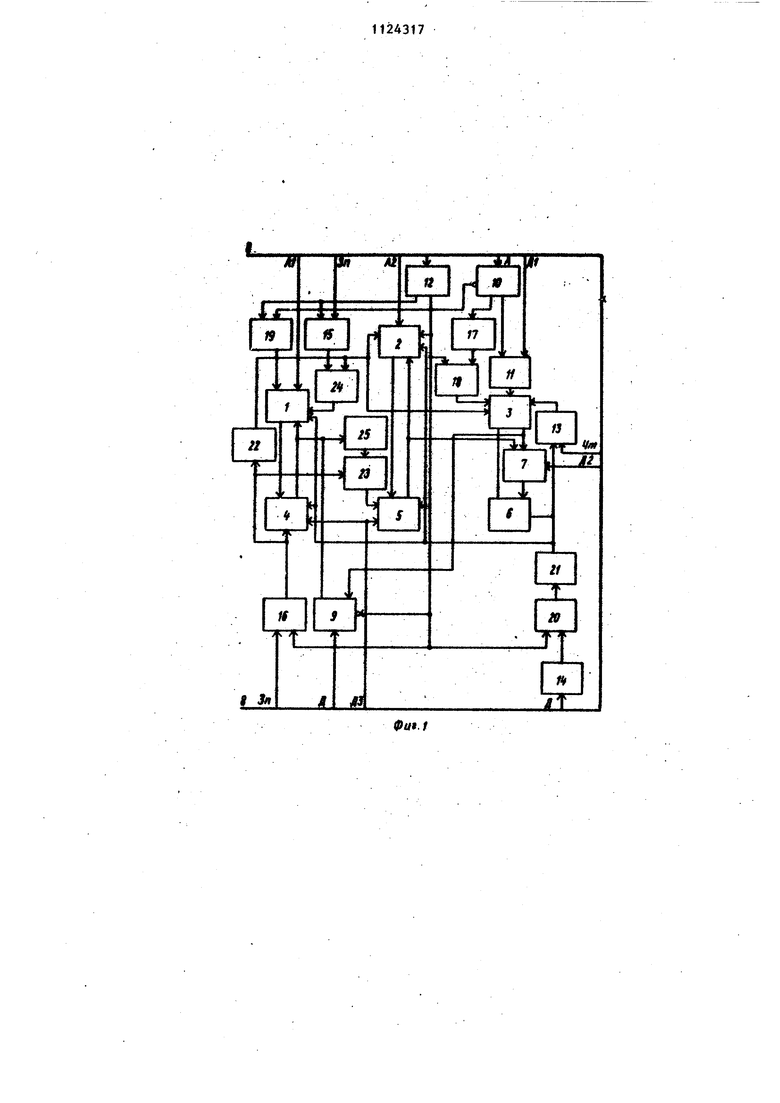

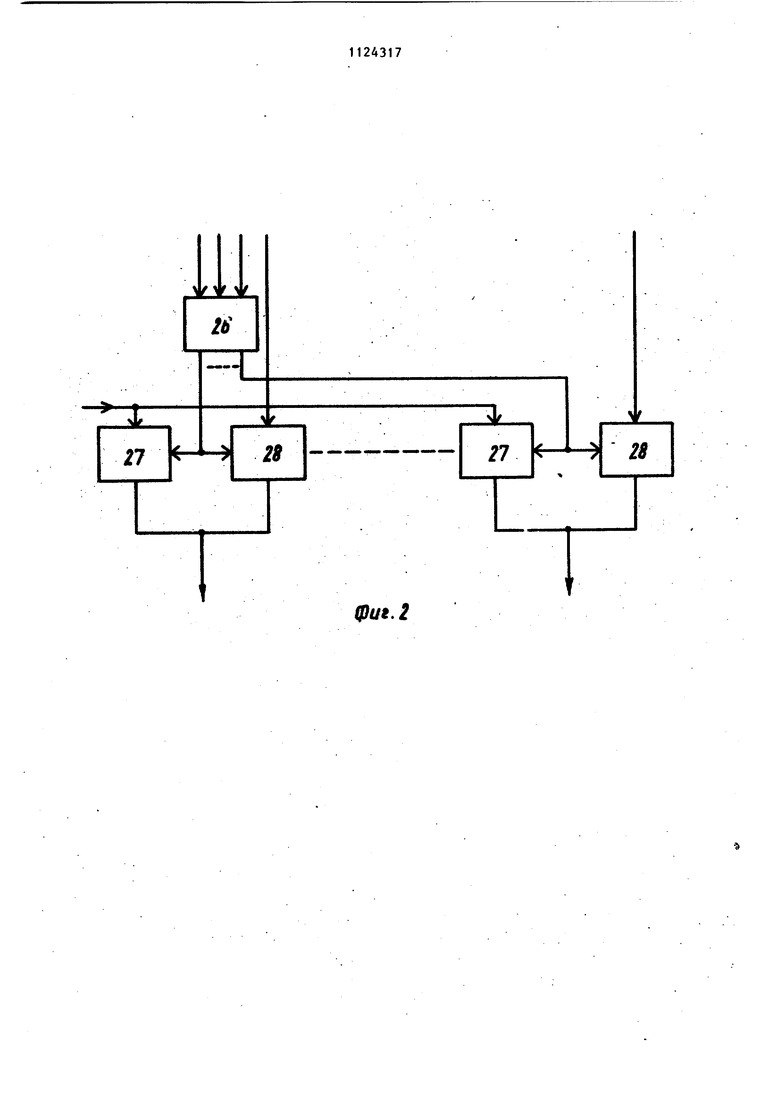

Недостатками известного устройства являются низкая скорость вычислений вследствие того, что каящый раз последовательно производится полная проверка выполнения условий булевых уравнений и программное формирование слов результата, и большой объем памяти для записи уравнений, так как памяти постоянно хранятся программы решения каждого из уравнений. Цель изобретения - повышение производительности устройства и уменьшение объема используемой памяти. Указанная цель достигаемся тем, что в устройство логической обработки, содержащее 1дресный регистр, дешифратор адреса, блок приемо-передат чиков адреса и блок приемо-передатчи ков данных, первый информационный вход которого соединен с информацион ным входом устройства, а информацио ные входы адресного регистра и блока приемо-передатчиков адреса подключены к адресному входу устройства, введены блок памяти термов, блок памяти функций, блок памяти результата, реверсивный счетчик термов, реверсивный счетчик функций, коммутатор, регистр результата, два одновибратора; дифференцирующий элемент ключ, блок элементов ИЛИ, пять элементов ИЛИ и три элемента И, при это первый и второй входы первого элемен та И соединены соответственно с первым выходом адресного регистра и вх дом управления режимом устройства, первый и второй входы и выход второго элемента И подключены соответс венно к второму выходу адресного ре гистра, входу управления режимом устройства и счетному входу реверсивного счетчика термов, вход приращения, вход параллельной записи, информационный вход и информационньм выход которого соединены соответственно с информационным входом устройства, выходом первого одновибратора, информационным выходом и инфо мационньп4 входом блока памяти термов, первый и второй входы и выход первого элемента ИЛИ подключены соотЕ тственно к выходу первого одновибратора, входу управления режимом устройства и входу чтения блока памя ти результата, вход записи, адресный вход, информационный вход и информационный выход которого соединены соответственно с выходом второ одновибратора, выходом блока элементов ИЛИ, выходом регистра результата и первым информационным входом коммутатора,второй информационный .вход, управляющий вход и выход коммутатора подключены соответственно к выходу младшего разряда реверсивного счетчика функций, информационному входу устройства и информацион-ному входу регистра результата, синхровход которого соединен с выходом первого одновибратора, выход, первый и второй входы третьего элемента И подключены соответственно к входу первого одновибратора, второму выходу адресного регистра и выходу второго элемента ИЛИ, входы которого соединены с информационным входом устройства, вькод, первый и второй входы третьего элемента ИЛИ подключены соответственно к входу разрешения обращения блока памяти результата, второму выходу адресного регистра и выходу дешифратора адреса, первый и второй входы блока элементов ИЛИ соединены соответственно с информационным входом устройства и первым выходом блока приемо-передатчиков адреса, второй выход и управляющий вход которого подключены соответственно к входу дешифратора адреса и второму выходу адресного регистра, первый и второй входы и выход четвертого элемента ИЛИ соединены соответственно с первым и втгорым выходами адресного регистра и входом разрешения обращения блока памяти термов, адресньв вход, вход чтения и вход записи которого подключены соответственно к адресному входу устройства, выходу первого одновибратора и выходу пятого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно первого элемента И и второго одновибратора, вход которого подключен к выходу второго элемента И, управляющий вход, второй информационный вход и выход блока приемо-передатчиков данных соединены соответственно с вторым выходом адресного регистра, выходом блока памяти результата и информационным входом блокэ памяти термов, выход, информационный вход, в-ход параллельной зат писи, вход приращения и счетный нход реверсивного счетчика функций подключены соответственно к инфо.рмацион- ному входу и выходу блока памяти функций, выходу первого одновибратора, информационному входу устройства и выходу ключа, управляющий вход и информационный вход которого соединены с выходами соответственно второго элемента И и дифференцир тощего элемента, вход которого подключен к выходу старшего разряда реверсивного счетчика термов, а вход чтения, вход записи, адресный вход и вход разреше ния обращения бЛока памяти функций соединены соответственно с выходом первого одновйбратора, выходом второ го одновйбратора, адресным входом устройства и вторым выходом адресного регистра. На фиг. 1 изображена структурная схема предлагаемого устройства логической обработки; на фиг. 2 - функ циональная схема коммутатора; на фиг. 3 - временная диаграмма работы устройства в режиме логической обработки. Устройство (фиг. 1 и 2) содержит блок 1 памяти термов, блок 2 памяти функций, блок 3 памяти результата, реверсивный счетчик 4 термов, реверсивный счетчик 5 функций, регистр 6 результата, коьшутатор 7, системная магистраль 8, блок 9 приемо-передатчиков данных блок 10 приемо-передатчиков адреса, блок 11 элементов ИЛИ адресный регистр 12, первый и второй элементы ИЛИ 13 и 14, первый и второй элементы И 15 и 16, дешифратор 1 адреса, третий и четвертый элементы ИЛИ 18 и 19, третий элемент 20, .первый и второй одновибраторы 21 и 22, ключ 23, пятый элемент ИЛИ 24, диффе ренцирующий элемент 25, дешифратор 2 первый и второй ключи 27 и 28. Блок 1 памяти термов, блок 2 памя ти функций и блок 3 памяти результата представляют собой запоминающие устройства, ячейки которых с помощью реверсивного счетчика 4 термов, реверсивного счетчика 5 функций и регистра 6 результата образуют виртуальные счетчики, соответствующие конъюнктивным термам и булевым функциям, и виртуальные регистры результата. Блок 1 памяти термов и блок 2 памяти функдай соединены со счет.чиком термов и счетчиком 5 функций непосредственно, а передача данных из блока 3 памяти результата в регистр 6 результата осуществляется через .коммутатор 7. Структура устройства в значительной степени предопределена выбранным методом решения .булевых уравнений основные особенности которого сводятся к следующему;исходные уравнения представляются в дизъюнктивной нормальной форме; истинность (равенство логической единице) отдельного конъюнктивного .терма в уравнении проверяется путем подсчета входящих в него переменных, имеющих в текущий момент значение логической единицы, и сравнения результатач подсчета с контрольной константой; истинность булевого уравнения проверяется путем подсчета входящих в него конъюнктивных термов, имеющих в текущий момент значение логической единицы, и сравнения результата подсчета с контрольной константой. Возьмем в качестве примера уравнениеЯ/ЯгПэ гИзЦлЯ.П, 0) где f - булева функция; Чл булевы переменные; q,,, ч, А Па конъюнктивные термы. Контрольной константой для первого и второго конъюнктивных термов будет число 3, а для третьего - 2. Контрольной константой для проверки ложности функции будет число 6. Каждому конъюнктивному терму и каждой функции соответствует виртуальный счетчик. Контрольной константой для всех счетчиков, соответствующих булевым функциям, является О, Сравнение значений счетчиков, соответствующих конъюнктивным термам уравнений, в данном устройстве производится также с одной, общей для всех этих счетчиков константой. В качестве такой константы взято число, соответствующее старшему разряду используемых счетчиков. Так для четырехразрядных счетчиков такой константой будет число 18. Это, в свою очередь, означает, что при данной разрядности счетчиков максимальное число переменных, входящих в один конъюнктивный терм, не должно превышать 8, а число конъюнктивных термов в одном уравнении должно быть не более 15. Для обеспечения работы с общей контрольной константой в счетчики конъюнктивных термов предварительно загружаются константы начальных значений, которые определяются как разность между контрольной константой и числом переменных, входящих в данный конъюнктив1а1й терм. Так при 71 принятой контрольной константе 8 константами начальных значений для счетчиков, соответствующих конъюнктивным термам уравнения (1), будут числа 5, 5 и 6. Устройство логической обработки связано с микропроцессорной системой через системную магистраль 8, которая, в частности, может иметь трехшинную организацию (щина данных, шина адреса и шина управления режимом) . Первый информационный вход блока 9 соединен с информационным входом Д устройства (шиной данных магистрали 8), а информационные входы адресного регистра 12 и блока 10 подключены к адресному входу А устройства (шине адреса магистрали 8), Первый и второй входы элемента 15 соединены соответственно с первым вы ходом регистра 12 и входом Зп управления режимом устройства (шина управления режимом магистрали 8). Первый и второй входы и выход элемента 16 подключены соответственно к второ му выходу регистра 12, входу управления режимом устройства и счетному входу счетчика 4. Вход приращения, вход параллельной записи, информационный вход и информационный выход счетчика 4 соединены соответственно с информационньм входом ДЗ устройст ва, выходом одновибратора 21, информационным выходом и информационным входом блока 1. Первый и второй вхо- ды и выход элемента 13 подключен соответственно к выходу одновибратора 21, входу Ч управления режимом устройства и входу чтения блока 3, Вход записи, адресный вход, информационный вход и информационный выход блока 3 соединены соответственно с выходом одновибратора 22, выходом блока 11, выходом регистра 6 и первым информационным входом коммутатора 7, Второй информационный вход, управляющий вход и выход комму татора 7 подключены соответственно к выходу младшего разряда счетчика 5 информационному входу Д2 устройства и информационному входу регистра 6, синхровход которого соединен с выходом одновибратора 21. Выход, первый и второй входы .элемента 20 подключены соответственно к входу одновибратора 21, второму выходу регистра 12 и выходу элемента 14, входы которого соединены с информационным 78 входом Д устройства. Выход, первый и второй входы элемента 18 подкхпочены соответственно к входу разрешения обращения блока 3, второму выходу регистра 12 и выходу дешифратора 17. Первый и второй входы блока 11 соединены соответственно с информационным входом Д1 устройства и первым выходом блока 10, второй выход и управляющий вход которого подключены соответственно к входу дешифратора 17 и второму выходу регистра 12. Первый и второй входы и выход элемента 19 соединены соответственно с первым и вторым выходами регистра 12 и входом разрешения обращения блока 1, адресный вход, вход чтения и вход записи которого подключены соответственно к адресному входу А1 устройства, выходам одновибратора 21 и элемента 24. Первый и второй входы элемента 24 соединены с выходами соответственно элемента 15 и одновибратора 22, вход которого подключен к выходу элемента 16. Управляющий вход, второй информационный вход и выход блока 9 соединены соответственно с вторым выходом регистра 12, выходом блока 3 и информационным входом блока 1. Выход, информационный вход, вход параллельной записи, вход приращения и счетный вход счетчика 5 подключены соответственно к информационному входу и выходу блока 2, выходу одновибратора 21, информационному входу ДЗ устройства и выходу ключа 23. Управляющий вход и информационный вход ключа 23 -соединены с вьпсодами соответственно элементов 16 и 25, при этом вход последнего подключен к выходу старшего разряда счетчика 4. При этом вход чтения, вход записи, адресный вход и вход разрешения обращения блока 2 соединены соответственно с выходами одновибраторов 21 и 22, адресным входом А2 устройства и вторым выходом регистра 12. В коммутаторе 7 (фиг. 2) каждый из выходов дешифратора 26 соединен с управляющим открывающим входом первого ключа 27 и управляющим закрывающим входом второго ключа 28. Пход дешифратора 26 является управляющим входом коммутатора 7. Информационные входы ключей 27 соединены между собой и с вторым информационным входом коммутатора 7. Информационные входы ключей 28 являются первым информацио ным входом коммутатора 7. Выходы клю чей 27 и 28, относящиеся к одному разряду, соединены мезцду собой и.являются информационньм выходом комму:татора 7. Для управления устройством логической обработки со стороны централь ного процессора микропроцессорной системы предусматривается использова ние трех команд: Вывод, Запись в память, Чтение памяти (эти команды являются типовыми для микропроцессоров) . По команде Вывод процессор записывает в регистр 12 признак режима работы. Устройство имеет три режима работы: логическая обработка (первьй выход регистра 12 имеет значение 1, второй - О); чтение слов результата (первый и второй выходы регистра 12 имеют значение О); запись констант в счетчики тер мов (первый выход регистра 12 имеет значение О, второй - 1). I По команде Запись в память процессор осуществляет запись констант начальных значений в счетчики конъюн тивных термов (в режиме Запись констант в счетчики термов) или задает связанную цепочку счетчик терма-сче чик функции-разряд в слове результата и определяет выполняемую в уст ройстве операцию - прибавление или вычитание 1 (в режиме Логическая обработка). По команде Чтение памяти осуществляется вьтод значений булевых функций из блока 3. Устройство работает следующим об.разом, В .начале работы ячейки блока 2 : обнуляются И В регистр 12 процессором системы по команде Вьшод за;сылается значение признака режима рабочи Запись констант в счетчики терйов. Сигнал с второг о выхода регистра 12 поступает через элемент 19 и& вход разрешения обращения блока t,. подготавливая его к работе, и на вход элемента 15. Затем про цессор стандартным образом с помощью команды Запись в память последовательно загружает в ячейки блока 1, соответствующие счетчикам конъюнктивных термов, константы начальных значений. При этом на адресный вход блока 1 поступает код адреса А1 соответствзтощей ячейки, а по Ьшне данных через блок 9 - значение константы начальной загрузки. После загрузки констант начальных значений очередной командой Вывод устанавливается режим работы Логическая обработка. Данное устройство предназначено для работы в составе вычислительной системы, в которой независимо от устройства логической обработки осуществляется контроль за изменением значений переменных, входящих в булевые уравнения, В системе (ее управляющей программе) для каждой переменной имеется список конъюнктивных термов, в которые она входит, а для каждого конъюнктивного терма - список функ.ций, в уравнения которых он входит, и также адреса функций в блоке 3, В устройство поступает информация, связанная только с переменньми, изменившими свое значение. При выполнении команды Запись в память на линиях А1, А2 и Д1 магистрали 8 устанавливаются коды адресов соответственно счетчика термов, в которь1й входит текущая переменная, счетчика функции, в уравнение которой входит данньй терм, и слова результата, в которое помещается значение вычисляемой функции. На линиях Д2 устанавливается код, определяющий разряд в адресуемом слове результата для значения переменнрй. Значение сигнала Сложение-вычитание, подаваемого на счетчики 4 и 5, задается через линию данных ДЗ, на которую подается значение логической единицы в том случае, если значение текущей переменной равно 1 и переменная входит в данный конъюнктивный терм без инверсии или если значение текущей переменной равно О и она входит в данный конъюнктивный терм с инверсией. Значение логического нуля на линию ДЗ подается в том случае, если значение текущей переменкой равно О и она входит в данный конъюнктивньй терм без инверсии, шти если значение текущей переменной равно 1 и она входит в данный конъюнктивный терм с инвсрси-, ей. Работа устройства в режиме Логическая обработка поясняется временной диаграммой (фиг. 3). Выполнение команда Запись в память иа кнавтся с возбуждения адресных линий А1 и А2,При этом в блоке 1 и в блоке 2 подготавливается доступ к адресуемьм ячейкам. Затем возбуждатотся линии данных Д1, Д2 и ДЗ. По коду на линиях Д1 выбирается ячейка в блоке 3. Сигналом на линии ДЗ задается направление счета (1) счетчиков 4 и 5. По коду на линиях Д2 зада ется номер разряда, в который записывается значение булевой функции. Общее нулевое значение сигналов на линиях Д1 и Д2 является программно запрещенным, позтому на выходе элемента 14 появляется сигнал 1 и злемент 20 возбуждается.уровень его выходного сигнала изменяется с нулевого на единичный. Положительным фронтом запускается одновибратор 21, сигнал с которого поступает на входы чтения блоков 1, 2 и 3, а также на входы записи счетчиков 4 и 5 и синхровход регистра 6. Производится пере запись данных из ячеек памяти в указанные счетчики и регистр. При возбуждении управляющей линии Запись в память на счетный вход счетчика 4 поступает сигнал и в счетчике осуществляется операция +1 или -1 в зависимости от значения сигнала на линии ДЗ. Если при этом происходит изменение значения старшего разряда счетчика 4, элемент 25 вырабатывает сигнал, который через ключ 23 поступает на счетный вход счетчика 5, которым в этом случае также производится операция +1 или -1, Значение младшего разряда счетчика 5, являющееся значением функции решаемого уравнения, поступает на второй информационный (корректирующий) вход коммутатора 7. В коммутаторе 7 (фиг, сигнал со счетчика 5 передается на выход по тому разряду, в котором на управляющем входе ключа 27 имеется разрешающий сигнал с выхода дешифра.тора 26. Значения остальных разря1712дов коммутатора соответствуют содер- жимому адресуемой в блоке 3 ячейки, С вьпсода коммутатора 7 откорректированное слово результата записывается в регистр 6. Задним фронтом магистрального сигнала Запись в память запускается одновибратор 22, сигнал с которого поступает через элемент 24 на вход записи блока 1 и на аналогичные входы -блоков 2- и 3. Откорректированные значения счетчика термов, счетчика функций и регистра результата перезаписываются в ячейки Пс1мяти, из которых они считаны. Вычисление функций по изменению одной переменной в составе одного терма на этом заканчивается. Команда Запись в память повторяется для всех термов, в которые входит переменная, по всем переменным, изменявшим свое значение. В управляющих вычислительных системах управляющие дискретные сигналы выводятся, как правило, сгруппированными по словам или по байтам. Позтому в данном устройстве вычисления булевых функций сопровождаются упаковкой значений функций в слова результата. Для считывания слов результата центральный процессор переводит устройство в режим работы Чтение слов результата и посредством команды Чтение памяти стандартным образом считьгаает необходимые данные из блока 3. Техническим преимуществом данного устройства по сравнению с известными является увеличение скорости обработки (производительности) на 2-3 порядка и уменьшение объема используемой памяти в 2-3 раза.

фиг. 2

А1,А2

MiMAL

выход элемента --

1120

Выход о9HOBuSjsomo0021

Выход одно8иШто)а22

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4153942, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1984-11-15—Публикация

1982-12-09—Подача