11

Изобретение относится к цифровой вычислительной технике а именно к устройствам для вычисления операций над машинными числами, и может быть использовано при создании высокопроизводительных вычислительных устройств..

Цель изобретения - повышение бысродействия.

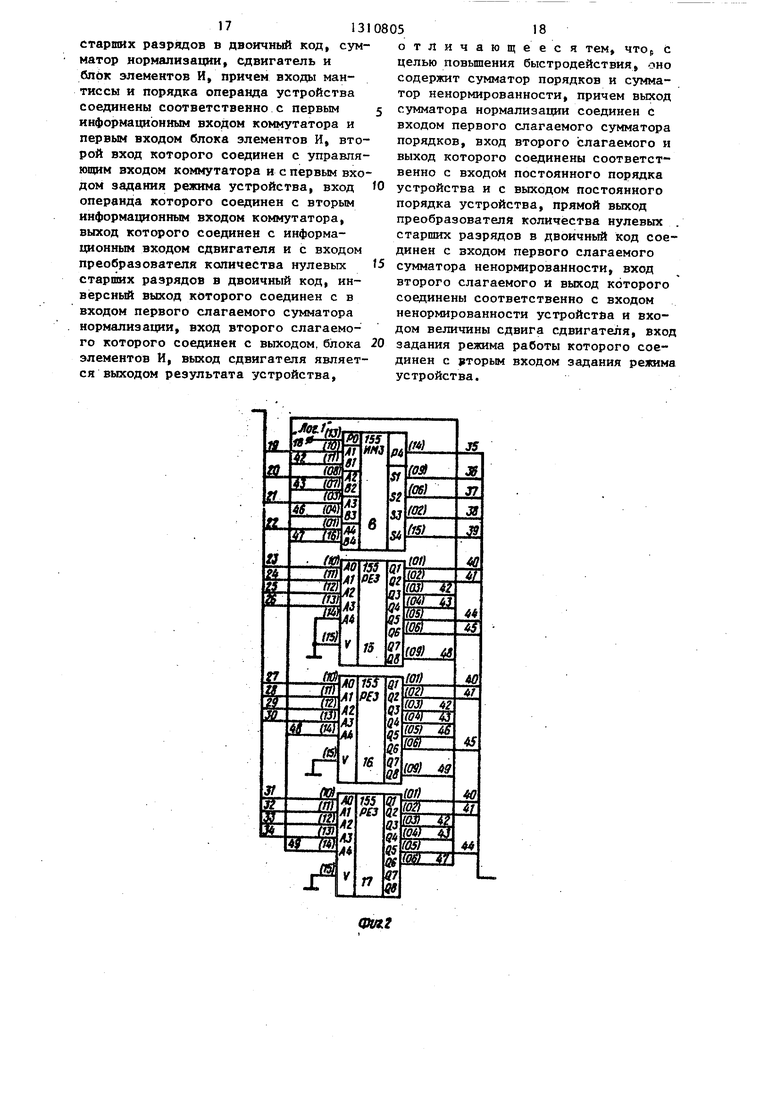

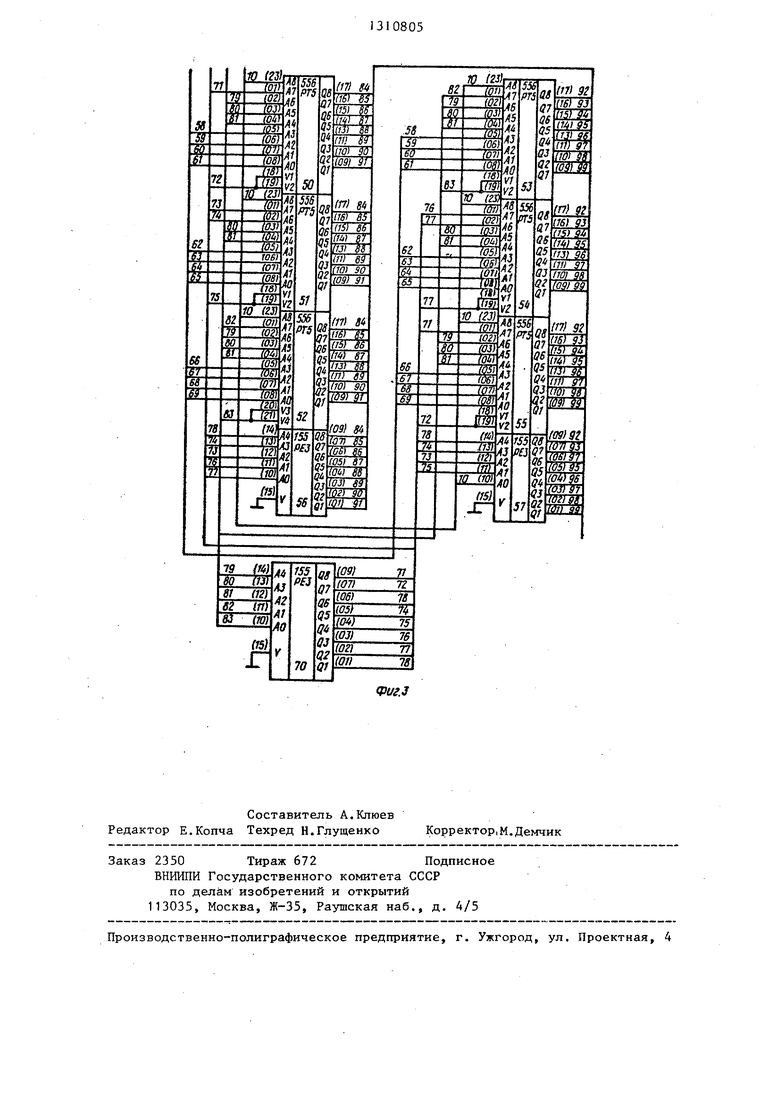

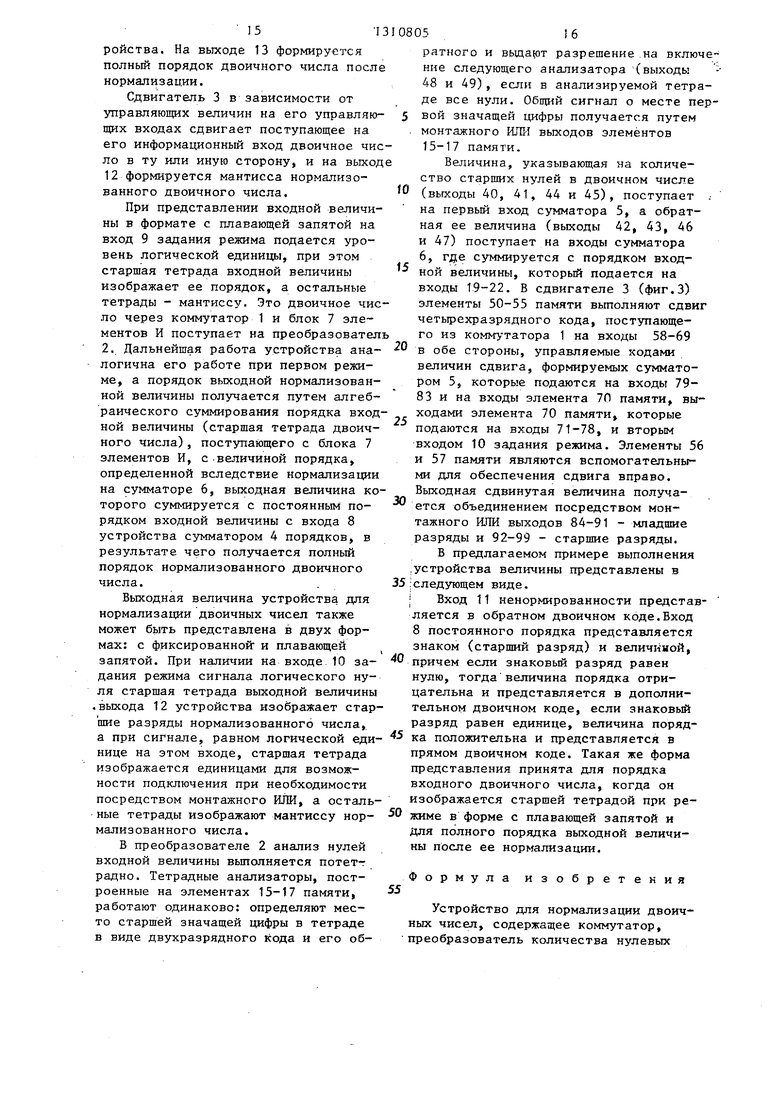

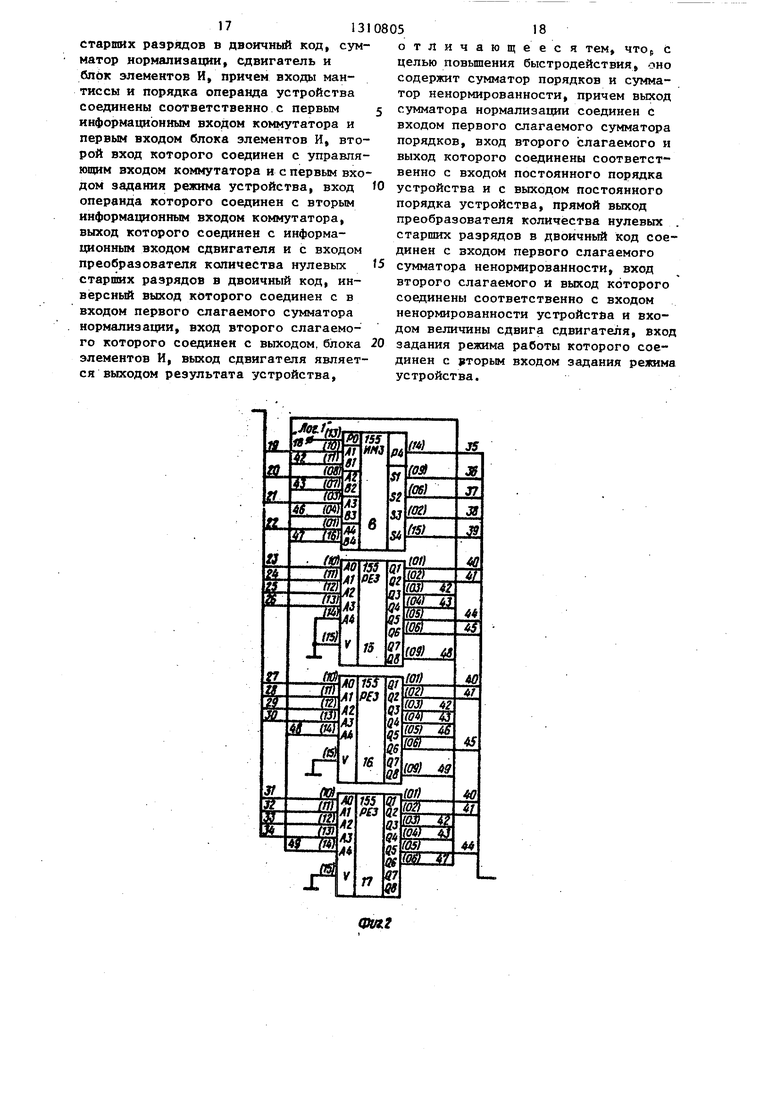

На фиг. 1 изображена cxeMia устройства для нормализации двоичных чисел; на фиг. 2 - схема преобразователя количества нулевых старших разрядов в двоичный код и его связи с сумматором нормализации; на фиг, 3 - схема сдвигателя.

На фиг. 1-3 1щфрами в скобках стоящих около линий и стрелок, обозначены порядковые номера соответственно входов и выходов.

Устройство для нормализации двои ных чисел (фиг. 1) содержит коммутатор 1, преобразователь 2 количества нулевых старших разрядов в двоичный код, сдвигатель 3, сумматор 4 порядков, сумматор 5 ненормированно

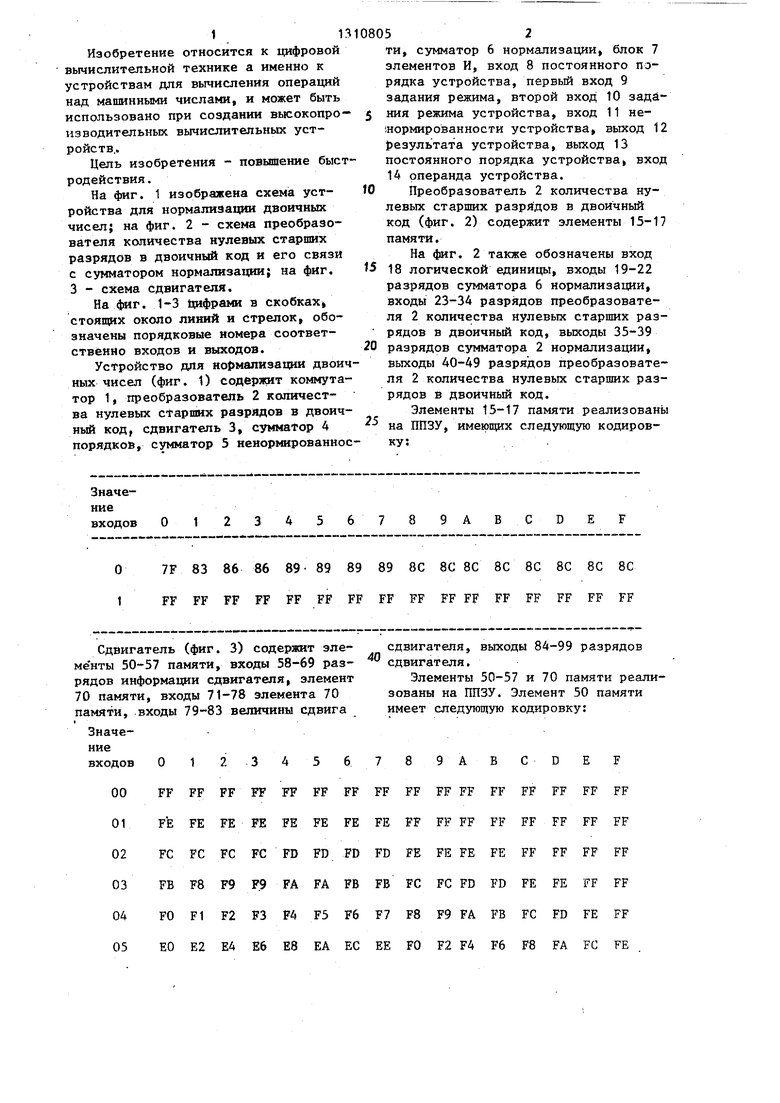

07F 83 86 86 89- 89 89 89 8С 8С 8С 8С 8С 8С 8С 8С

1FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

Сдвигатель (фиг. 3) содержит эле- ме нты 50-57 памяти, входы 58-69 разрядов информации сдвигателя, элемент 70 памяти, входы 71-78 элемента 70 памяти, входы 79-83 величины сдвига

Значениевходов О 1 23 4 5 6

00FFFFFFFFFFFFFF

01FEFEFEFEFEFEFE

02FCFCFCFCFDFDFD

03FBF8F9F9FAFAFB

04FOF1F2F3F4F5F6

05ЕОЕ2Е4Е6Е8ЕАЕС

ти, сумматор 6 нормализации, блок 7 элементов И, вход 8 постоянного порядка устройства, первый вход 9 задания режима, второй вход 10 задй- ния режима устройства, вход 11 не- мормированности устройства, выход 12 езультата устройства, выход 13 постоянного порядка устройства, вход 14 операнда устройства.

Преобразователь 2 количества нулевых старших разрядов в двоичный код (фиг. 2) содержит элементы 15-17 памяти.

На фиг. 2 также обозначены вход 18 логической единицы, входы 19-22 разрядов сумматора 6 нормализации, входы 23-34 разрядов преобразователя 2 количества нулевых старших разрядов в двоичный код, выходы 35-39 разрядов сумматора 2 нормализации, выходы 40-49 разрядов преобразователя 2 количества нулевых старших разрядов в двоичный код.

Элементы 15-17 памяти реализованы на ППЗУ, имеющих следующую кодировку:

40

сдвигатепя, выходы 84-99 разрядов сдвигателя.

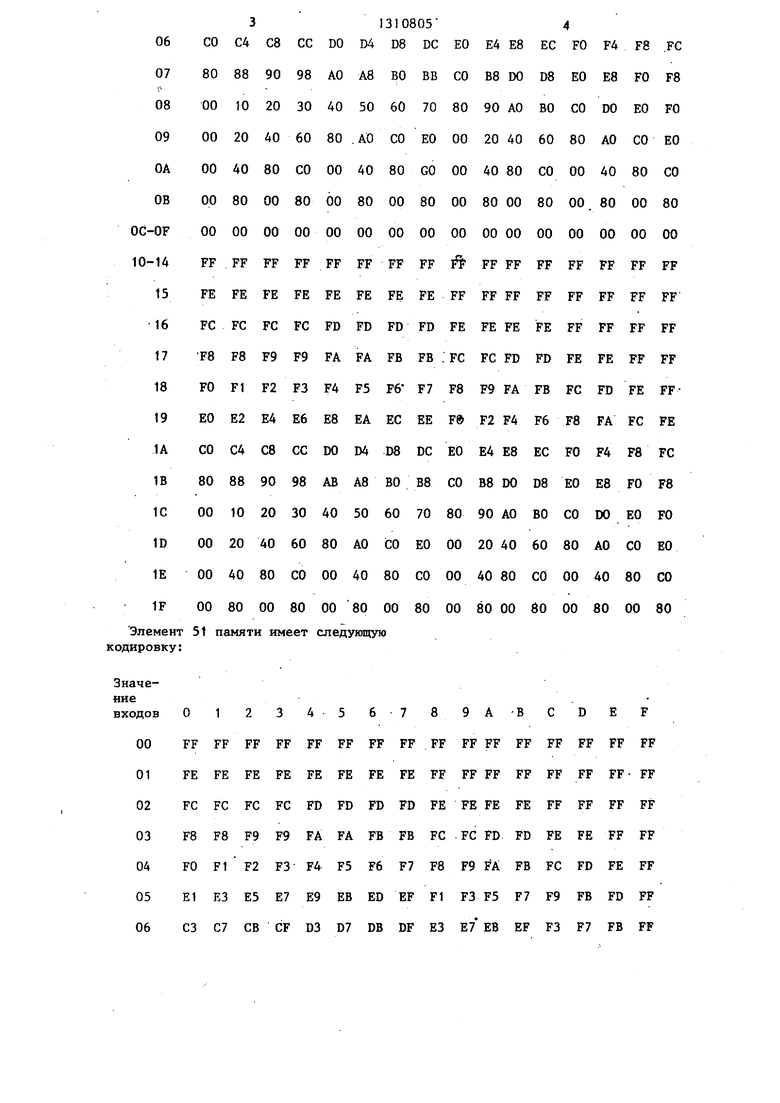

Элементы 50-57 и 70 памяти реализованы на ППЗУ. Элемент 50 памяти имеет следующую кодировку:

89АВCDЕF

FFFF FFFFFFFFFFFF

FFFF FFFFFFFFFFFF

FEFE FEFEFFFFFFFF

FCFC FDFDFEFEFFFF

F8F9 FAFBFCFDFEFF

FOF2 F4F6F8FAFCFE

31310805 4

06СО С4 С8 СС DO D4 D8 DC EG Е4 Е8 ЕС FO F4 FB FC

0780 88 90 98 АО A8 ВО ВВ СО В8 DO D8 ЕО Е8 FO F8

0800 10 20 30 АО 50 60 70 80 90 АО ВО СО DO ЕО FO

0900 20 40 60 80 . АО СО ЕО 00 20 40 60 80 АО СО ЕО ОА00 40 80 СО 00 40 80 GO 00 40 80 СО 00 40 80 СО ОБ00 80 00 80 00 80 00 80 00 80 00 80 00. 80 00 80

OC-OF00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

10-14FF FF FF FF FF FF FF FF И FF FF FF FF FF FF FF

15FE FE FE FE FE FE FE FE FF FF FF FF FF FF FF FF

16FC FC FC FC FD FD FD FD FE FE FE FE FF FF FF FF

17Т8 F8 F9 F9 FA FA FB FB . FC FC FD FD FE FE FF FF

18FO F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF19ЕО Е2 Е4 Е6 Е8 ЕА ЕС ЕЕ F& F2 F4 F6 F8 FA FC FE 1АСО С4 С8 СС DO D4 D8 DC ЕО Е4 Е8 ЕС FO F4 F8 FC 1В80 88 90 98 АВ А8 ВО В8 СО В8 DO D8 ЕО Е8 FO F8 1C00 10 20 30 40 50 60 70 80 90 АО ВО СО DO ЕО FO ID00 20 40 60 80 АО СО ЕО 00 20 40 60 80 АО СО ЕО IE00 40 80 СО 00 40 80 СО 00 40 80 СО 00 40 80 СО

IF00 80 00 80 00 80 00 80 00 80 00 60 00 80 00 80

Элемент 5 памяти имеет следующую кодировку:

ЗначениевходовО 1 2 3 45 67 89А-В С D Е F

00FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

01FE FE FE FE FE FE FE FE FF FF FF FF FF FF FF FF

02FC FC FC FC FD FD FD FD FE FE FE FE FF FF FF FF

03F8 F8 F9 F9 FA FA FB FB FC FC FD FD FE FE FF FF

04FO F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

05Е1 ЕЗ Е5 Е7 Е9 ЕВ ED EF F1 F3 F5 F7 F9 FB FD FF

06СЗ С7 СВ CF D3 D7 DB DF ЕЗ Е7 ЕВ EF F3 F7 FB FF

5 13108056

07878F979FА7AFВ7BFC7CF D7DFE7 EF F7 FF

08OF IF2F3F4F5F6F7F8F9F AFBFCF DF EF FF

09IF3F5F7F9FBFDFFFIF3F 5F7F9F BF DF FF DA 3F7FBFFF3F7FBFFF3F7F BFFF 3F 7F BF FF OB7FFF7FFF 7FFF7FFF7FFF 7FFF 7F FF DF FF

OC-1AFFFFFFFFFFFFFFFFFFFF FFFFFF FF FF FF

15FEFEFEFEFEFEFEFEFFFF FFFFFF FF FF FF

16FCFCFCFCFDFDFDFDFEFE FEFEFF FF FF FF

17F8F8F9F9FAFAFBFBFCFC FDFDFE FE FF FF

18FOF1F2F3F4F5F6 F7F8F9 FAFBFC FD FE FF

19ElE3E5E7E9EBEDEFF1F3 F5F7F9 FB FD FF 1AC3C7 CBCFD3D7DBDFE3.E7 EBEF3F F7 FB FF 1B878F979FA7AFB7BFC7CF D7DFE7 EF F7 FF 1COF IF 2F3F4F5F6F7F8F9F AFBFCF DF EF FF IDIF3F 5F7F 9FBFDFFFIF3F 5F7F9F BF DF FF IE3F 7F BFFF 3F7FBFFF3F7F BFFF3F 7F BF FF

IF 7F FF 7FFF 7FFF7FFF7FFF 7FFF 7F FF 7F FF

Элемент 52 памяти имеетследующую .кодировку:

Значениевходов0123456789ABCDEF

0000000000000000000000 000000 00 00 00

0100000000000000000101 010101 01 01 01

0200000000010101010202.020203 03 03 03

0300000101020203030404 050506 06 07 07

0400010203040506070809 ОАОБОС OD ОЕ OF

050103050709OBODOF1113 151719 IB 1D IF

060307OBOF1317IBIF2327 2B2F33 37 3B 3F

0707OF17IF272F372F474F 575F67 6F 77 7F

08OFIF2F3F4F5F6F7F8F9F AFBFCF DF EF FF

09IF3F5F7F9FBFDFFF1F3F 5F7F9F BF DF FF

713108058

ОА 3F 7F BF FF 3F 7F BF FF 3F 7F BF FF 3F 7F BF FF

OB 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF

GC-OFFF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

10-1400 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

1500 00 00 00 00 00 00 00 00 01 01 01 01 01 01 01

1600 00 00 00 01 01 01 01 02 02 02 02 03 .03 03 03

1700 00 01 01 02 02 03 03 04 04 05 05 06 06 07 07

1800 01 02 03 04 05 06 07 0 09 OA OB ОС OD OE OF

1901 03 05 07 09 OB ОГ) OF 11 13 15 17 19 IB ID IF 1A03 07 OB OF 13 17 18 IF 23 27 2B 2F 33 37 3B 3F 1B07 OF 17 IF 27 2F 37 3F 47 4F 57 5F 67 6F 77 7F 1COF IF 2F 3F 4F 5F 6F 7F 8F 9F AF BF CF DF EF FF ID IF 3F 5F 7F 9F BF DF FF IF 3F 5F 7F 9F BF DF FF IE3F 7F BF FF 3F 7F BF FF 3F 7F BF FF 3F 7F BF FF

IF7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF

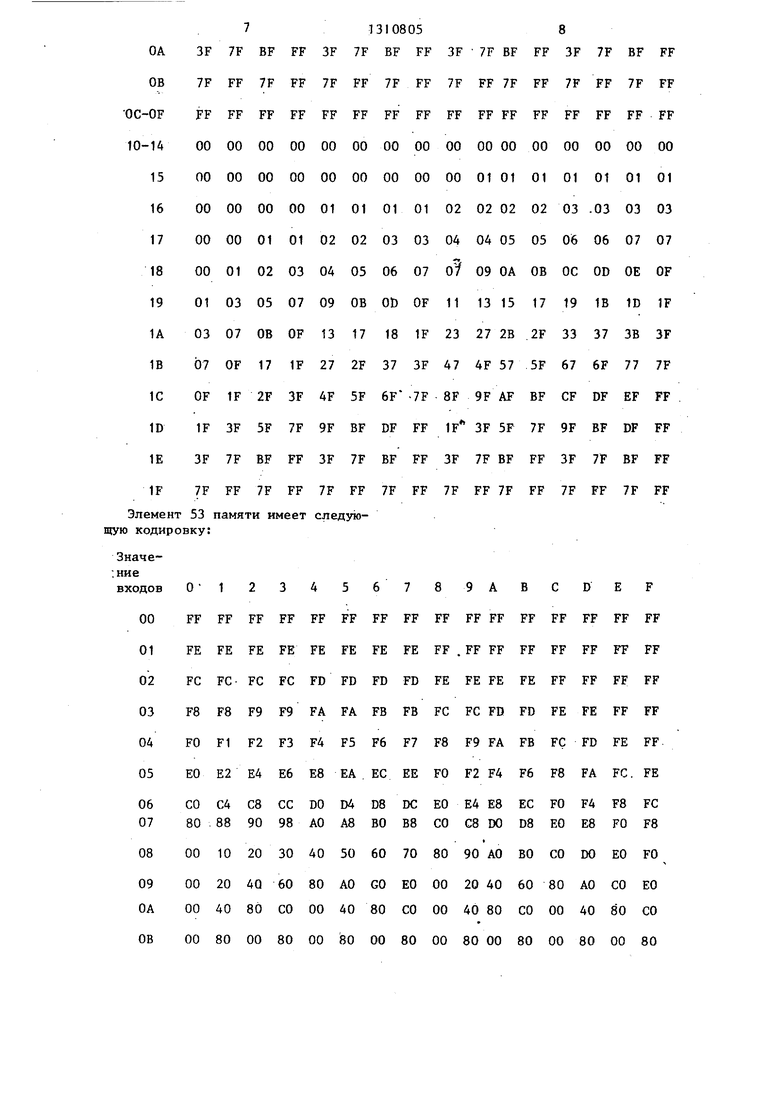

Элемент 53 памяти имеет следующую кодировку:

Значе- ;ние

входов0-1 23456789ABCDEF

00FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

01FE FE FE FE FE FE FE FE FF . FF FF FF FF FF FF FF

02FC FC FC FC FD FD FD FD FE FE FE FE FF FF FF FF

03F8 F8 F9 F9 FA FA FB FB FC FC FD FD FE FE FF FF

04FO F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

05ЕО Е2 Е4 Е6 Е8 ЕА . ЕС ЕЕ FO F2 F4 F6 F8 FA FC. FE

06СО С4 С8 СС DO DA D8 DC ЕО Е4 Е8 ЕС FO FA F8 FC

0780 88 90 98 АО A8 ВО В8 СО С8 DO D8 ЕО Е8 FO F8

I

0800 10 20 30 АО 50 60 70 80 90 АО ВО СО DO ЕО FO

0900 20 AQ 60 80 АО GO ЕО 00 20 АО 60 80 АО СО ЕО ОА00 40 80 СО 00 АО 80 СО 00 АО 80 СО 00 АО 80 СО

ОВ00 80 00 80 00 iBO 00 80 00 80 00 80 00 80 00 80

131080510

OC-OF 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

10-14 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

15FE FE FE FE FE FE FE FE FF FF FF FF FF FF FF FF

16FC FC FC FC FD FD FD FD FE FE FE FE FF FF FF FF

17F8 F8 F9 F9 FA FA FB FB FC . FC FD FD FE FE FF FF

18FO F1 F2 F3 F4 F5 F6 F7 F8 F8 FA FB FC FD FE FF

19FO F2 FA F6 F8 FA FC FE FO F2 F4 F6 F8 FA FC FE 1A FO F4 F8 FC FO F4 F8 FC FO F4 F8 FC FO F4 F8 FC IB. FO F8 FO F8 FO F8 FO FB FO F8 FO F8 FO F8 FO F8

1D-1F FO FO FO FO FO FO FO FO FO FO FO FO FO FO FO FO

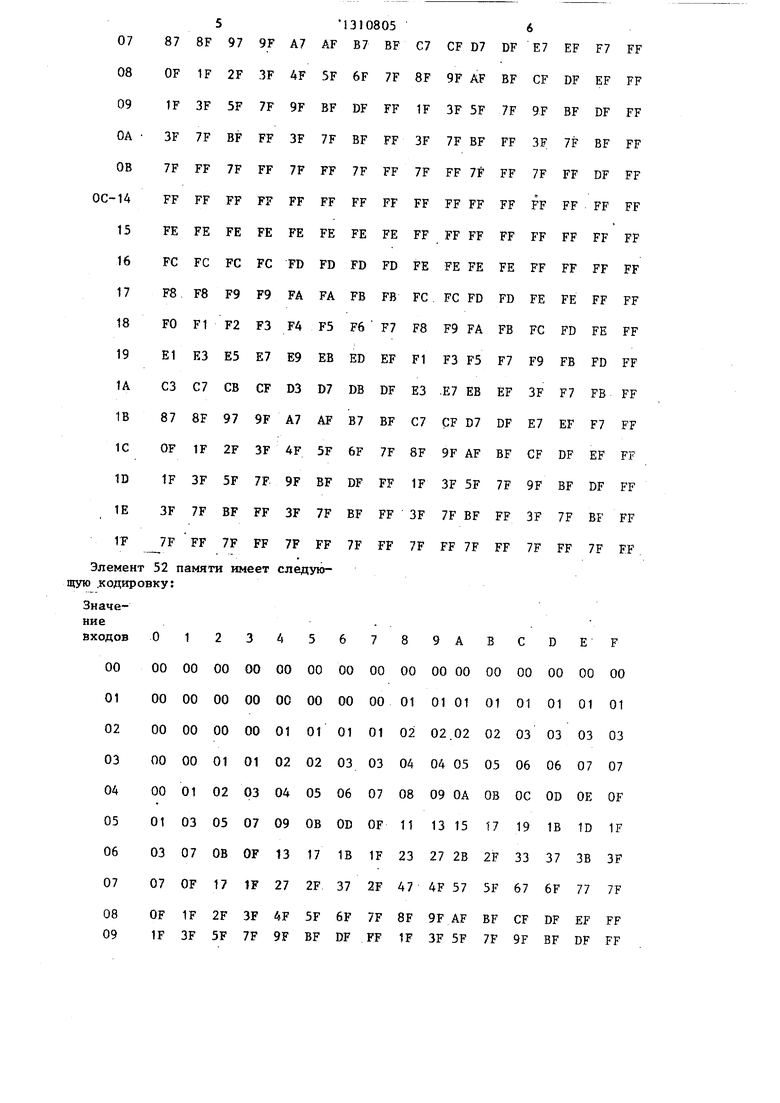

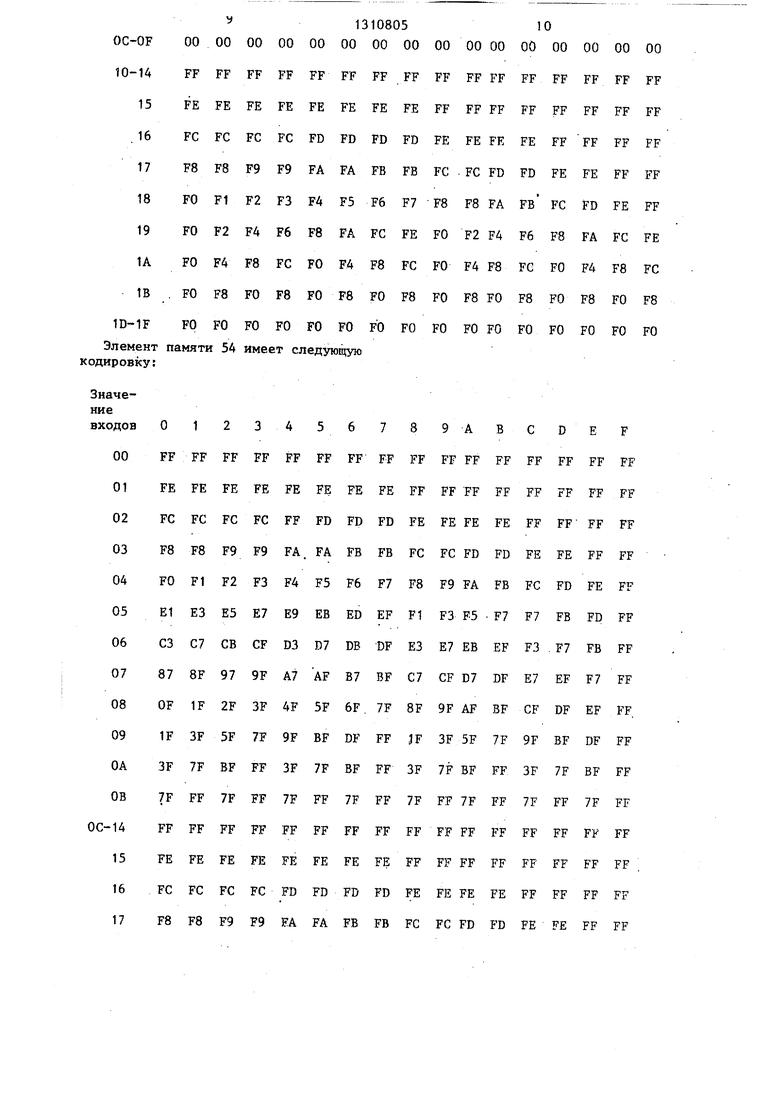

Элемент памяти 54 имеет следзпощую кодировку:

Значение

входовО 1 2 34 56 7 8 9 А В С DE F

00FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

01FE FE FE FE FE FE FE FE FF FF FF FF FF FF FF FF

02FC FC FC FC FF FD FD FD FE FE FE FE FF FF FF FF

03F8 F8 F9 F9 FA. FA FB FB FC FC FD FD FE FE FF FF

04FO F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

05Е1 ЕЗ Е5 Е7 Е9 ЕВ ED EF F1 F3 Е5 - F7 F7 FB FD FF

06СЗ С7 СВ CF D3 D7 DB DF ЕЗ Е7 ЕВ EF F3 . F7 FB FF

0787 8F 97 9F А7 AF В7 BF С7 CF D7 DF Е7 EF F7 FF

08OF IF 2F 3F 4F 5F 6F. 7F 8F 9F AF BF CF DF EF FF,

09IF 3F 5F 7F 9F BF DF FF JF 3F 5F 7F 9F BF DF FF OA3F 7F BF FF 3F 7F BF FF 3F 7F BF FF 3F 7F BF FF OB7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF 7F FF

ОС-14FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

15FE FE FE FE FE FE FE FE FF FF FF FF FF FF FF FF ,

16FC FC FC FC FD FD FD FD FE FE FE FE FF FF FF FF

17F8 F8 F9 F9 FA FA FB FB FC FC FD FD FE FE FF FF

II131080512

18 FO F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FB FC FD FE FF

.19F1F3 .F5F7F9FBFFFFF1F3F5F7F9FBFDFF

1AF3F7 FBFFF3F7FBFFF3F7FBFFF3F7FBFF

IBF7FF F7FFF7FFF7FFF7FFF7FFF7FFF7FF

1C-1FFFFF FFFFFFFFFFFFFFFFFFFFFFFFFFFF

Элемент 55 имеет следующую .кодировку:

Значениевходив 01 2345678 9 ABCDEF

0000000000000000000000 000000000000

0100000000000000000101 010101010.101

0200000000010101010202 020203030303

0300000101020203030404 050506060707

0400010203040506070809 ОАОВОСODОБOF

050103050709ОВОБOF1113 1517191ВIDIF

060307ОВOF13171В1F2327 2В2F3337ЗВ3F

0707OF17IF272F373F474F 575F676F777F

08OFIF2F3F4F5F6F7F8F9F AFBFCFDFEFFF .091F3F5F7F9FBFDFFF1F3F 5F7F9FBFDFFF

OA3F7FBFFF3F7FBFFF3F7F BFFF3F7FBFFF

OB7FFF7FFF7FFF7FFF7FFF 7FFF7FFF7FFF

OC-OEFFFFFFFFFFFFFFFFFFFF FFFFFFFFFFFF

OFFFFFFFFFFFFFFFFFFFFF FFFFFFFFFF00

10-11FOFOFOFOFOFOFOFOFOFO FOFOFOFOFO00

12-14FOFOFOFOFOFOFOFOFOFO FOFOFOFOFOFO

15FOFOFOFOFOFOFO.FOF1F1 F1F1F1F1F1F1

16FOFOFOFOF1F1F1F1F2F2 F2F2F3F3F3F3

17FOFOF1F1F2F2F3F3F4F4 F5F5F6F6F7F7

18FOF1F2F3F4F5F6F7F8F9 FAFBFCFDFEFF

19F1F3F5F7F9FBFDFFF1F3 F5F7F9FBFDFF

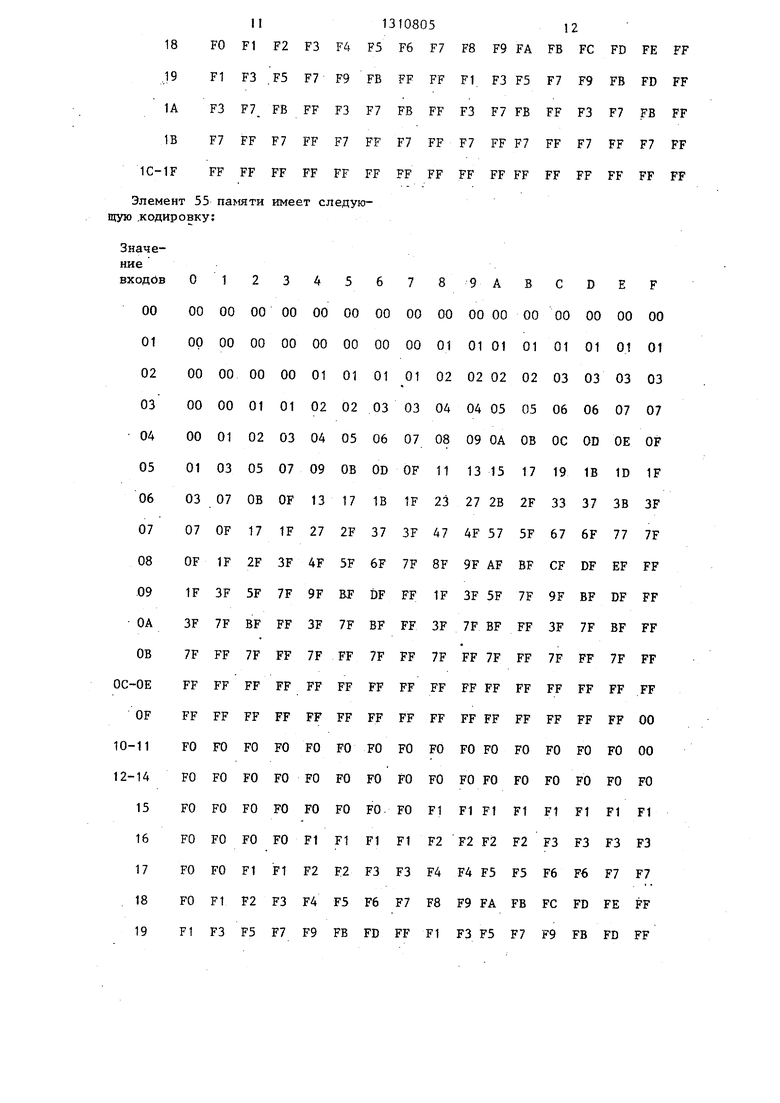

13 13J080514

1А F3 F7 Fb FF F3 F7 FB FF F3 F7 FB FF F3 F7 FB FF

IB F7 FF F7 FF F7 FF F7 FF F7 FF F7 FF F7 FF F7 FF

1A-1E FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

IF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF 00

Элемент 56 памяти имеет следующую кодировку:

Значениевходов О 1 23456 789ABCDEF

0FF FF FF FF 00 FF FF FF FF FF FF 00 FF FF FF FF

1FF FF FF FF FF FF FF FF FF FF FF FF FF. FF FF FF

Элемент 57 памяти имеет следующую кодировку:

Значение.входов 0123456789ABCDEF

000 FO 00 FO FF FF FF FF FF FF 00 FO FF FF FF FF

1FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

30 Элемент 70 памяти имеет следующую

кодировку:

Значениевходов 0123456789ABCDEF

000 00 00 00 08 08 08 08 2А 2В 2В 2В AD AD AD AD

1BF BF BF BF F1 F1 F1 F1 С2 С2 С2 С2 04 04 04 04

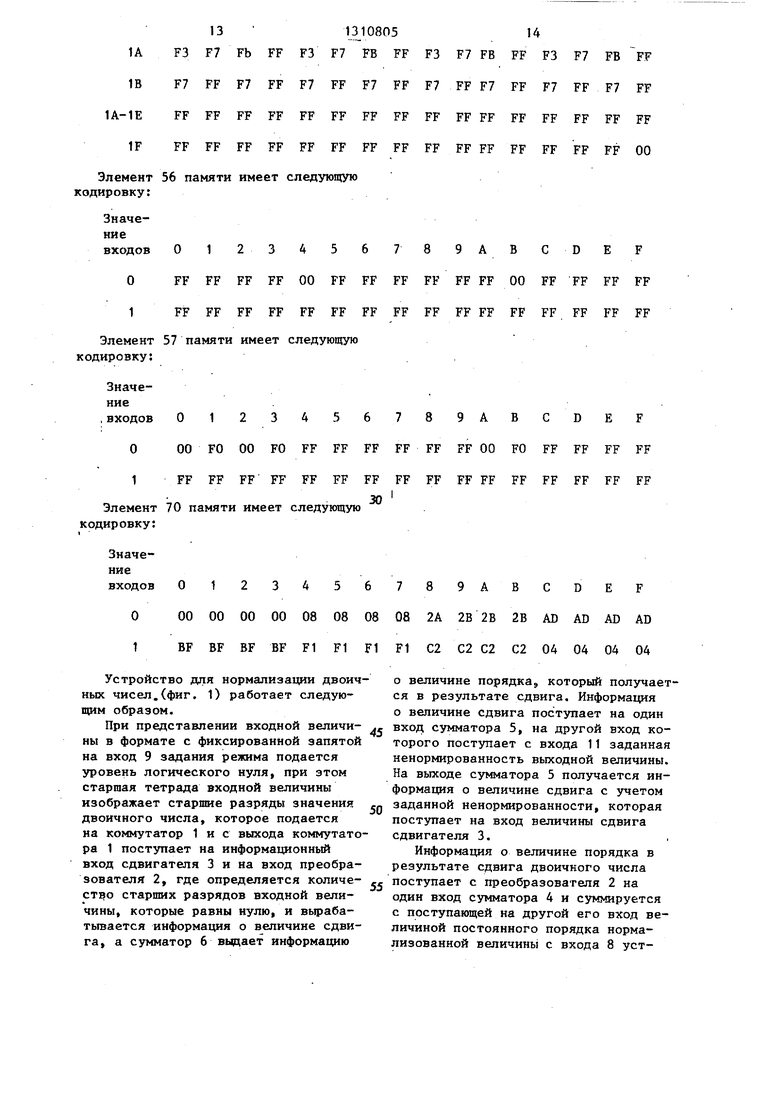

Устройство для нормализации двоич-о величине порядка, который получаетных чисел.(фиг. 1) работает следую-ся в результате сдвига. Информация

щим образом.о величине сдвига поступает на один

При представлении входной величи- вход сумматора 5, на другой вход коны в формате с фиксированной запятойторого поступает с входа 11 заданная на вход 9 задания режима подаетсяненормированность выходной величины, уровень логического нуля, при этомНа выходе сумматора 5 получается ин- старшая тетрада входной величиныформация о величине сдвига с учетом изображает старшие разряды значения заданной ненормированности, которая двоичного числа, которое подаетсяпоступает на вход величины сдвига на коммутатор 1 и с выхода коммутато-сдвигателя 3.

ра 1 поступает на информационный Информация о величине порядка в вход сдвигателя 3 и на вход преобра-результате сдвига двоичного числа зователя 2, где определяется количе- „поступает с щэеобразователя 2 на ство старших разрядов входной вели-один вход сумматора 4 и суммируется чины, которые равны нулю, и выраба-с поступающей на другой его вход ве- тьгаается информация о величине сдви-личиной постоянного порядка норма- га, а сумматор 6 выдает информациюлизованной величины с входа 8 устfO

15

15 131 0805

ройства. На выходе 13 формируется полный порядок двоичного числа после нормализации.

Сдвигатель 3 в зависимости от управляющих величин на его управляющих входах сдвигает поступающее на его информационный вход двоичное число в ту или иную сторону, и на выходе 12 формируется мантисса нормализованного двоичного числа.

При представлении входной величины в формате с плавающей запятой на вход 9 задания режима подается уровень логической единицы, при этом старшая тетрада входной величины изображает ее порядок, а остальные тетрады - мантиссу. Это двоичное чис ло через коммутатор 1 и блок 7 элементов И поступает на преобразователь 2. Дальнейшая работа устройства аналогична его работе при первом режиме, а порядок выходной нормализованной величины получается путем алгебраического суммирования порядка входной величины (старшая тетрада двоичного числа), поступающего с блока 7 элементов И, с величиной порядка, определенной вследствие нормализации на сумматоре 6, выходная величина которого суммируется с постоянным порядком входной величины с входа 8 устройства сумматором 4 порядков, в результате чего получается полный порядок нормализованного двоичного числа.

Выходная величина устройства для нормализации двоичных чисел также может быть представлена в двух формах: с фиксированной и плавающей запятой. При наличии на входе 10 задания режима сигнала логического нуля старшая тетрада выходной величины .выхода 12 устройства изображает старшие разряды нормализованного числа.

6

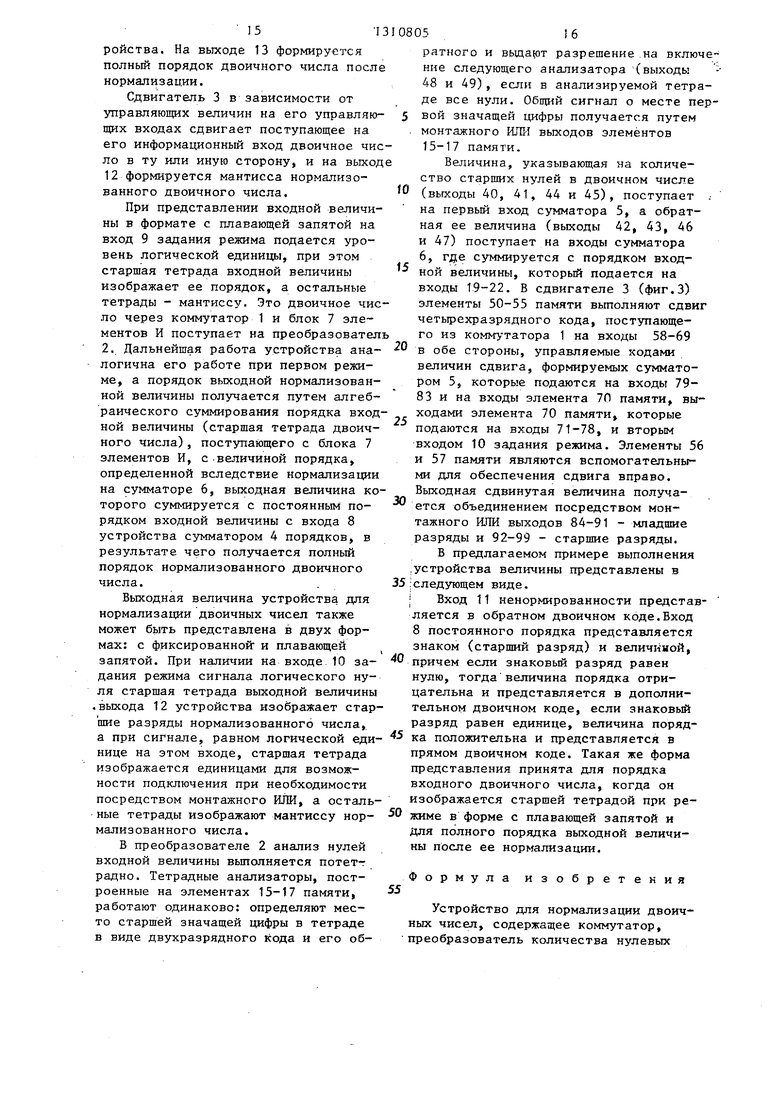

ратного и разрешение .на вклю ние следующего анализатора ч выходы 48 и 49), если в анализируемой тетр де все нули. Общий сигнал о месте п вой значащей цифры получается путем монтажного ИЛЯ выходов элементов 15-17 памяти.

Величина, указывающая на количество старших нулей в двоичном числе (выходы 40, 41, 44 и 45), поступает на первый вход сумматора 5, а обратная ее величина (выходы 42, 43, 46 и 47) поступает на входы сумматора 6, где суммируется с порядком входной величины, который подается на

20

25

входы 19-22. В сдвигателе 3 (фиг.З) элементы 50-55 памяти вьтолняют сдви четьфехразрядного кода, поступающего из коммутатора 1 на входы 58-69 в обе стороны, управляемые кодами величин сдвига, формируемых сумматором 5, которые подаются на входы 79- 83 и на входы элемента 70 памяти, вы ходами элемента 70 памяти, которые подаются на входы 71-78, и вторьм входом 10 задания режима. Элементы 5 и 57 памяти являются вспомогательными для обеспечения сдвига вправо. Выходная сдвинутая величина получается объединением посредством монтажного ИЛИ выходов 84-91 - младшие разряды и 92-99 - старшие разряды.

В предлагаемом примере выполнения .устройства величины представлены в 35 . следующем виде.

i Вход 11 ненормированности предста ляется в обратном двоичном коде.Вход 8 постоянного порядка представляется знаком (старший разряд) и величиной, причем если знаковый разряд равен нулю, тогда величина порядка отрицательна и представляется в дополнительном двоичном коде, если знаковый разряд равен единице, величина поряд

30

40

а при сигнале, равном логической еди- ка положительна и представляется в нице на этом входе, старшая тетрада прямом двоичном коде. Такая же форма изображается единицами для возможности подключения при необходимости

представления принята для порядка входного двоичного числа, когда он изображается старшей тетрадой при репосредством монтажного ИЛИ, а остальпредставления принята для порядка входного двоичного числа, когда он изображается старшей тетрадой при р

ные тетрады изображают мантиссу нор- О жиме в форме с плавающей запятой и

мализованного числа.

В преобразователе 2 анализ нулей входной величины выполняется потетг радно. Тетрадные анализаторы, построенные на элементах 15-17 памяти, работают одинаково: определяют место старшей значащей цифры в тетраде в виде двухразрядного кода и его об

5

6

ратного и разрешение .на включение следующего анализатора ч выходы - 48 и 49), если в анализируемой тетраде все нули. Общий сигнал о месте первой значащей цифры получается путем монтажного ИЛЯ выходов элементов 15-17 памяти.

Величина, указывающая на количество старших нулей в двоичном числе (выходы 40, 41, 44 и 45), поступает на первый вход сумматора 5, а обратная ее величина (выходы 42, 43, 46 и 47) поступает на входы сумматора 6, где суммируется с порядком входной величины, который подается на

0

5

входы 19-22. В сдвигателе 3 (фиг.З) элементы 50-55 памяти вьтолняют сдвиг четьфехразрядного кода, поступающего из коммутатора 1 на входы 58-69 в обе стороны, управляемые кодами величин сдвига, формируемых сумматором 5, которые подаются на входы 79- 83 и на входы элемента 70 памяти, выходами элемента 70 памяти, которые подаются на входы 71-78, и вторьм входом 10 задания режима. Элементы 56 и 57 памяти являются вспомогательными для обеспечения сдвига вправо. Выходная сдвинутая величина получается объединением посредством монтажного ИЛИ выходов 84-91 - младшие разряды и 92-99 - старшие разряды.

В предлагаемом примере выполнения .устройства величины представлены в 5 . следующем виде.

i Вход 11 ненормированности представляется в обратном двоичном коде.Вход 8 постоянного порядка представляется знаком (старший разряд) и величиной, причем если знаковый разряд равен нулю, тогда величина порядка отрицательна и представляется в дополнительном двоичном коде, если знаковый разряд равен единице, величина поряд0

0

ка положительна и представляется в прямом двоичном коде. Такая же форма

ка положительна и представляется в прямом двоичном коде. Такая же форма

представления принята для порядка входного двоичного числа, когда он изображается старшей тетрадой при ре55

Для полного порядка выходной величины после ее нормализации.

Формула изобретения

Устройство для нормализации двоичных чисел, содержащее коммутатор, преобразователь количества нулевых

1713

старших разрядов в двоичный код, сум матор нормализации, сдвигатель и блок элементов И, причем входы мантиссы и порядка операнда устройства соединены соответственно с первым информационным входом коммутатора и первым входом блока элементов И второй вход которого соединен с управляющим входом коммутатора и с первьм входом задания режима устройства, вход операнда которого соединен с вторым информационным входом коммутатора, выход которого соединен с информационным входом сдвигателя и с входом преобразователя количества нулевых старших разрядов в двоичный код, инверсный выход которого соединен с в входом первого слагаемого сумматора нормализации, вход второго слагаемого которого соединен с выходом, блока элементов И, выход сдвигателя является выходом результата устройства,

18

о

тличающееся тем, чтор с целью повышения быстродействия, оно содержит сумматор порядков и сумматор ненормированности, причем выход сумматора нормализации соединен с входом первого слагаемого сумматора порядков, вход второго слагаемого и выход которого соединены соответственно с входом постоянного порядка устройства и с выходом постоянного порядка устройства, прямой выход преобразователя количества нулевых старших разрядов в двоичный код соединен с входом первого слагаемого сумматора ненормированности, вход второго слагаемого и выход которого соединены соответственно с входом ненормированности устройстйа и входом величины сдвига сдвигателя, вход задания режима работы которого соединен с лторым входом задания режим устройства.

Составитель А.Клюев Редактор Е.Копча Техред Н.Глущенко

Заказ 2350 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор, М.Демчик

Изобретение относится к вычислительной технике и может быть использовано при создании высокопроизводительных вьгаислительных устройств, Цель изобретения - повышение быстродействия. Цоставленная цель достигается тем, что устройство для нормализации двоичных чисел, содержащее коммутатор 1, преобразователь 2 количества нулевых старпшх разрядов в двоичный код, сдвигатель 3, сумматор 6 нормализации, блок 7 элементов И, содержит сумматор 4 порядков и сумматор 5 ненормированности с соответствующими связями. 3 ил. 70 1 (Л с -ll Г2 со О СХ) о СП Ж к 8 б jrl OMff.i

| Устройство для нормализации двоичных чисел | 1982 |

|

SU1056181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| М., 1977, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1987-05-15—Публикация

1985-10-17—Подача